Fターム[5F110QQ21]の内容

Fターム[5F110QQ21]の下位に属するFターム

Fターム[5F110QQ21]に分類される特許

81 - 90 / 90

半導体装置およびその製造方法

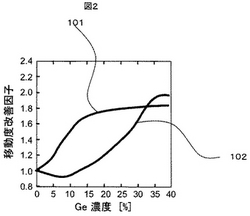

【課題】高周波電力増幅用電界効果型半導体装置において、耐圧を確保しながらの小型化と高効率化の両立が困難になる。

【解決手段】高周波電力増幅用出力段LDMOSに、歪Siチャネルを用いることで更なる効率向上を実現する。更に、チャネル領域を有する歪Si層の膜厚、欠陥の不活性化、或いはフィールドプレート構造の最適化などによってリーク電流を低減しつつ最大限に効率を高める。

(もっと読む)

配線の作製方法

スピン塗布によりレジストの被膜を形成する場合、無駄となってしまうレジスト材料が存在し、さらに、必要に応じて端面洗浄の工程が増えてしまう。また、真空装置を用いて、基板上に薄膜を成膜する際には、チャンバー内を真空にする特別な装置や設備が必要で、製造コストが高くなってしまう。本発明は、絶縁表面を有する基板上に、CVD法、蒸着法又はスパッタ法により選択的に導電層を形成するステップと、前記導電層に接するように、組成物を吐出してレジストマスクを形成するステップと、前記レジストマスクを用いて、大気圧又は大気圧近傍下で、プラズマ発生手段により前記導電層をエッチングするステップと、大気圧又は大気圧近傍下で、前記プラズマ発生手段により前記レジストマスクをアッシングするステップを有することを特徴とする。上記特徴により、材料の利用効率を向上させて、製造コストの低減を実現する。  (もっと読む)

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】 同一基板上に形成されるn型薄膜トランジスタとp型薄膜トランジスタにおいて、水素化の際に半導体層に注入される水素量をn型薄膜トランジスタとp型薄膜トランジスタとで独立に制御可能とし、両薄膜トランジスタの特性を同時に高める。

【解決手段】 nチャネル型薄膜トランジスタ11aのソース・ドレイン領域16aとpチャネル型薄膜トランジスタ11bのソース・ドレイン領域16bとが隣接して形成される共に、ソース・ドレイン領域16a,16bに重なるように形成されたコンタクトホール19bによりnチャネル型薄膜トランジスタ11aとpチャネル型薄膜トランジスタ11bとでコンタクトホール19bを共通化した薄膜トランジスタ基板1において、隣接して形成された前記ソース・ドレイン領域16a,16b上の前記ゲート絶縁層14の膜厚が、前記nチャネル型薄膜トランジスタ11aと前記pチャネル型薄膜トランジスタ11bとで異なる。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、微細な形状を有する半導体領域の形成方法を提供する。バラツキの少ない半導体装置の作製方法を提供する。また、少ない原料でコスト削減が可能であり、且つ歩留まりが高い半導体装置の作製方法を提供する。

【解決手段】 本発明は、半導体膜の一部にレーザ光を照射し、絶縁層を形成した後、該絶縁層をマスクとして半導体膜をエッチングして、所望の形状を有する半導体領域を形成した後、該半導体領域を用いる半導体装置を作製する。本発明では、公知のレジストを用いたフォトリソグラフィー工程を用いずとも、所定の場所に微細な形状を有する半導体領域を形成することが可能である。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】半導体装置の基体層に対し、剥離層を確実に形成すると共に、水素のイオン注入を容易に制御できるようにする。

【解決手段】半導体装置Sの製造方法は、活性領域30が形成された複数の第1領域R1と、各第1領域R1同士の間に設けられた第2領域R2とを有する基体層1を備えた半導体装置Sの製造方法であって、活性領域30を覆うゲート酸化膜7の表面と高さが同じようになるように第2領域R2に素子分離用絶縁膜5を形成する素子分離用絶縁膜形成工程と、素子分離用絶縁膜形成工程の後に、基体層1に水素をイオン注入して剥離層を形成する剥離層形成工程と、剥離層に沿って基体層1の一部を分離する分離工程とを備えている。

(もっと読む)

半導体装置およびその作製方法

【課題】 従来のパルス発振のレーザー光による照射を半導体膜に行った場合、半導体表面にリッジと呼ばれる凹凸が形成され、トップゲート型TFTの場合には、素子特性がリッジにより大きく左右されていた。特に、電気的に並列に接続する複数の薄膜トランジスタ間でのバラツキが問題となっている。

【解決手段】 本発明は、複数の薄膜トランジスタからなる回路の作製において、連続発振レーザを用いて半導体膜にレーザ光を照射して溶融する領域の幅LP(微結晶領域を含まない)を大きくし、一つの領域に複数の薄膜トランジスタ(電気的に並列に連結された薄膜トランジスタ)の活性層を配置することを特徴の一つとする。

(もっと読む)

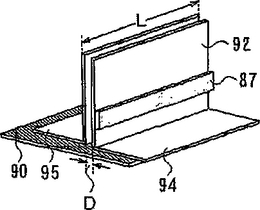

電気光学装置及び電子機器

【課題】電気光学装置において、画素電極及びデータ線間に生じる容量カップリングの影響を極力排除するとともに、TFTの長期寿命化を図り、更には、積層構造を構成する各要素間の電気的接続を良好に実現することによって、より高品質な画像を表示する。

【解決手段】基板上に、データ線(6a)、走査線(3a)、画素電極(9a)及びTFT(30)が積層構造の一部をなして備えられている。この基板上には更に、TFT及び画素電極に電気的に接続された蓄積容量(70)と、データ線及び画素電極間に配置されたシールド層(400)と、前記画素電極の下地として配置された層間絶縁膜(43)とが、前記積層構造の一部をなして備えられている。このうちシールド層は略三角形の部分が設けられ、前記略三角形の部分も含めて窒化膜を含む。

(もっと読む)

半導体装置およびその作製方法

【課題】 高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつ液晶表示装置を提供する。

【解決手段】 ゲート電極106と異なる層に走査線102を形成し、容量配線107が信号線109と平行になるよう配置する。各画素はそれぞれ独立した容量配線107に誘電体を介して接続されているため隣接画素の書き込み電流による容量配線電位の変動を回避でき、良好な表示画像を得る事ができる。

(もっと読む)

半導体基板の製造方法、及び半導体基板

【課題】剥離用物質を注入して半導体層を薄膜化すると共に、半導体デバイス部に対する剥離用物質による悪影響を排除する。

【解決手段】半導体装置Sの製造方法は、半導体層20の表面に絶縁層であるゲート酸化膜4を形成する絶縁層形成工程と、半導体層20に対し、半導体層における上記剥離用物質の移動を抑止するためのホウ素イオンを注入し、該半導体層20に拡散抑止層35を形成する拡散抑止層形成工程と、拡散抑止層35のホウ素を加熱して活性化させる活性化工程と、半導体層20に水素イオンを注入し、半導体層20の領域のうち拡散抑止層35を介してゲート酸化膜4と反対側の領域に剥離層36を形成する剥離層形成工程と、半導体層20のゲート酸化膜4側にガラス基板18を貼り合わせる貼り合わせ工程と、半導体層20を熱処理することにより、半導体層20を剥離層36に沿って分割する分割工程とを備えている。

(もっと読む)

D/A変換回路及び半導体装置

【課題】 高いビット数のデジタル信号に対応し、線形性が良く、占有面積の小さいD/A変換回路を提供する。

【解決手段】 複数の容量を有するD/A変換回路であって、複数の容量は、第1電極と、第1電極に接している第1誘電体と、第1誘電体に接している第2電極と、第2電極に接している第2誘電体と、第2誘電体に接している第3電極とをそれぞれ有しており、第2電極は、第1電極及び第3電極と重なっており、第2電極は、第1電極及び第3電極と重なっている部分において開口部を有しており、第2電極が有する開口部において、第1誘電体及び第2誘電体にコンタクトホールが形成されており、コンタクトホールを介して第1電極と第3電極が接続されていることを特徴とするD/A変換回路。

(もっと読む)

81 - 90 / 90

[ Back to top ]