Fターム[5F110QQ21]の内容

Fターム[5F110QQ21]の下位に属するFターム

Fターム[5F110QQ21]に分類される特許

21 - 40 / 90

半導体装置及びその作製方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極の上に設けられたゲート絶縁膜と、ゲート絶縁膜

の上に設けられソース領域及びドレイン領域を含む半導体膜と、ソース領域又はドレイン

領域に電気的に接続する配線又は電極と、配線又は電極の上に設けられ第1の開口部を有

する第1の絶縁膜と、第1の絶縁膜の上に設けられ第2の開口部を有する第2の絶縁膜と

、第2の絶縁膜の上に設けられた画素電極とを有し、第1の絶縁膜は窒化シリコン膜を含

む積層の無機絶縁膜からなり、第2の絶縁膜は有機樹脂膜からなり、第2の絶縁膜の第2

の開口部の底面において、第1の絶縁膜の上面は第2の絶縁膜に覆われていない露呈した

部分を有し、第2の絶縁膜の第2の開口部の断面において、第2の絶縁膜の内壁面は凸状

の曲面を有しており、画素電極は、第1の開口部及び第2の開口部を介して配線又は電極

に電気的に接続されている。

(もっと読む)

電気光学装置、電気光学装置の製造方法、電子機器

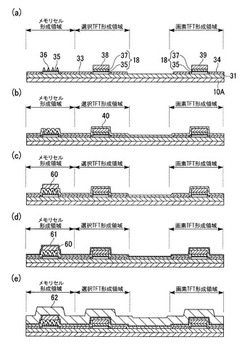

【課題】不揮発性メモリと画素TFTとを同一基板上に形成でき、且つ両者を良好に動作させることが可能な電気光学装置を提供する。

【解決手段】画素TFTのゲート絶縁膜18を不揮発性メモリのトンネル絶縁膜(第1の絶縁膜)35と、トンネル絶縁膜35よりも膜厚の大きい第2の絶縁膜37によって構成する。また、フローティングゲート電極36のコントロールゲート電極60側の面を凹凸とし、該凹凸によってフローティングゲート電極36の表面積を拡げる。これにより、フローティングゲート電極36とコントロールゲート電極60との間の容量を、フローティングゲート電極36と半導体層33との間の容量よりも大きくする。

(もっと読む)

薄膜トランジスタの製造方法

【課題】小粒径の多結晶シリコン層と、大粒径の多結晶シリコン層を同時に作る手法として、シリコン層の堆積時に小粒径の多結晶シリコン層を形成し、所望の領域のみにCWレーザーを照射し大粒径化する技術が知られている。しかし、この技術を用いる場合、小粒径の多結晶シリコン層中に不対電子を埋める水素を残しての処理が必要となり、製造工程にかかる時間が長くなるという課題がある。

【解決手段】一部に金属層311がある基板310上に窒化珪素層312を形成し、窒化珪素層312上に、酸化珪素層313を形成し、パルスレーザーを照射する。酸化珪素層313の層厚により小粒径の多結晶シリコン層と大粒径の多結晶シリコン層とが入れ替わるように形成されるため、小粒径の多結晶シリコン層と、大粒径の多結晶シリコン層を同時に形成することが可能となる。

(もっと読む)

表示装置

【課題】光源側にゲート電極膜を有するTFTを複数個直列に設ける場合、光リーク電流の発生を抑えつつ、容量増加をも抑制することができる表示装置を提供することにある。

【解決手段】複数個あるTFTの少なくとも一部について、半導体膜とゲート電極膜が対向する面積のチャネル領域に対する相対的な面積が異なることにより、光リーク電流の発生を抑えつつ、容量増加を抑制する構造の平面ディスプレイを提供する。

(もっと読む)

表示装置

【課題】光源側にゲート電極膜を有するTFTを複数個直列に設ける場合、光リーク電流の発生を抑えつつ、容量増加をも抑制することができる表示装置を提供することにある。

【解決手段】直列に設けれた複数個のチャネル領域のチャネル端のうち、映像信号線側及び画素電極側の最も近くに位置するチャネル端の外側に、対向するゲート端が位置し、当該チャネル端以外のチャネル端のうち少なくとも一つにおいて、チャネル端がゲート端のより近くに位置している。

(もっと読む)

酸化ゲルマニウムの製造方法およびそれを用いた半導体デバイスの製造方法

【課題】熱的および化学的に安定な酸化ゲルマニウムの製造方法を提供する。

【解決手段】p型Geからなる基板1は、純水および0.1%HFによって洗浄され、その後、超純水によってリンスされる(工程(a)参照)。その後、基板1は、33%の過酸化水素水3に、60秒間、浸漬される(工程(b)参照)。これによって、酸化ゲルマニウム膜4が基板1の一主面に形成される。

(もっと読む)

半導体装置

【課題】 LDD形成工程に於けるプラズマプロセスが原因となり生じる素子の

損傷を極力低減した半導体装置の作製方法を提供すること。

【解決手段】 基板全面を覆うように導電性膜を形成した状態で、ハードマスク

を利用した半導体装置の作製方法でLDD構造の素子を形成することにより、L

DD形成工程におけるプラズマプロセスによる素子への損傷を極力低減する。導

電性膜が全面に形成されていることにより、異方性エッチング等のプラズマによ

る処理(プラズマプロセス)においてゲート電極に蓄積される電荷密度を低減で

き、プラズマプロセスによる損傷を低減できる。

(もっと読む)

薄膜トランジスタの製造方法および薄膜トランジスタ

【課題】光照射による活性化処理を行ったとしても、ホットキャリア信頼性が損なわれることがない薄膜トランジスタおよびその製造方法を提供すること。

【解決手段】基板上に島状半導体層を形成する工程、前記島状半導体層上にゲート絶縁膜を形成する工程、光を照射して、前記島状半導体層とゲート絶縁膜との界面に焼締め処理を施す工程、前記ゲート絶縁膜上にゲート電極を形成する工程、前記島状半導体層に不純物を注入し、所定の間隔を隔てて第1の不純物領域及び第2の不純物領域を形成する工程、及び前記島状半導体層に光を照射し、前記第1の不純物領域及び第2の不純物領域中の不純物を活性化する工程を具備することを特徴とする。

(もっと読む)

表示装置の作製方法及び電子書籍の作製方法

【課題】樹脂基板等の可撓性を有する基板を用いて、柔軟性を有する表示装置を作製するための技術を提供する。

【解決手段】固定基板上に、剥離層となる非晶質シリコン膜を介して樹脂基板を形成する工程と、前記樹脂基板上に少なくともTFT素子を形成する工程と、前記非晶質シリコン膜にレーザー光を照射することにより、前記非晶質シリコン膜において前記固定基板から前記樹脂基板を剥離する工程とを行い、前記樹脂基板を用いた柔軟性を有する表示装置を作製する。

(もっと読む)

薄膜トランジスタ基板、その製造方法及び表示装置

【課題】静電気による帯電を防止し、素子破壊による不良発生を低減させることができる薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】薄膜トランジスタ基板1を製造する各処理工程に長尺プラスチック基板10をロール・ツー・ロールで供給、巻き取りを行いながらその長尺プラスチック基板10の一方の面S1に薄膜トランジスタ50を形成する薄膜トランジスタ基板1の製造方法であって、少なくとも長尺プラスチック基板10の一方の面S1に薄膜トランジスタ50を形成する前に、長尺プラスチック基板10の他方の面S2の全面に導電膜2を形成する。

(もっと読む)

半導体装置の作製方法

【課題】半導体集積回路に用いる絶縁膜として、膜厚が薄くとも信頼性を確保することができる絶縁膜の作製方法を提供することを課題とする。特に、ガラス等の大面積化が可能な絶縁表面を有する基板上に低い基板温度で高品質の絶縁膜を提供することを課題とする。

【解決手段】チャンバーにモノシランガス(SiH4)と亜酸化窒素(N2O)と希ガスを導入し、10Pa〜30Paの圧力下で高密度プラズマを発生させてガラス等の絶縁表面を有する基板上に絶縁膜を形成する。その後、モノシランガスの供給を停止し、大気に曝すことなく亜酸化窒素(N2O)と希ガスとを導入して絶縁膜表面にプラズマ処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】薄膜トランジスタを含む半導体装置を歩留まりよく製造するためのアライメントマークを、工程増となることなく、歩留まりと精度のよい半導体装置、及びその製造方法を提供する。

【解決手段】多結晶シリコン半導体膜13と、少なくとも表面が異なるシリコン相6a,6bで図形化されたシリコン膜5からなるアライメントマーク4と、が基板10上に形成されている半導体装置1によって、上記課題を解決する。この異なるシリコン相6a,6bは、多結晶シリコン相6pと非晶質シリコン相6aである。こうした異なるシリコン相6a,6pは、半導体素子部2に多結晶シリコン半導体膜13を形成するためのマスクパターンAを形成するとともに、アライメントマーク部3にアライメントマーク4を形成するためのマスクパターンBを形成し、そのマスクパターンA,B上からイオン注入して、マスクパターンA,Bで覆われていない多結晶シリコン膜の露出部の少なくとも表面を非晶質シリコン相に変化させることによって形成できる。

(もっと読む)

電気光学装置、電子機器、電気光学装置の製造方法

【課題】不揮発性メモリと画素TFTが同一基板上に併設されており、かつ高信頼性とされた液晶装置を提供する。

【解決手段】本発明の電気光学装置は、画素部と、これを駆動させる駆動回路と、不揮発性メモリと、を備えた電気光学装置である。画素部及び前記駆動回路の少なくとも一方におけるスイッチング素子は、不揮発性メモリとともに基板10A上に形成されている。スイッチング素子のゲート絶縁膜は、第1絶縁膜35と第2絶縁膜36と第3絶縁膜38との積層構造からなっており、不揮発性メモリは、第2絶縁膜36を介して半導体層33上に設けられたフローティングゲート電極37と、第3絶縁膜38を介してフローティングゲート電極37上に設けられたコントロールゲート電極39Aと、を有するメモリセル110aを備えている。

(もっと読む)

ゲート絶縁膜、薄膜トランジスタ基板及びその製造方法

【課題】薄膜トランジスタが有する特性のよいゲート絶縁膜、及びそのゲート絶縁膜を有する薄膜トランジスタ基板及びその製造方法を提供する。

【解決手段】シリコン薄膜トランジスタ基板が有する酸化ケイ素からなるゲート絶縁膜であって、ゲート電圧を正電圧から負電圧に掃引したとき、ゲート電極からゲート絶縁膜中に流れ込むゲートリーク電流の値が正から負に変わる時のゲート電圧値と、ゲート電圧を負電圧から正電圧に掃引したとき、ゲート電極からゲート絶縁膜中に流れ込むゲートリーク電流の値が負から正に変わる時のゲート電圧値との差ΔV(V)が、ゲート絶縁膜の厚さd(nm)との関係で、[ΔV/d]<0.0045であるように構成する。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】トランジスタとしての移動度が高く、ゲート絶縁膜の界面準位密度が低い薄膜トランジスタ基板を低コストで製造することができる薄膜トランジスタ基板の製造方法を提供する。

【解決手段】少なくとも、基板上にシリコン半導体膜を形成する工程と、酸化ケイ素からなるゲート絶縁膜を形成する工程と、ゲート電極を形成する工程とをその順で有するトップゲート型の薄膜トランジスタ基板の製造方法であって、前記ゲート電極の形成工程後に、300℃未満の高圧水蒸気処理工程を設ける。この高圧水蒸気処理工程を、100℃を超え300℃未満の温度と1気圧を超え飽和蒸気圧以下の圧力とからなる雰囲気下で行うこと、又は、150℃〜200℃の温度と飽和蒸気圧とからなる雰囲気下で行うことが好ましい。

(もっと読む)

半導体装置、およびその作製方法

【課題】ばらつきを抑え、かつ、製造歩留まりの高い半導体装置を作製することを課題とする。

【解決手段】

絶縁表面を有する基板上に、チャネル形成領域が非単結晶半導体層で形成される薄膜トランジスタを有し、前記非単結晶半導体層は、厚さが5nm以上50nm以下であり、一方向に略平行に延びる結晶粒界を含み、該結晶粒界の間隔は10nm以上、500nm以下であることを特徴とする、半導体装置及びその作製方法を提供する。

(もっと読む)

半導体層とこの半導体層を用いた半導体装置および表示装置

【課題】水素終端化された高品質な多結晶Si膜を含む半導体薄膜を低温、高速成膜することで、良好な特性のTFTを安定して実現し、高品質、高画質の半導体装置および表示装置を提供する。

【解決手段】絶縁性基板上に形成したSi、Ge、F、Hを含有する半導体層4を、良好な結晶性が得られる反応熱CVD法で形成した多結晶SiGe膜または多結晶Si膜を第一層4aとその上層の第二層4bとの複数層の連続成膜で積層構造に構成し、該半導体層4中のH濃度を絶縁性基板1側に対して表面側にある第二層4bで高くした。

(もっと読む)

表示装置

【課題】サイズが小さく、耐圧の高い薄膜トランジスタにより構成された保護回路を有する表示装置を提供する。

【解決手段】表示装置の保護回路において、非晶質半導体層と、微結晶半導体層と、該微結晶半導体層に接するゲート絶縁層と、ゲート電極層と、が重畳する薄膜トランジスタを用いる。微結晶半導体層の電流駆動能力が高いため、トランジスタのサイズを小さくすることができる。また、非晶質半導体層を有することで耐圧を向上させることができる。ここで表示装置とは、液晶表示装置又は発光装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】本発明は、比較的低温(600℃未満)のプロセスで作製される素子をガラス基板から分離(すなわち、剥離)し、可撓性基板(代表的にはプラスチックフィルム)に配置(すなわち、転置)する技術を開示する。

【解決手段】ガラス基板上にプラズマCVD法を用いてハロゲン元素を含む剥離層を形成し、その剥離層上に半導体素子を形成した後、剥離層の層内または界面で剥離を行って、大面積のガラス基板と半導体素子とを分離する。また、ガラス基板と剥離層との界面で分離させるために、剥離層においてハロゲン元素の濃度勾配を持たせてもよく、剥離層におけるガラス基板との界面近傍にハロゲン元素を他の箇所より多く含ませる。

(もっと読む)

半導体装置の作製方法及び電子機器

【課題】レーザ光照射による処理で高品質なシリサイド膜を形成し、絶縁基板に形成された電気的特性のばらつきの小さい電界効果型トランジスタの微細化と高性能化を実現する。

【解決手段】絶縁基板上に形成された一対の不純物領域及びチャネル形成領域を有する島状の半導体膜において、一対の不純物領域上に第1の金属膜を形成し、ゲート絶縁膜を介してチャネル形成領域上に位置するゲート電極上に反射膜として機能する第2の金属膜を形成する。第1の金属膜にレーザ光を照射して、第2の金属膜が形成された領域においてレーザ光を反射させ、且つ、一対の不純物領域において選択的に島状の半導体膜と第1の金属膜とを反応させる。

(もっと読む)

21 - 40 / 90

[ Back to top ]