Fターム[5F140AA01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 周波数特性 (832)

Fターム[5F140AA01]に分類される特許

201 - 220 / 832

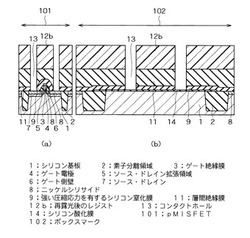

半導体装置及びその製造方法

【課題】強い圧縮応力を有するシリコン窒化膜を用いたpMISFETを有する半導体装置及びその製造方法において、歩留まりが高く且つスイッチングスピードが高い半導体装置及びその製造方法を提供する。

【解決手段】ボックスマーク102内においてシリコン基板1を覆うようにシリコン酸化膜14を形成する。次に、基板上の半導体領域にシリサイド化反応によりニッケルシリサイド8を形成する。その後、強い圧縮応力を有するシリコン窒化膜9をpMISFET101及びボックスマーク102を覆うように形成する。その上に層間絶縁膜11を形成した後レジストをパターニングしてコンタクトホール13を形成する。この際、重ね合わせ精度が所定の規格を満たすまで、レジストを一旦除去し再度レジスト12bを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISのソース・ドレイン領域端部における転位の発生および拡散抵抗の上昇を防止する。

【解決手段】CMISにおけるソース・ドレイン領域12、14の形成時、シリコン基板1に不純物をイオン注入する前に、Pウエル層4には転位抑制元素としてアルゴンを打ち込み、かつNウエル層5には窒素を転位抑制元素として打ち込む。これにより転位の発生を抑制しつつ、かつ、Pウエル層4とNウエル層5それぞれに適した転移抑制元素を打ち分けることで拡散抵抗の上昇を抑制し、歩留まりを向上させ、素子の信頼性を高めることができる。

(もっと読む)

新構造半導体集積回路

【課題】現在、半導体集積回路で使用されているバイポーラトランジスタとMOSトランジスタは最初に発明された時よりその構造は変わっておりません。構造と原理を根本的に見直し、高速化・低消費電力化・微細化を進展させる。

【解決手段】サブミクロンスケールの微細加工技術を用い、新しい原理と構造のトランジスタによる半導体集積回路を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電層が基板の内部深くにまで達することを回避して、浅いソース・ドレイン領域を形成することを可能とし、微細化に適した半導体装置及びその製造方法を得る。

【解決手段】シリコン基板1の上面内にエクステンション5を形成した後、シリコン酸化膜30を全面に堆積し、シリコン酸化膜30上にシリコン窒化膜31を、シリコン窒化膜31上にシリコン酸化膜32をそれぞれ堆積し、シリコン酸化膜32、シリコン窒化膜31及びシリコン酸化膜30をこの順にエッチングしてサイドウォール36を形成する。不純物領域13を形成し、シリコン酸化膜に対して選択性を有する条件下でシリコン成長を行うことにより、シリコン成長層15,16,37を形成する。コバルト17を全面に堆積した後、熱処理を行うことにより、コバルトシリサイドを形成する。その後、未反応のコバルト17を除去する。

(もっと読む)

半導体装置

【課題】ソース/ドレインの配線抵抗の上昇を抑制し、ゲート配線の低抵抗化を図る。

【解決手段】もっとも半導体基板10側に位置する第1配線層20は、半導体素子のソース領域15に電気的に接続された第1ソース配線21と、半導体素子のドレイン領域12に電気的に接続された第1ドレイン配線22と、ゲート電極17に電気的に接続された中継部23とを備えている。そして、第1ソース配線21および第1ドレイン配線22にそれぞれ設けられたソース側凹部21aおよびドレイン側凹部22aによって設けられた間隙24にこの中継部23を配置する。

(もっと読む)

半導体装置及びその製造方法

【課題】結晶歪技術を使用した高性能なFETを提供する。

【解決手段】半導体装置1は、チャネル方向に沿って延在する立体構造と、この立体構造の第1の側面に作用する残留応力を有するストレス膜16Saと、この立体構造の第2の側面に形成されたゲート絶縁膜19aと、立体構造をゲート絶縁膜19aを介して被覆するとともに第1および第2の側面が対向する方向に沿って延在するゲート電極10Pと、を備える。立体構造はソース電極13Saとドレイン電極13Daとの間にチャネル領域13Qaを有する。

(もっと読む)

半導体装置

【課題】コンタクトの位置ずれが回路の特性に与える影響を低減した半導体装置を提供する。

【解決手段】この半導体装置は、半導体層10に設けられた素子分離膜20と、素子分離膜20により区画された素子形成領域と、素子形成領域上及び素子分離膜20上を延伸しているゲート配線140と、ゲート配線140の側壁に形成されたサイドウォール150と、素子分離膜20上に位置するゲート配線140に接続するコンタクト200とを備える。ゲート配線140の側壁は、少なくとも上部においてコンタクト200に接触してる領域144を有する。

(もっと読む)

半導体装置

【課題】 従来の構造よりさらに安定した電気的特性を実現しうる横型MOSトランジスタを提供する。

【解決手段】 P型の半導体基板10内において方向d1に延伸するP型のボディ領域15、ボディ領域15と離間して形成されたN型のドレイン領域11、ボディ領域15内に形成された高濃度P型のボディコンタクト領域21及びN型のソース領域16、ドレイン領域11内に形成された高濃度N型のドレインコンタクト領域12、並びにソース領域16とドレインコンタクト領域12の間に形成されたP型の拡散領域13を備え、拡散領域13は、ドレイン領域11内においてボディ領域15と離間した状態で方向d1に延伸して形成される主領域13aと、主領域13a内のボディ領域15と対向する外周端の一または離散した複数の一部領域からボディ領域15に向かう方向にボディ領域15または半導体基板10と連絡する位置まで突出する突出領域13bとを有する。

(もっと読む)

窒化ガリウム系化合物半導体層の形成方法、移設方法、及び窒化ガリウム系化合物半導体層が接合されたシリコン基板

【課題】比較的結晶欠陥の少ない窒化ガリウム系化合物半導体層を比較的低コストで得ることができる技術を提供する。

【解決手段】サファイア基板10上に、SiO2層13を形成し、層13を部分的に除去してサファイア基板の露出部を形成し、露出部を持つサファイア基板上に、非晶質窒化ガリウム系化合物半導体を堆積し、層13上の非晶質窒化ガリウム系化合物半導体を蒸発させ、サファイア基板の露出部上に非晶質窒化ガリウム系化合物半導体の核を形成し、核のサイズ増大、合体、結晶成長、層13上への横方向結晶成長、平坦表面形成などを経て、サファイア基板上に窒化ガリウム系化合物半導体層20を形成し、サファイア基板10の露出部上の窒化ガリウム系化合物半導体層を除去して分離溝25を形成する。サファイア基板上の窒化ガリウム系化合物半導体層20は他の基板に移設される。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

半導体装置

【課題】高周波帯域で高出力動作可能な半導体装置の提供。

【解決手段】半導体装置を、半導体基板12上に形成されたP型Si層13と、絶縁膜を介して設けられたゲート電極3と、ゲート電極3の一方側のP型Si層13内に形成されN型の第1低濃度不純物拡散層44および第1拡散層44より高い不純物濃度を有するN型第2高濃度不純物拡散層45からなるドレイン領域と、第2拡散層45の各辺に対して所定間隔内側に設けられたコンタクトホール53を有する層間絶縁膜9aと、ゲート電極3の他方側のP型Si層13内に形成されN型の高濃度の第3不純物拡散層からなるソース領域41と、素子分離用絶縁膜11と、P型分離拡散層14とを備え、P型分離拡散層14は結晶欠陥を有し、ゲート幅方向の絶縁膜11と第2拡散層45の対向する端部間距離がゲート長方向における第2拡散層45とゲート電極3の対向する端部間の距離より長い。

(もっと読む)

ファセットされたシリサイドコンタクトを有する半導体デバイス及び関連する製造方法

【解決手段】

開示される主題は、半導体トランジスタデバイス及び、従来のシリサイドコンタクトと比較して増大された実効サイズを有するシリサイドコンタクトを形成するために利用することができる関連する製造技術に関する。ここに開示されるプロセスに従って製造される半導体デバイス(200)は、半導体材質(102)の層と、半導体材質(102)の層を覆うゲート構造(112,128)とを含む。チャネル領域(218)が半導体材質(102)の層内に形成され、チャネル領域(218)はゲート構造(112,128)の下層となる。半導体デバイス(200)はまた、半導体材質(102)の層内のソース及びドレイン領域(216)を含み、チャネル領域(218)はソース及びドレイン領域(216)の間に配置される。また、半導体デバイス(200)はソース及びドレイン領域(216)を覆うファセット形状シリサイドコンタクト区域(210,308,406)を含む。

(もっと読む)

トランジスタにおいて進歩したシリサイド形成と組み合わされる凹型のドレイン及びソース区域

【解決手段】

洗練されたトランジスタ要素を形成するための製造プロセスの間、それぞれの金属シリサイド領域を形成するのに先立つ共通のエッチングシーケンスにおいて、ゲート高さが減少させられてよく、そして凹型のドレイン及びソース構造もまた得られてよい。対応する側壁スペーサ構造はエッチングシーケンスの間に維持され得るので、ゲート電極におけるシリサイド化プロセスの可制御性及び均一性を高めることができ、それにより、低減された程度のスレッショルドばらつきを得ることができる。更に、凹型のドレイン及びソース構造が、全体的な直列抵抗の低減及び応力転移効率の増大をもたらすことができる。

(もっと読む)

酸化ゲルマニウムの製造方法およびそれを用いた半導体デバイスの製造方法

【課題】熱的および化学的に安定な酸化ゲルマニウムの製造方法を提供する。

【解決手段】p型Geからなる基板1は、純水および0.1%HFによって洗浄され、その後、超純水によってリンスされる(工程(a)参照)。その後、基板1は、33%の過酸化水素水3に、60秒間、浸漬される(工程(b)参照)。これによって、酸化ゲルマニウム膜4が基板1の一主面に形成される。

(もっと読む)

MIS電界効果トランジスタ及び半導体基板の製造方法

【課題】高温特性を改善した高集積、高速且つ高性能なMISFETを得ること。

【解決手段】半導体基板に絶縁膜を埋め込んだトレンチ素子分離領域を選択的に設け、この絶縁分離された半導体基板上に、半導体基板と同じ第1の半導体を、筒状構造を有して縦方向にエピタキシャル成長させ、この第1の半導体層に自己整合して、格子定数がやや大きい第2の半導体を内側面の横方向にエピタキシャル成長させることにより、第1の半導体層に歪みを加える。この第2の半導体層の上部内側面を除く内側面に接して絶縁膜を設け、この絶縁膜の側面間を空孔となし、この空孔に栓をするように、第2の半導体層の上部内側面間に導電膜を設ける。歪み半導体層の外側面にはゲート絶縁膜を介してゲート電極を設ける。歪み半導体層及び第2の半導体層の上部にはドレイン領域を設け、歪み半導体層及び第2の半導体層の下部且つ半導体基板の表面にはソース領域を設けておき、配線体をそれぞれの領域に接続した縦型のMISFETを構成すること。

(もっと読む)

非シリコンチャネルMOSデバイス中のフェルミレベルピンニングの低減方法

【課題】金属酸化物半導体(MOS)デバイス中の、GeやIII−V化合物(例えばGaAsまたはInGaAs)のような高移動度半導体化合物チャネル中の、フェルミレベルピンニング(FLP)を低減(回避)する方法の提供。

【解決手段】半導体化合物11上のゲート誘電体19上にゲート電極20を形成し、水素アニール21を実施する。水素はゲート電極のPtやPdのような貴金属による触媒作用により原子状水素を形成しアニールを行い半導体化合物11とゲート誘電体19との界面を界面をパッシベートし、更には欠陥を回復する。

(もっと読む)

high−K誘電膜上に金属ゲートを蒸着する方法及び、high−K誘電膜と金属ゲートとの界面を向上させる方法、並びに、基板処理システム

【課題】金属酸化膜半導体電界効果トランジスタ(MOSFET)において、本発明の目的は、high−K誘電膜と金属ゲートとの間の界面特性を向上させることにより、電気的特性およびデバイス性能を向上させることである。

【解決手段】high−K誘電体上に金属ゲートを蒸着することによりMOSFETの製造においてhigh−K誘電膜と金属ゲートとの間の界面を向上させる方法は、熱アニーリングモジュール内で、その上にhigh−K誘電膜が蒸着された基板をアニールするアニーリングステップと、金属ゲート蒸着モジュール内で、前記アニールされた基板上に金属ゲート材料を蒸着させる蒸着ステップとを含み、真空を破ることなく、前記アニーリングステップおよび前記蒸着ステップが連続的に行なわれることを特徴とする。

(もっと読む)

基板全域にわたって高められた均一性を有する埋め込みSi/Ge材質を伴うトランジスタ

【解決手段】

洗練された半導体デバイスにおいては、異なる結晶方位に対して異方性エッチング挙動を有し得るウエット化学的エッチングプロセスに基いてキャビティを形成することによって、チャネル領域の近くに歪誘起半導体合金を位置させることができる。1つの実施形態では、異方性エッチング挙動に加えて二酸化シリコンに関する高いエッチング選択性を呈するTMAHを用いることができ、それにより、チャネル領域からのオフセットを更に減少させる可能性を追加的に提供する一方で、全体的なプロセスばらつきの大きな原因となることのない極めて薄いエッチング停止層が可能になる。

(もっと読む)

半導体装置

【課題】高周波高出力増幅に用いるFETを具えた半導体装置において、交差部に起因の寄生容量を防止し、かつチップ面積を拡大せずに発熱の集中を分散させる。

【解決手段】半導体装置は、ゲート幅方向15に互いに平行にかつ離間して形成されている複数のゲート電極13と、ゲート長方向11に延在して形成されている基線部17と、複数の主電極19とが下地21の上側に設けられている。ゲート電極は、基線部とそれぞれ交差し、かつこの基線部と一体的に形成されている。主電極は、基線部、及び隣り合うゲート電極の間に囲まれた領域に1つずつ配置形成されている

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低減に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11と、前記半導体基板上にゲート絶縁膜12を介して設けられるゲート電極13と、前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるエクステンション領域LDDと、前記エクステンション領域の両側を挟むように前記半導体基板中に設けられ、前記半導体基板とは異なる格子定数有し、前記半導体基板に歪みを付与する歪み付与層22と、前記エクステンション領域の両側の前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるソース/ドレインS/Dと、前記ソース/ドレイン上に設けられるシリサイド層SS/Dとを具備し、前記歪み付与層と前記半導体基板との界面Si-Siは、少なくとも前記シリサイド層の底面の一部に一致する。

(もっと読む)

201 - 220 / 832

[ Back to top ]