Fターム[5F140AA01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 周波数特性 (832)

Fターム[5F140AA01]に分類される特許

161 - 180 / 832

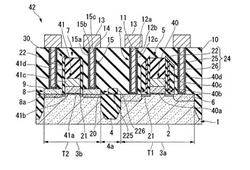

半導体装置及び半導体装置の製造方法

【課題】同一の工程で、同一半導体基板上に異なる構造のトランジスタを形成する半導体装置の提供。

【解決手段】半導体基板上に第一及び第二のゲート電極40,41を形成する工程と、第一のゲート電極の側壁面に第一の絶縁層122を形成するとともに、第二のゲート電極のゲート幅方向両側の半導体基板上にエピタキシャル成長層9aを形成する工程と、第二のゲート電極の側壁面に第二の絶縁層を形成する工程と、第一の絶縁層及び第二の絶縁層を覆うように第三の絶縁層を形成する工程と、第二の絶縁層を覆う第三の絶縁層を除去する工程と、第一のゲート電極のゲート幅方向両側の半導体基板及びエピタキシャル成長層にそれぞれ不純物を拡散させて、第一及び第二の不純物拡散領域6,8を形成する工程と、第一及び第二の不純物拡散領域にコンタクトプラグ12,15を接続させる工程と、を具備してなることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域に印加される応力分布のピークとソース領域近傍に発生する電位分布のピークの位置を最適化することで、キャリア速度を向上させて飽和電流特性を向上させることを可能にする。

【解決手段】半導体基板11に形成されたチャネル領域12と、前記チャネル領域12の一方側に形成されたソース領域19と、前記チャネル領域12の他方側に形成されたドレイン領域20と、前記チャネル領域12上にゲート絶縁膜13を介して形成されたゲート電極14と、前記チャネル領域12に応力を印加する第1、第2応力導入層21、23を有し、前記チャネル領域12と前記ソース領域19とのpn接合境界と、前記チャネル領域12と前記ドレイン領域20とのpn接合境界の間に、前記ソース領域19側の応力分布のピークと前記ドレイン領域20側の応力分布のピークが位置する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】良質な半導体−酸化物界面を有する電界効果トランジスタおよびその製造方法を提供する。

【解決手段】電界効果トランジスタ100は、半導体基板101と、半導体基板101上に形成されたチャネル層102と、チャネル層102上に形成された電子供給層103と、電子供給層103内に形成され、Ptを含む半導体層106と、半導体層106上に形成され、ゲート絶縁膜として機能するペロブスカイト型酸化物層107と、ペロブスカイト型酸化物層107上に形成されたゲート電極108とを備える。

(もっと読む)

半導体装置

【課題】インパクトイオン化現象によって発生した電子・正孔を効率よく吸収することが可能で正常な動作特性と高い信頼性を実現する半導体装置を提供する。

【解決手段】半導体装置20は、基板21に対して順次積層されたバッファ層22、下地化合物半導体層23f(下地化合物半導体層23)、インパクトイオン制御層24、下地化合物半導体層23s(下地化合物半導体層23)、チャネル画定化合物半導体層26f(チャネル画定化合物半導体層26)、チャネル画定化合物半導体層26s(チャネル画定化合物半導体層26)、AlGaN(窒化アルミニウムガリウム)層28、GaN(窒化ガリウム)層29を備えている。インパクトイオン制御層24は、下地化合物半導体層23の積層範囲(積層範囲の厚さTst)内に積層されてインパクトイオン化現象の発生位置を制御する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ低抵抗の半導体装置およびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された半導体層と、前記半導体層上に形成され、該半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極と、を備える。また、基板上に半導体層を形成する半導体層形成工程と、前記半導体層上に、前記半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極を形成する電極形成工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】PMISトランジスタのソースドレイン電極に高濃度のゲルマニウムを含むシリコンゲルマニウム層を用いても、シリコンゲルマニウム層に格子緩和を生じさせることなく、ソースドレイン電極の上部にシリコン層又は金属シリサイド層を形成できるようにする。

【解決手段】半導体装置は、n型半導体領域100の上にゲート絶縁膜101を介在させて形成されたゲート電極102と、その両側方に形成されたp型のソースドレイン電極150とを有している。ソースドレイン電極150は、n型半導体領域100に設けられた各リセス部100aに、その底部から少なくともチャネル領域の深さにまで形成されたシリコンゲルマニウム層111と、その上に形成され、炭素とシリコンゲルマニウム層のゲルマニウム濃度よりも低いゲルマニウムとを含むカーボンドープドシリコンゲルマニウム層112と、その上に形成された金属シリサイド層115とから構成される。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】低いコンタクト抵抗を有し、かつ、オン抵抗の増大を回避できて高いチャネル移動度を維持できるノーマリオフ動作の電界効果型トランジスタを提供する。

【解決手段】この電界効果型トランジスタは、AlGaN障壁層6の薄層部6aは、第2のGaN層4のV欠陥13およびV欠陥13に連なる第3のGaN層5の非成長領域G1上に形成されているので、エッチングを行うことなく平坦部6bよりも薄くできる。よって、エッチングダメージがチャネル移動度を低下させることがなく、オン抵抗の増大を回避できる。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTの増大及びキャリア移動度の低下を抑制しつつ、半導体基板表面に形成されている酸化膜と高誘電率絶縁膜との界面に、しきい値電圧を低減する電気双極子を形成可能な金属を添加する。

【解決手段】半導体基板100上にゲート絶縁膜140を介してゲート電極150が形成されている。ゲート絶縁膜140は、酸素含有絶縁膜101と、第1の金属を含む高誘電率絶縁膜102とを有する。高誘電率絶縁膜102は、第1の金属とは異なる第2の金属をさらに含む。高誘電率絶縁膜102における第2の金属の組成比が最大になる位置は、高誘電率絶縁膜102と酸素含有絶縁膜101との界面及び高誘電率絶縁膜102とゲート電極150との界面のそれぞれから離れている。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】短いゲート長を加工可能にする半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法の一形態は、シリコン基板2上にシリコン酸化膜34を形成し、酸化膜34上に所定幅T1を有する多結晶シリコン膜35aを形成し、少なくとも多結晶シリコン膜35aの両側部を酸化し、所定幅T1よりも狭い幅を有する酸化膜34の部分を多結晶シリコン膜35aの下に残すように、酸化膜34を、多結晶シリコン膜35aの酸化された部分と共にエッチングし、酸化された部分がエッチングされた多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入し、多結晶シリコン膜35aの両側に側壁絶縁膜14を形成し、側壁絶縁膜14が形成された多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入する、工程を有する。

(もっと読む)

半導体装置

【課題】デジタル回路と高周波回路とを混載した半導体装置において、デジタル回路の微細化を進めつつ、高周波回路の配線間容量を小さくする。

【解決手段】高周波回路100の第1トランジスタ120,140の第1ゲート電極124,144から第1コンタクト162,166までの距離aは、デジタル回路200の第2トランジスタ220,240の第2ゲート電極224,244から第2コンタクト262,266までの距離bより大きい。第1コンタクト162,166は第1トランジスタ120,140のドレイン126,146に接続しており、第2コンタクト262,266は第2トランジスタ220,240のドレイン226,246に接続している。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

調整した垂直窒素濃度分布を具備する窒化ゲート誘電体層を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(110,114又は122)のゲート誘電体層(500,566又は700)は、垂直濃度分布を有する窒素を含有している。

【解決手段】 該垂直濃度分布は、上側に位置しているゲート電極(502,568又は702)内のボロンが該ゲート誘電体層を介して下側のチャンネルゾーン(484,554又は684)内に著しく浸透することを防止し同時に該ゲート誘電体層から下側に存在する半導体ボディ内への窒素の移動を回避するために特別に調整されている。該チャンネルゾーン内の不所望のボロンから及び該半導体ボディにおける不所望の窒素から発生する場合がある損傷は実質的に回避される。

(もっと読む)

延長型ドレイン電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 拡張型ドレイン絶縁ゲート電界効果トランジスタ(104又は106)が、第1ウエル領域(184A又は186A)の一部によって構成されているチャンネル(322又は362)ゾーンによって横方向に分離されている第1及び第2ソース/ドレインゾーン(324及び184B又は364及び186B/136B)を包含している。

【解決手段】 ゲート誘電体層(344又は384)が該チャンネルゾーンの上側に存在している。該第1ソース/ドレインゾーンは、通常は、ソースである。通常はドレインである該第2S/Dゾーンは、少なくとも部分的には第2ウエル領域(184B又は186B)で構成されている。該半導体ボディのウエル分離部分(136A又は212U/136B)が該ウエル領域の間を延在しており且つ各ウエル領域よりも一層軽度にドープされている。該ウエル領域の構成は、該半導体ボディのIGFETの部分における最大電界をして上部半導体表面の十分に下側、典型的には該ウエル領域同士が互いに最も近い箇所におけるか又はその近くで発生させる。該IGFETの動作特性は動作時間と共に安定である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 電界効果型トランジスタの動作速度を向上させる半導体装置の製造方法、及び半導体装置を提供する。

【解決手段】 ゲルマニウム基板の上にシリコンゲルマニウムを含むエピタキシャル成長層を形成する工程と、エピタキシャル成長層上に酸化物層を形成する工程と、エピタキシャル成長層を熱処理する熱処理工程と、を含み、熱処理工程における熱処理は、加熱温度が600℃以上900℃以下であり、ゲルマニウム基板の上にシリコンゲルマニウムからなるエピタキシャル成長層を形成する工程は、エピタキシャル成長層にシリコンが5%以上20%以下、及びゲルマニウムが80%以上95%以下の割合で含有するように形成する。

(もっと読む)

非対称的チャンネルゾーン及び異なる構成としたソース/ドレイン延長部を有する非対称的電界効果トランジスタの構成及び製造

【課題】 非対称的絶縁ゲート電界効果トランジスタ(100又は102)は半導体ボディのボディ物質(180又は182)のチャンネルゾーン(244又は284)によって横方向に分離されたソース(240又は280)及びドレイン(242又は282)を有している。

【解決手段】 ゲート電極(262又は302)が該チャンネルゾーンの上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の一層高度にドープしたポケット部分(250又は290)がほぼ該ソースのみに沿って延在している。該ソースは、主要ソース部分(240M又は280M)と、一層軽度にドープした横方向ソース延長部(240E又は280E)とを有している。該ドレインは、主要ドレイン部分(242M又は282M)と、一層軽度にドープした横方向ドレイン延長部(242E又は282E)とを有している。該ドレイン延長部は該ソース延長部よりも一層軽度にドープされている。これら2つの延長部を画定する半導体ドーパントの最大濃度は、該ソース延長部におけるよりも該ドレイン延長部において一層深くに発生する。付加的に又は代替的に、該ドレイン延長部は該ソース延長部よりも該ゲート電極下側を更に横方向に延在する。これらの特徴はスレッシュホールド電圧が動作時間に関して高度に安定であることを可能とする。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのリーク電流を防止できる電界効果型トランジスタを提供する。

【解決手段】この電界効果型トランジスタによれば、WN/Alドレイン電極109がドレイン電極109の下のn+型領域(拡散領域)112を介してGaNチャネル層104にショットキー接合されている。これにより、従来の熱処理によりドレイン電極にオーミックコンタクトを形成する場合と異なり、ドレイン電極109下へメタルが侵入することを回避できる。よって、このメタル侵入が発生するために生じるリーク電流を低減することが可能であり、電界効果型トランジスタにおける破壊電圧を向上できる。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

ゲート・ダイオード構造及びゲート・ダイオード構造の製造方法

【課題】改善された特性と強化された機能とを備えたダイオード構造とその製造方法が望まれている。

【解決手段】ゲート・ダイオード構造及びSOI基板(SOI)等の上にゲート・ダイオード構造を製造する方法であって、緩和下地層(34‘)を用いる。緩和下地層は歪下地層(34)から形成される。歪下地層(34)は典型的にはゲート・ダイオード構造と同時に形成される電界効果型トランジスタに用いられる。緩和下地層は歪下地層(34)のイオン注入処理のような処理により形成される。反応性イオンエッチング方法を用いてゲート・ダイオード構造から歪下地層を除去するときのゲート・ダイオードの損傷がないので、歪下地層に比較して、緩和下地層はゲート・ダイオード構造の理想値を改善する。

(もっと読む)

161 - 180 / 832

[ Back to top ]