Fターム[5F140AA01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 周波数特性 (832)

Fターム[5F140AA01]に分類される特許

101 - 120 / 832

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタにおけるシリコン混晶層からなるソースドレイン領域を、不純物の拡散による不具合を防止しながらチャネル領域に近づけることができるようにする。

【解決手段】半導体装置は、半導体基板10からなるn型の活性領域の上に、ゲート絶縁膜12を介在させて形成されたゲート電極13と、活性領域におけるゲート電極13の両側方の領域に形成されたp型ソースドレイン領域20と、活性領域における各p型ソースドレイン領域20の側面からそれぞれゲート電極13の下側に向かって形成されたn型ポケット領域18とを有している。p型ソースドレイン領域20は、シリコンとIV族元素との混晶層からなり、混晶層は、ゲート長方向におけるゲート電極側の側面がゲート電極側に突き出す凸部20aを有している。凸部20aの先端は、ポケット領域18によって覆われている。

(もっと読む)

電界効果型トランジスタ

【課題】電流許容値の低下を抑制する。

【解決手段】Y方向に沿って延在する延在ゲート電極G11と、Y方向に沿って延在するダミーゲート電極DM1と、Y方向に沿って延在する延在ソース電極S11と、Y方向に沿って延在する延在ドレイン電極D11とを含む。延在ソース電極G11は、X方向においてダミーゲート電極DM1を覆う形状を有する。また、延在ドレイン電極G11は、X方向においてダミーゲート電極DM1を覆う形状を有する。

(もっと読む)

酸化膜形成方法

【課題】膜中欠損を生じさせることなくGe基板の表面にGe酸化膜を形成する。

【解決手段】Ge基板2の表面にGe酸化膜を形成するプロセスシステム1の酸化炉13において、1000Pa以下の圧力及び300℃以下の基板温度のもとでGe基板2にオゾン供給装置11からオゾンガスを供して当該基板の表面にGe酸化膜を形成する。室温よりも低温の基板温度のもとで前記基板に前記オゾンガスを供給してGe基板2上にオゾン分子層を形成させる。次いで、前記オゾンガスの供給を遮断させた後、Ge基板2を室温まで加熱することにより前記オゾン分子層によって当該基板の表面を酸化させてGe酸化膜を形成させる。Ge基板2が室温まで達した後に前記加熱を遮断して当該基板の温度を室温よりも低温に降下させるとよい。Ge基板2を加熱するための加熱源として赤外光光源を用いるとよい。前記オゾンガスはオゾン濃度が100%であるとよい。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】ゲート電極構造の垂直方向の抵抗を低減する。

【解決手段】半導体基板1と、半導体基板1の上に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成された仕事関数制御層3と、仕事関数制御層3の上に形成された第1のシリサイド層4と、第1のシリサイド層4の上に形成されたポリシリコンゲート電極5と、ポリシリコンゲート電極5の下の半導体基板1中の領域を挟んで半導体基板1中に形成されるソース領域6およびドレイン領域7と、を有する半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】側面に(110)面が形成されたGe若しくはSiGeのフィン構造を実現することができ、FinFET等の素子特性の向上に寄与する。

【解決手段】Ge若しくはSiGeのフィン構造部を有する半導体装置であって、Si基板10の表面部に、一方向に長いストライプ領域を挟むように埋め込み形成され且つ基板表面よりも高い位置まで形成された素子分離絶縁膜12と、ストライプ領域上に形成され、且つ最上面が前記素子分離絶縁膜の最上面よりも低い位置にあるSiGeバッファ層14と、バッファ層14上に形成され、該層14よりも一方向と直交する方向の幅が狭く基板面と垂直な(110)面を有するGeフィン構造16と、を備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極抵抗の増大や工程数の増加を招くことなく、シリコン混晶層を用いた歪技術により、半導体装置の高性能化を実現する。

【解決手段】半導体基板100における第1のゲート電極106Aから見て第1の絶縁性サイドウォールスペーサ111Aの外側に第1のソースドレイン領域114Aを形成する。その後、半導体基板100における第2のゲート電極106Bから見て第2の絶縁性サイドウォールスペーサ111Bの外側にリセス部119を形成すると共に、第2のゲート電極106Bを部分的に除去する。その後、リセス部109内に、第2のソースドレイン領域114Bとなるシリコン混晶層120を形成する。

(もっと読む)

単結晶ゲルマニウムまたはシリコンゲルマニウムを形成する方法

【課題】基板中に形成されたトレンチ中に、単結晶のゲルマニウムまたはシリコンゲルマニウムを形成する改良された方法を提供する。

【解決手段】誘電体分離3(例えばSTI)を有する基板1を準備する工程と、基板材料1(例えばSi)のトレンチエッチング4を行う工程と、トレンチ4内への充填層5(例えばGe)の選択成長を行う工程と、略溶融温度での充填層6の加熱により、充填層5(例えばGe)の再結晶化7により達成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】アンテナ効果によるゲート酸化膜の破壊等を防止するとともに、半導体装置の動作の遅延を抑制すること。

【解決手段】本発明の一態様に係る半導体装置は、前段出力トランジスタA1に金属配線A2aを介して接続された入力トランジスタゲート電極A9を有する入力トランジスタA3と、入力トランジスタゲート電極A9に抵抗素子A4を介して接続されたダミートランジスタA5を備える。抵抗素子A4は、入力トランジスタA3の後段に設けられ、金属配線A2aに接続されている。抵抗素子A4とダミートランジスタA5は、金属配線A2bを介して接続されている。

(もっと読む)

III−V族半導体装置の導電性の改善

III-V族半導体装置における導電性の改善について示した。第1の改良は、チャネル層とは幅の異なるバリア層を有することである。第2の改良は、金属/Si、Ge、またはシリコン-ゲルマニウム/III-Vスタックの熱処理により、Siおよび/またはゲルマニウムドープIII-V層に、金属-シリコン、金属-ゲルマニウム、または金属-シリコンゲルマニウム層を形成することである。次に、金属層が除去され、金属-シリコン、金属-ゲルマニウム、または金属シリコンゲルマニウム層上に、ソース/ドレイン電極が形成される。第3の改良は、III-Vチャネル層上に、IV族元素および/またはVI族元素の層を形成し、熱処理し、III-Vチャネル層に、IV族および/またはVI族化学種をドープすることである。第4の改良は、III-V装置のアクセス領域に形成された、パッシベーション層および/またはダイポール層である。  (もっと読む)

(もっと読む)

集積回路デバイスに歪みを与える技術及び構成

本開示の実施形態により、例えば横型電界効果トランジスタなどの集積回路デバイスに歪みを与える技術及び構成が提供される。集積回路デバイスは、半導体基板と、該半導体基板と結合された第1のバリア層と、第1のバリア層に結合された、第1の格子定数を持つ第1の材料を有する量子井戸チャネルと、量子井戸チャネルに結合されたソース構造とを含む。ソース構造は、第1の格子定数とは異なる第2の格子定数を持つ第2の材料を有し、量子井戸チャネルに歪みを与える。その他の実施形態も開示される。  (もっと読む)

(もっと読む)

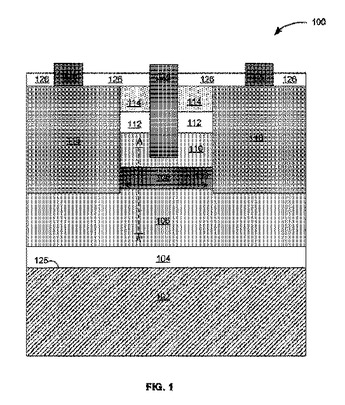

非平面ゲルマニウム量子井戸デバイス

非平面(ノンプレーナ)ゲルマニウム量子井戸構造を形成する技術が開示される。量子井戸構造は、IV族又はIII−V族の半導体材料を用いて実現されることができ、ゲルマニウムフィン構造を含む。一例において、非平面量子井戸デバイスが提供され、このデバイスは、基板(例えば、シリコン上にSiGe又はGaAsのバッファを有する)と、IV族又はIII−V族材料のバリア層(例えば、SiGe、GaAs又はAlGaAs)と、ドーピング層(例えば、デルタ/変調ドープされる)と、アンドープのゲルマニウム量子井戸層とを有する量子井戸構造を含む。アンドープのゲルマニウムフィン構造が量子井戸構造内に形成され、該フィン構造上に頂部バリア層が堆積される。ゲートメタルが、フィン構造を横切って堆積される。ドレイン/ソース領域がフィン構造のそれぞれのエンドに形成され得る。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極にシリサイドを形成しつつ、拡散領域に接続するコンタクトとゲート電極の間隔を確保する。

【解決手段】被覆絶縁膜120は、ゲート電極140のチャネル幅方向における少なくとも一部上に形成されている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、ゲート電極140上、及び被覆絶縁膜120上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。シリサイド層142は、ゲート電極140上に形成されている。サイドウォール160は、被覆絶縁膜120が形成されている領域においてはゲート電極140より高く形成されている。そしてコンタクト210は、ゲート電極140のうち被覆絶縁膜120が形成されている領域に面している。

(もっと読む)

半導体装置、および、その製造方法

【課題】半導体素子の特性を向上させると共に、半導体素子の微細化を容易に実現する。

【解決手段】半導体素子101にてゲート電極111gが設けられる部分の表面を凹凸面に形成する。ここでは、凹凸面のうち凸部CVでは、一対のソース・ドレイン領域112s,112dの表面と同一の面を覆うようにゲート絶縁膜111zを形成し、そのゲート絶縁膜111zの上面にゲート電極111gを設ける。これに対して、凹部TRでは、一対のソース・ドレイン領域112s,112dの表面から内部へ向けて設けられた溝Mの面を覆うようにゲート絶縁膜111zを形成し、その溝Mの内部を埋め込むようにゲート電極111gを設ける。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

半導体装置

【課題】応力の作用によって、チャネルの移動度をより向上させることができる半導体装置を提供する。

【解決手段】p型チャネルMOSFET20が形成されている半導体基板12を有する半導体装置10。半導体基板12のうちのp型チャネルMOSFET20のn型ウェルに接する領域には、STI50が形成されている。p型チャネルMOSFET20のソース22からドレイン24に向かう方向においてn型ウェルに接するSTI50aは、n型ウェル領域26に圧縮応力を作用させる絶縁材料により形成される。p型チャネルMOSFET20のソース22からドレイン24に向かう方向と直交する方向においてn型ウェル領域26に接するSTI50cは、n型ウェル領域26に引張応力を作用させる絶縁材料により形成される。

(もっと読む)

量子井戸型半導体装置

量子井戸型半導体装置、および量子井戸型半導体装置を形成する方法について示した。本方法は、基板の上部に配置され、量子井戸チャネル領域を有するヘテロ構造を提供するステップを有する。また、この方法は、ソースおよびドレイン材料領域を形成するステップを有する。また、この方法は、ソースおよびドレイン材料領域に溝を形成するステップを有し、ドレイン領域から分離されたソース領域が提供される。また、この方法は、溝内のソース領域とドレイン領域の間に、ゲート誘電体層を形成するステップと、溝内のゲート誘電体層の上部に、ゲート電極を形成するステップとを有する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層の厚みのバラツキを抑制できるJFET、MOSFETもしくはMESFETを備えた半導体装置およびその製造方法を提供する。

【解決手段】n+型層3に対して異方性エッチングを行うことによって凹部4を形成したのち、この凹部4内にエピタキシャル成長させることによってn型チャネル層5を形成する。これにより、n型チャネル層5を一定の膜厚かつ一定の濃度で形成することが可能となる。このため、従来の構造と異なり、n型チャネル層5の膜厚が一定なバラツキのない構造とすることが可能となる。したがって、JFETの特性も一定とすることが可能となる。

(もっと読む)

不均一な半導体装置のアクティブ領域パターン形成方法

【課題】不均一な半導体装置のアクティブ領域パターン形成方法を提供する。

【解決手段】具体例によると、少なくとも3つのアクティブ領域を含む半導体装置が提供される。少なくとも3つのアクティブ領域は隣接する。少なくとも3つのアクティブ領域の縦軸は平行で、少なくとも3つのアクティブ領域は、それぞれ、対応するアクティブ領域の縦軸と交差する辺縁を有する。少なくとも3つのアクティブ領域の辺縁は弧形を形成する。

(もっと読む)

101 - 120 / 832

[ Back to top ]