Fターム[5F140AA01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 周波数特性 (832)

Fターム[5F140AA01]に分類される特許

21 - 40 / 832

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

トレンチ拡散領域を有する金属酸化物半導体デバイスおよびその形成方法

【課題】改善された高周波性能およびオン状態特性を可能にするMOSデバイスを提供すること。

【解決手段】MOSデバイスは、第1の伝導型の半導体層と、半導体層の上面に近接して半導体層中に形成された第2の伝導型の第1および第2のソース/ドレイン領域とを含む。第1および第2のソース/ドレイン領域は、互いに間隔を開けて配置されている。ゲートは、少なくとも部分的に第1のソース/ドレイン領域と第2のソース/ドレイン領域との間の半導体層の上に形成され、かつ半導体層から電気的に絶縁されている。第1および第2のソース/ドレイン領域のうちの少なくとも特定の1つは、半導体層とその特定のソース/ドレイン領域との間の接合の幅よりも実質的に大きな実効幅を有して形作られている。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

炭化珪素半導体を用いたMOS構造およびその酸化膜形成方法

【課題】 SiO2/SiC界面における界面準位自体を低減することが出来るSiC半導体を用いたMOS構造、およびその酸化膜の形成方法を提供する。

【解決手段】 SiC半導体基板1を処理炉内に用意し、処理炉内を比較的低い700℃に設定して、SiC半導体基板1の基板表面を酸素ガス雰囲気中にさらす。この熱酸化により、SiC半導体基板1の基板表面には、SiO2から成る中間層2が約1nmの極薄い厚さで形成される。次に、中間層2上にSiO2膜を約50nmの厚さに堆積して、SiO2から成る堆積層3を形成する。次に、SiC半導体基板1が酸化しない温度および時間で、堆積層3をアニーリングする。このアニーリングは、赤外線ランプなどの急速加熱装置により、SiO2膜の融点である1200℃に近い、この1200℃の融点よりも低い例えば1000〜1100℃程度の温度で、短時間に急速に行われる。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】高性能なIII−V族MISFETの実現を可能にする、より効果的なIII−V族化合物半導体表面のパッシベーション技術を提供する。

【解決手段】エピタキシャル成長により化合物半導体層をベース基板上に形成するステップと、前記化合物半導体層の表面をセレン化合物を含む洗浄液で洗浄するステップと、前記化合物半導体層の上に絶縁層を形成するステップと、を有する半導体基板の製造方法を提供する。前記セレン化合物として、セレン酸化物が挙げられる。前記セレン酸化物として、H2SeO3が挙げられる。前記洗浄液が、水、アンモニアおよびエタノールからなる群から選択された1以上の物質をさらに含んでもよい。前記化合物半導体層の表面がInxGa1−xAs(0≦x≦1)からなる場合、前記絶縁層がAl2O3からなるものであることが好ましく、Al2O3は、ALD法により形成されることが好ましい。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】ウルツ鉱型結晶構造の半導体を用いた電界効果トランジスタで、電極との接触抵抗を高くすることなく、バンドギャップエネルギーのより大きな半導体から障壁層が構成できるようにする。

【解決手段】ゲート電極104を挟んで各々離間して障壁層103の上に接して形成された2つの電流トンネル層105と、各々の電流トンネル層105の上に形成された2つのキャップ層106とを備える。電流トンネル層105の分極電荷は、障壁層103の分極電荷よりも大きい。

(もっと読む)

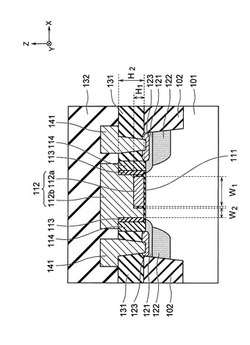

半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

半導体装置

【課題】低オン抵抗特性を有するパワーMOSトランジスタのスイッチング特性を、従来以上に改善した高効率パワーMOSトランジスタを実現する。

【解決手段】Finger形状電極からなるソース電極8とドレイン電極9の間をFinger形状電極の一方の端部GE1から他方の端部GE2まで延在するゲート電極6と、層間絶縁膜7に形成されたコンタクトホールを介してゲート電極6の端部GE1、GE2とそれぞれ接続されるゲート引き出し電極と、前記層間絶縁膜7上を被覆するパッシベーション膜12と、該パッシベーション膜12の開口に露出する前記ゲート引き出し電極の一部となるゲート接続電極G1、G2と、該ゲート接続電極G1、G2に形成された突起電極25を備える半導体チップ100を、該突起電極25を介して、BGA基板200の表面201に形成された低抵抗のゲート電極シャント用基板配線23に接続する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

半導体基板、半導体装置及びその製造方法

【課題】キャリア移動度(チャネル移動度)を増加させて、オン電流を増加させること。

【解決手段】トランジスタを形成するための半導体基板(10)は、主面(11a)を持つシリコン基板(11)と、このシリコン基板(11)の主面(11a)上に形成された歪緩和SiGe層(12)と、この歪緩和SiGe層(12)上に形成された歪Si層(13)と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 層間絶縁膜をCMP法で研磨、平坦化する際、MOS型トランジスタのチャネル領域に応力を与えるためにゲート電極を覆うように形成される応力ライナー膜が研磨されて、トランジスタ特性の変動やバラツキが発生しないようにする。

【解決手段】 第1活性領域(例えばPチャネルトランジスタ形成領域)上のゲート電極(シリコン膜14と金属シリサイド膜15との積層膜)上には第1応力膜(圧縮応力ライナー膜)16のみを形成し、第2活性領域(例えばNチャネルトランジスタ領域)上のゲート電極上には第2応力膜(引っ張り応力ライナー膜)18のみを形成する。一方、素子分離10上のゲート電極上には第1および第2応力膜16、18の積層膜を形成する。層間絶縁膜20のCMP法による研磨は、素子分離10上の第2応力膜18の露出後に停止する。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

半導体装置

【課題】横型構造のパワートランジスタにおいて、寄生サイリスタのラッチアップ耐量を改善するとともに、ターンオフ時間を短縮する。

【解決手段】エミッタ電極(21)下部に設けられるn+エミッタ層(6)を、所定の間隔で互いに離れて配置される単位領域(60)で構成する。単位領域においてエミッタ電極とのコンタクトを取るとともに、pベース層(5)よりも高濃度でp+層(45)を少なくともエミッタ層の下方に設ける。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】電極材料が拡散するのを抑制し、特性の向上を実現する。

【解決手段】半導体装置を、ゲート電極3とゲート絶縁膜2との間、Al含有オーミック電極4、5とAu配線9との間、及び、ゲート電極3の下方及びAl含有オーミック電極4、5の上方、のいずれかに設けられ、第1TaN層6A、Ta層6B、第2TaN層6Cを順に積層した構造を有する電極材料拡散抑制層6を備えるものとする。

(もっと読む)

トランジスタの制御回路、トランジスタの制御システム、およびトランジスタの制御方法

【課題】ゲートとフィールドプレートとを有するトランジスタのスイッチング速度を速くする。

【解決手段】ゲートとフィールドプレートとを有するトランジスタ4を制御する制御回路2であって、トランジスタを駆動するタイミングを検出する検出回路38と、駆動するタイミングに応答してゲートを駆動する第1の駆動タイミングとフィールドプレートを駆動する第2の駆動タイミングとを制御するタイミング制御回路40と、第1の駆動タイミングに応答してゲートを駆動し第2の駆動タイミングに応答してフィールドプレートを駆動する駆動回路42とを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMTの信頼性を高める。

【解決手段】基板10の上方に形成された窒化物半導体からなる半導体層21〜24と、半導体層21〜24の上方に、金を含む材料により形成された電極41と、電極41の上方に形成されたバリア膜61と、半導体層21〜24の上方に、シリコンの酸化膜、窒化膜、酸窒化物のいずれかを含む材料により形成された保護膜50と、を有する。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

21 - 40 / 832

[ Back to top ]