Fターム[5F140AA27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | イオン注入ダメージの防止 (16)

Fターム[5F140AA27]に分類される特許

1 - 16 / 16

半導体装置の製造方法

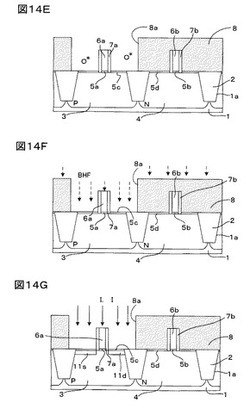

【課題】レジストパターンの下地層への悪影響を及ぼすことなくスカムを最適に除去する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上に酸化膜5cを形成し、前記酸化膜5c上にフォトレジスト8を塗布し、前記フォトレジスト8を露光し、露光された前記フォトレジスト8を現像することにより前記フォトレジス8トに開口部8aを形成し、前記フォトレジスト8をマスクとして、前記酸化膜5cを酸素プラズマ処理し、前記酸素プラズマ処理の後、前記酸化膜5cと前記フォトレジスト8に希釈フッ酸を供給し、前記希釈フッ酸を供給する工程の後、前記フォトレジスト8をマスクとして前記酸化膜5cを通して記半導体基板1に一導電型不純物をイオン注入する工程を含む。

(もっと読む)

半導体装置およびその製造方法、固体撮像素子、電子情報機器

【課題】従来のようにトランジスタゲート面積を大きくすることなく、より簡単な製造工程で、トランジスタのソース側ゲート端のイオン注入ダメージにより発生するソース側ゲート端付近の欠陥を低減することにより、ランダムノイズを効果的に低減する。

【解決手段】ドレイン側のLDD領域のN型拡散層11だけがゲート電極6の他方端の下に潜り込んで、ドレイン側のLDD領域のN型拡散層11がゲート電極6と平面視でオーバラップし、ソース側のLDD領域のN型拡散層12はゲート電極6の一方端の下に潜り込まず、ソース側のLDD領域のN型拡散層12がゲート電極6と平面視でオーバラップしておらず、ソース側のLDD領域のN型拡散層12がゲート電極6の一方端と離間して形成されている。

(もっと読む)

半導体装置の製造方法

【課題】歪み技術を利用した性能のよい半導体装置を低コストで製造する。

【解決手段】シリコン基板10上のnMOS形成領域12a及びpMOS形成領域12bにそれぞれゲート電極15a,15bを形成し、pMOS形成領域12bを覆い、フォトレジストマスク18を形成して、イオン注入によりnMOSのソース/ドレイン領域17aを形成するとともに、ゲート電極15aをアモルファス化し、フォトレジストマスク18を除去した後に、シリコン基板10上に、ゲート電極15a,15bを覆うように、引っ張り歪みを有するキャップ膜19を形成し、nMOS形成領域12aを覆うようにフォトレジストマスク20を形成し、pMOS形成領域12bのキャップ膜19に不純物をイオン注入し、フォトレジストマスク20を除去した後に、アニール処理を行い、nMOSのゲート電極15a下のチャネルに対し、チャネル深さ方向の圧縮歪みを加える。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板に形成された電界効果トランジスタのソース領域やドレイン領域に生じる欠陥を抑制する。

【解決手段】半導基板1の主面上にゲート電極7Gを形成した後、ゲート電極7Gをマスクとして不純物を半導体基板1に導入することにより半導体基板1の主面に低濃度層11を形成する。続いて、ゲート電極7Gの側面に第1サイドウォール12および第2サイドウォール13を形成した後、第1サイドウォール12、第2サイドウォールおよびゲート電極7Gをマスクとして半導体基板1に窒素等をイオン打ち込みすることにより、半導体基板1の主面に結晶化抑制領域CCRを形成する。その後、第2サイドウォール13を除去した後、半導体基板1の主面に、ソースおよびドレイン用の高濃度層を形成する。

(もっと読む)

半導体装置およびその製造方法

【目的】トレンチ横型パワーMOSFETにおいて、信頼性を高めること。また、デバイスピッチを小さくすること。

【構成】半導体基板にn型ウェル領域2、p型オフセット領域4を形成し、トレンチ5を平面形状が環状になるように形成する。トレンチ5の第1の側壁に沿ってゲート酸化膜13を形成し、トレンチ5の第2の側壁に沿ってフィールドプレート酸化膜14を形成し、半導体基板表面上およびトレンチ内面にポリシリコンを堆積する。その後、半導体基板表面およびトレンチ底面のポリシリコンを除去するために異方性エッチングを行う。その後、n型ソース領域7を形成するとともに、n型ドレイン領域6を形成する。層間絶縁膜でトレンチ5の内部を埋めるとともに、n型ソース領域7およびn型ドレイン領域6の表面を覆い、その層間絶縁膜にコンタクトホールを開口する。そして、ソース電極10とドレイン電極9を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】イオン注入を行うことに起因する電気的特性の低下およびしきい値電圧の変動を抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置は、シリコン基板1にチャネル領域3を挟むように形成された一対のソース/ドレイン領域4と、チャネル領域3上にゲート絶縁膜5を介して形成されたゲート電極6とを備えている。そして、ゲート電極6は、金属含有層7と、金属含有層7上に形成された金属含有層9と、金属含有層7と金属含有層9との間に形成されたポリシリコン層8とを含む。

(もっと読む)

半導体素子のデュアルゲート形成方法

【課題】イオン注入マスク膜として用いられるフォトレジスト膜パターンを残留物なしに除去し、自然酸化膜除去のための洗浄工程で発生するウォーターマークを防止する半導体素子のデュアルゲート形成方法を提供する。

【解決手段】半導体基板300の第1領域100及び第2領域200上にそれぞれp型及びn型にドーピングされた第1及び第2ポリシリコン膜110,210を形成する段階と、前記第1及び第2ポリシリコン膜110,210の表面上に第1湿式洗浄、第2湿式洗浄及び乾式洗浄を順次行う段階と、を含んで半導体素子のデュアルゲート形成方法を構成する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタ特性のばらつきが抑えられた半導体装置の製造方法を提供する。

【解決手段】P型MOSFETとN型MOSFETを有する半導体装置の製造方法であって、半導体基板上にゲート絶縁膜、ノンドープポリシリコン膜、金属シリサイド膜、金属ナイトライド膜、金属膜を形成する工程と、金属シリサイド膜の、P型MOSFETのゲート電極を構成する部分とN型MOSFETのゲート電極を構成する部分とが互いに分離するように、金属膜、金属ナイトライド膜および金属シリサイド膜を少なくとも加工してゲート形状にパターニングする工程と、P型およびN型のMOSFET形成領域内のノンドープポリシリコン膜にそれぞれP型およびN型不純物を導入する工程と、不純物を拡散させるための熱処理を行う工程と、不純物導入後のポリシリコン膜をゲート形状にパターニングする工程を有する半導体装置の製造方法。

(もっと読む)

熱処理装置、熱処理方法及び半導体装置の製造方法

【課題】ダメージを抑制して熱処理することが可能な熱処理装置を提供する。

【解決手段】半導体基板10を載置する基板ステージ32と、半導体基板10の表面を区分する複数の区域のそれぞれを、基板ステージ32を通して選択的に予備加熱する複数の加熱部を有する加熱源43と、基板ステージ32に対向して配置され、半導体基板10の表面全体に0.1m秒〜100m秒のパルス幅の光を照射する光源40とを備える。

(もっと読む)

半導体素子の製造方法

【課題】本発明は、半導体素子の製造に関するものである。

【解決手段】半導体素子の活性領域内における高いキャリア移動度を達成するために、ゲルマニウム原子を半導体基板の表面に打ち込み、半導体基板の内部にゲルマニウムを含む層を形成する。そして、上記ゲルマニウムを含む層の上部を含み、当該半導体基板の表面から上記ゲルマニウムを含む層の上部までを酸化し、打ち込まれたゲルマニウム原子を表面から上記半導体基板内に押し込む。これにより、酸化された上部を除くゲルマニウムを含む層の内部でゲルマニウム濃度が上昇し、ゲルマニウム濃度が高い層が半導体基板の内部に形成される。上記ゲルマニウム濃度が高い層内の少なくとも一部に、半導体素子の活性領域を配置することにより、上記半導体素子は製造される。

(もっと読む)

互いに重ねて堆積させた金属層の積層体中に形成されたゲート電極を含むMOSトランジスタを備える半導体デバイスの製造方法

互いに重ねて堆積させたいくつかの金属層(8,9,13;8,12,13)として形成したゲート電極(15,16)を有するMOSトランジスタを備える半導体デバイスの製造方法。この方法では、シリコン本体(1)に、ゲート誘電体層(7)を備えるシリコン活性領域(4,5)およびこれらの領域を互いに絶縁するフィールド分離領域(6)を形成する。次いで、第1の金属層(8)を堆積させ、活性領域(4)の一部の位置でその層中に局所的に窒素を導入する。次いで、第1の金属層上に第2の金属層(13)を堆積させ、その後それらの金属層中にゲート電極をエッチングする。第1の金属層中に窒素を導入する前に、第1の金属層上に窒素透過性の第3の金属補助層(9)を堆積させる。したがって、その下にあるゲート電極に損傷を与える危険なく、第1の金属層を窒化することができる。金属の仕事関数を実質的に変えることが可能であるとともに、NMOSおよびPMOSを備える半導体デバイスが実現される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 ゲート電極と異物の衝突を抑えることができる半導体装置の製造方法を得る。

【解決手段】 本発明に係る半導体装置の製造方法は、ゲート電極を有する半導体装置が表面に形成されたウェハをディスクの周縁内側に並べて、ディスクを回転させながらウェハの表面にイオン注入する半導体装置の製造方法において、異物のゲート電極への衝突角度に応じた高さのダミーのフォトレジストをウェハ内の分離酸化膜、ウェハの周辺部、又はダイシング部の上に形成する。

(もっと読む)

絶縁膜の形成方法および炭化珪素半導体装置

【課題】 SiC結晶中における結晶欠陥の増加を抑制しつつ、SiC結晶上への絶縁膜形成速度を改善した絶縁膜形成方法と、この方法を用いて形成された絶縁膜を含むSiC半導体装置を提供する。

【解決手段】 SiC結晶1上への絶縁膜の形成方法であって、SiC結晶1上にSi膜2を形成する工程と、Si膜2を酸化または窒化することによりSiを含む絶縁膜を形成する工程と、を含む絶縁膜の形成方法である。また、この絶縁膜形成方法を用いた炭化珪素半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】接合リーク電流の増大、接合耐圧の劣化を抑制したシリサイドコンタクトを達成する半導体装置の製造方法を提供する。

【解決手段】ソース及びドレイン領域(S,D)形成のドーパントイオン打ち込み工程を、ウエル領域(3)との間にp/n接合を形成する1回のドーパントイオン打ち込みと、ソース・ドレイン領域(S,D)とウエル領域との間のp/n接合位置に影響を与えない打ち込み深さが浅く、かつ打ち込み量の多い1回のドーパントイオン打ち込みに分けて行う。そして、ドーパントの活性化熱処理を実施した後、ソース・ドレイン領域表面をシリサイド化(12)することにより、ソース・ドレイン領域(S,D)の低抵抗化とともにp/n接合リークの低減を図ることができる。

(もっと読む)

半導体装置

【課題】エンハンスメント型のMOS構造を有する半導体装置において、大きなリーク電流を発生させないようにする。

【解決手段】エンハンスメント型トランジスタにおいて、ゲート電極13下のチャネル領域に形成される高濃度P領域17を、ソース領域15bに接し、ドレイン領域15aに接しないようにする。このことによって、ドレイン領域15aと高濃度P領域17間のPN接合がなくなり、リーク電流を低減することができる。また、ドレイン領域15aと高濃度P領域17との距離は、ドレイン領域15aに動作電圧が印可されたときに拡がる空乏層が、高濃度P領域17の内部に拡がったとしても、空乏層内部の電界がアバランシェ降伏あるいはツェナー降伏を発生させる臨界電界に達しないような距離とする。これによりアバランシェ降伏あるいはツェナー降伏によるリーク電流の増大を抑制することができる。

(もっと読む)

SiC半導体のイオン注入層及びその製造方法

【課題】 結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層を提供する。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

(もっと読む)

1 - 16 / 16

[ Back to top ]