Fターム[5F140AC24]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 縦型トランジスタ(縦型DMOSなど) (291) | 縦型IGBT (35)

Fターム[5F140AC24]に分類される特許

1 - 20 / 35

半導体装置

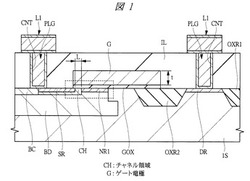

【課題】微細CMOSと中高耐圧MOSFETとの混載を前提とする集積回路(半導体装置)において、中高耐圧MOSFETのチャネル長やしきい値電圧のばらつきを抑制して、設計仕様どおりの安定した回路動作の実現や出力電流密度の向上を図ることができる技術を提供する。

【解決手段】本発明における特徴は、チャネル領域CHの幅(チャネル長)を小さくしたことにある。具体的には、ゲート電極Gと平面的に重なるチャネル領域CHの幅をLとし、ゲート電極Gの厚さをtとした場合、チャネル領域CHの幅Lが、ゲート電極Gの厚さtの1/5倍以上1倍以下になるようにチャネル領域CHを形成する。これにより、チャネル領域CHの幅Lを小さくすることができ、しきい値電圧のばらつきを小さくすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の表面に導入された不純物を、前記表面の浅い領域に高精度かつ高濃度で分布させ、不純物が半導体基板の深い領域に拡散することを防ぐことで、半導体装置の歩留まりおよび性能を向上させ、装置の微細化を容易にする。

【解決手段】N型MISトランジスタにおいて、半導体基板300に打ち込まれた炭素が、同じ領域に打ち込まれたホウ素を引き寄せる性質を利用し、ホウ素をN型の不純物として注入したハロー領域306に炭素を共注入して炭素注入層307を形成する。これにより、ホウ素が増速拡散することを防ぎ、ハロー領域306を高い精度で形成することを可能とすることで、微細化された半導体素子の短チャネル効果の発生を抑制する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高いゲート絶縁膜を備えたSiC半導体装置を提供する。

【解決手段】8度以下のオフ角度を有する炭化珪素基板(1)と、この基板上に形成された第1導電型の第1炭化珪素領域(2)と、この領域の表面に形成された第2導電型の第2炭化珪素領域(3)と、この領域の表面に形成され、不純物濃度が第2の炭化珪素領域と同程度に調整された第1導電型の第3炭化珪素領域(4)と、この領域の表面に選択的に形成された第1導電型の第4炭化珪素領域(5)と、第2炭化珪素領域の表面に形成された第2導電型の第5炭化珪素領域(6)と、第1炭化珪素領域から第3炭化珪素領域の少なくとも端部までを覆うように形成されたゲート絶縁膜(7)と、この上に形成されたゲート電極(8)とを具備し、第3炭化珪素領域の表面における、第3と第4炭化珪素領域の境界面は、オフ角度方向と90°以外の角度で交差するように形成されている。

(もっと読む)

半導体装置および電力変換器

【課題】部品点数を増やすことなく、SiC半導体装置の結晶劣化の進行を抑制することが可能な半導体素子を提供する。

【解決手段】p型コレクタ域91およびn型コレクタ領域92を含むコレクタ層93と、n型半導体層20と、p型ボディ領域30と、n型エミッタ領域40と、ボディ領域30に接して形成されたチャネルエピ層50と、エミッタ電極45と、ゲート絶縁膜60と、ゲート電極65と、コレクタ電極70とを備える構造とする。双方向導通IGBT100のゲート電極65に印加する電圧が閾値電圧よりも小さい場合、エミッタ電極45からチャネルエピ層50を介してコレクタ電極70へ電流を流すダイオードとして機能させる。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSFET動作からIGBT動作に切り替わるときのコレクタ電圧を上昇させずに、アバランシェ耐量を向上させる半導体装置を提供する。

【解決手段】P-型基板の表面部に形成されたN型リサーフ領域と、P型ベース領域と、N+型エミッタ/ソース領域105と、ゲート絶縁膜と、N型リサーフ領域内に形成されたN+型ドレイン領域109及びP+型コレクタ領域108と、ゲート絶縁膜上に形成されたゲート電極107と、P+型コレクタ領域108及びN+型ドレイン領域109に電気接続されたコレクタ/ドレイン電極と、N+型エミッタ/ソース領域105に電気接続されたエミッタ/ソース電極と、N型リサーフ領域内であってP型ベース領域及びN+型ドレイン領域109とは離隔しP+型コレクタ領域108の側面と対向して形成された、N型リサーフ領域よりも高いキャリア濃度のバッファ領域114とを備える半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧を向上した半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、第4半導体領域、ゲート領域、ゲート絶縁膜及び電界緩和領域を備える。第1導電形の第1半導体領域は、第1部分と第1方向に延出した第2部分とを有する。第1導電形の第2半導体領域は、第1部分上の第3部分と第2部分と隣接する第4部分とを有する。第2導電形の第3半導体領域は、第3部分上の第5部分と第4部分と隣接する第6部分とを有する。第1導電形の第4半導体領域は、第5部分上で第6部分と隣接する。ゲート領域は、第2半導体領域、第3半導体領域及び第4半導体領域を第2方向に貫通するトレンチ内に設けられる。ゲート絶縁膜は、トレンチ内壁とゲート領域との間に設けられる。第2導電形の電界緩和領域は、第3部分と第5部分との間に設けられ、第3半導体領域よりも不純物濃度が低い。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】窒化処理によって低下した閾値電圧を、向上させることができる炭化珪素半導体装置の製造方法を提供する。

【解決手段】ベース領域7およびソース領域8を含む炭化珪素ドリフト層6上に二酸化珪素を主成分とするゲート絶縁膜11が形成された炭化珪素基板2を窒化処理する窒化処理工程と、窒化処理工程後、炭化珪素基板2を、一酸化二窒素を含む雰囲気中で600℃以上1000℃以下の温度で熱処理する熱処理工程と、を備える。

(もっと読む)

双方向素子および半導体装置

【課題】高耐圧でオン電圧を低くできる双方向素子および半導体装置を提供すること。

【解決手段】分割半導体領域にpオフセット領域5とその表面に第1、第2nソース領域9、10を形成することで、第1、第2nソース領域9、10の平面距離を短縮してセルの高密度化を図り、トレンチに沿って耐圧を維持させることで高耐圧化を図り、ゲート電極7の電圧を第1、第2nソース電極11、12より高くすることで、トレンチ側壁にチャネルを形成して、双方向へ電流が流れる高耐圧で低オン電圧の双方向LMOSFETとすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】パワーMOSトランジスタのサイズの縮小を図り、ソース・ドレイン間絶縁破壊電圧の低下を防止する。

【解決手段】P+型コンタクト層17をN+型ソース層18の底面の直下のP型ベース層13内に埋め込んで形成する。これによりP型ベース層13の表面にN+型ソース層18と並列にP+型コンタクト層17を形成する必要がなくなりN+型ソース層18の幅を狭くできる。また、N+型ソース層18の底面の直下のP型ベース層13内にP+型コンタクト層17を形成するため、従来に比して、P+型コンタクト層17のN+ソース層18に対する面積占有率を大きくできる。この結果、NPN寄生トランジスタがオンすることを妨げる事ができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐圧確保とターンオフタイム短縮の両立が可能なIGBT構造を有する半導体装置を提供する。

【解決手段】縦型IGBT構造とPMOSFET30とが半導体基体上に一体で形成されている半導体装置10を構成する。この半導体装置は、PMOSFET30のドレイン電極29と、IGBTのコレクタ11とが電気的に接続されている。また、PMOSFET30のソース領域(第2のベース領域14)とドリフト領域12とにまたがって形成されたドリフト領域の取り出し領域(NSD19)が、PMOSFET30のソース領域の取り出し領域(PSD20)と導電膜により接続されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接触を発生させることなく、炭素の析出を抑制することにより配線の密着性を向上したオーミック電極を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】

SiC半導体装置においてオーミック電極を形成する際に、SiC層11の一方の主表面上には、1種の第1の金属元素からなる、第1の金属層12を形成する。また、第1の金属層の、SiC層11と対向する表面とは反対側の表面上(図1における上側)に、SiからなるSi層13を形成する。このようにして形成した積層構造10Aに対して熱処理を行なう。以上により、電極の表面層への炭素原子の析出や、SiとSiCとによるショットキー接触の形成が抑制された、配線との良好な密着性を示すオーミック電極を有する炭化珪素半導体装置を得ることができる。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方に保護ダイオードが配置されるためトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、素子領域の端部のセルではソースパッド部からゲートパッド部を迂回するように電流経路が形成される領域があった。

【解決手段】電極構造を2層とし、ゲートパッド部の少なくとも一部に保護ダイオードとの非重畳領域を形成する。非重畳領域下方にセルおよび1層目のソース電極層を配置でき、ソース電極層内の抵抗の偏りを小さくできる。更に、ゲートパッド部から保護ダイオードまでの距離が、ソースパッド部から保護ダイオードまでの距離より小さくなる位置に保護ダイオードを配置する。これにより効率的にトランジスタ動作を行える素子領域を大きく確保でき、且つ配線部下方の第1ソース電極層抵抗を低減できる。

(もっと読む)

半導体装置

【課題】絶縁ゲート構造を有する横型の高耐圧半導体装置において、セル面積の増大を抑えつつ、素子全体の耐圧を向上させること。

【解決手段】平面レイアウトにおいて、トラック形状のゲート電極38は、直線状に延びるコレクタ電極40を囲む。トラック形状のエミッタ電極37は、ゲート電極38を囲む。トラック形状の第1分離トレンチ43aは、エミッタ電極37を囲む。第2分離トレンチ43bは、第1分離トレンチ43aを囲む。第1分離トレンチ43aと第2分離トレンチ43bの間の領域は、n型の分離シリコン領域44である。分離シリコン領域44は、エミッタ電極37と同電位になっている。ゲート電極38を通る切断線Q−R−Sにおける断面構成において、ゲート電極38の弧状部分に対応するR−S間のpベース領域の深さは、ゲート電極38の直線状部分に対応するQ−R間のpベース領域の深さよりも浅い。

(もっと読む)

半導体装置

【課題】(0001)面や(11−20)面よりも優れた(000−1)面の炭化珪素基板を用いた半導体装置において、ゲート酸化後の熱処理方法を最適化することにより、高耐圧で高チャネル移動度を有するSiC半導体装置を提供する。

【解決手段】(000−1)面の炭化珪素からなる半導体領域にゲート絶縁膜と、そのゲート絶縁膜上にゲート電極と、上記半導体領域に電極を有する半導体装置において、ゲート絶縁膜中に1E19/cm3から1E20/cm3の範囲の水素あるいは水酸基(OH)を含む。或いは、ゲート絶縁膜と半導体領域の界面に1E20/cm3から1E22/cm3の範囲の水素あるいは水酸基(OH)が存在する。

(もっと読む)

半導体装置およびその製造方法

【課題】短絡耐量の大きい半導体装置およびその製造方法を提供すること。

【解決手段】n-ドリフト領域3の表面層にpボディ領域4と、nバッファ領域7とが離れて設けられている。pボディ領域4の表面層には、n+エミッタ領域5とp+コンタクト領域6とが接するように設けられている。nバッファ領域7の表面層には、p+コレクタ領域が設けられている。n-ドリフト領域3の上には、絶縁膜9が設けられており、n+エミッタ領域5、pボディ領域4およびn-ドリフト領域3の上にはゲート絶縁膜10が設けられている。絶縁膜9の一部およびゲート絶縁膜10の上には、ゲート電極11が設けられている。pボディ領域4内の、pボディ領域4領域と、n+エミッタ領域5およびp+コンタクト領域6との界面には、p+低抵抗領域41が設けられている。p+低抵抗領域41を含むpボディ領域4には、ゲート絶縁膜10との界面で不純物濃度が極大となる位置が2箇所ある。

(もっと読む)

半導体装置

【課題】信頼性の高いゲート絶縁膜を備えたSiC半導体装置を提供する。

【解決手段】8度以下のオフ角度を有する炭化珪素基板(1)と、この基板上に形成された第1導電型の第1炭化珪素領域(2)と、この領域の表面に形成された第2導電型の第2炭化珪素領域(3)と、この領域の表面に形成され、不純物濃度が第2の炭化珪素領域と同程度に調整された第1導電型の第3炭化珪素領域(4)と、この領域の表面に選択的に形成された第1導電型の第4炭化珪素領域(5)と、第2炭化珪素領域の表面に形成された第2導電型の第5炭化珪素領域(6)と、第1炭化珪素領域から第3炭化珪素領域の少なくとも端部までを覆うように形成されたゲート絶縁膜(7)と、この上に形成されたゲート電極(8)とを具備し、第3炭化珪素領域の表面における、第3と第4炭化珪素領域の境界面は、オフ角度方向と90°以外の角度で交差するように形成されている。

(もっと読む)

半導体装置

【課題】横型IGBTに対する過電流保護機能を有する半導体装置において、過電流保護機能が働く電流値のバラツキを低減する。

【解決手段】ゲート電圧により制御可能な主スイッチング素子である横型IGBT1と、電流検出用横型IGBT10とが並列に接続されている。電流検出用横型IGBT10ののベース領域109と、横型IGBT1のエミッタ領域106とが電気的に接続されている。電流検出用横型IGBT10のエミッタ領域108と、横型IGBT1のエミッタ領域106とが、電流検出回路7のセンス抵抗4を介して電気的に接続されている。

(もっと読む)

半導体素子評価装置及び半導体素子評価方法

【課題】半導体モジュールの生産性を向上させる。

【解決手段】絶縁ゲートを有した半導体素子をDUT11として、その動特性試験を行う半導体素子評価装置10において、DUT11の電極端子間に流れる電流を段階状に増加させながら動特性試験を行い、電極端子間に短絡が発生した直後に動特性試験を自動的に停止する半導体素子評価装置10が提供される。これにより、DUT11の電極端子間の短絡によって発生するDUT11の損傷を最小なものにし、併せてコンタクトピン12等の損傷を最小なものとすることができる。その結果、コンタクトピン等のメンテナンス労力をより低減させ、半導体モジュールの生産性を向上させることができる。

(もっと読む)

高耐圧IC

【課題】高耐圧第二領域を設け、縦型パワーデバイスの高耐圧接合終端構造、集積回路ユニット間を分離する高耐圧接合終端構造、nチャネルまたはpチャネルの高耐圧横型MOSFETの高耐圧接合終端構造などとし、配線が横切っても耐圧が低下せずに高耐圧が維持でき、かつ製造コストの低い高耐圧ICを提供すること。

【解決手段】第一の出力配線61と第二の出力配線62下の電界強度を弱めるために、GDU1を取り囲む第一の高耐圧接合終端構造HVJT1と、GDU1内およびLSU内に形成される横型MOSFETを取り囲む第二の高耐圧接合終端構造HVJT2とが同一構造の高耐圧接合終端構造HVJTで構成され、かつ一体となっている。

(もっと読む)

p型チャネルを含む炭化シリコンスイッチングデバイスおよびその形成方法

炭化シリコン内にpチャネルMOSデバイスを形成する方法は、炭化シリコン層内にn型ウェルを形成すること、および炭化シリコン層の表面のn型ウェル内にp型領域を形成するために、p型ドーパントイオンを注入することを含み、p型領域は、p型領域に隣接したn型ウェル内にチャネル領域を少なくとも部分的に画定する。チャネル領域内にしきい値調整領域が形成される。注入されたイオンは、不活性雰囲気で、1650℃よりも高温でアニールされる。チャネル領域上にゲート酸化物層が形成され、ゲート酸化物層上にゲートが形成される。炭化シリコンベースのトランジスタは、炭化シリコン層と、炭化シリコン層内のn型ウェルと、炭化シリコン層の表面のn型ウェル内のp型領域であって、p型領域に隣接したn型ウェル内にチャネル領域を少なくとも部分的に画定するp型領域とを含む。チャネル領域内にはしきい値調整領域があり、このしきい値調整領域は、p型ドーパントを、約1×1016cm-3から約5×1018cm-3のドーパント濃度で含む。このトランジスタはさらに、チャネル領域上のゲート酸化物層と、ゲート酸化物層上のゲートとを含む。このトランジスタは、チャネル領域内において、ゲート電圧−25Vで約5cm2/V−sを超える正孔移動度を示すことができる。  (もっと読む)

(もっと読む)

1 - 20 / 35

[ Back to top ]