Fターム[5F140BC19]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネルの製造 (2,860) | 前処理 (66)

Fターム[5F140BC19]に分類される特許

1 - 20 / 66

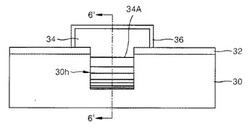

III−V族化合物半導体層を含む半導体素子及びその製造方法

【課題】III−V族化合物半導体層を含む半導体素子及びその製造方法を提供する。

【解決手段】III−V族物質を含む半導体素子及びその製造方法に係り、該半導体素子は、溝を含むシリコン基板30と、溝周囲の基板上に形成されたハードマスク32と、溝を充填する、ハードマスク上に形成された第1物質層34と、第1物質層上に形成された上部物質層36、及び上部物質層上に形成された素子層と、を含み、該第1物質層は、III−V族物質層であり、該上部物質層は、第1物質層の一部でもあり、該上部物質層は、第1物質層と同一物質または異なる物質であってもよい。

(もっと読む)

半導体装置

【課題】縦型PN接合において確実にオン/オフの制御をすることができる半導体装置を提供する。

【解決手段】半導体装置は、半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極とを備える。第1導電型の第1のチャネル領域が、ゲート絶縁膜の下にある半導体層の表面の一部に設けられている。第1導電型とは異なる導電型である第2導電型の拡散層が、第1のチャネル領域のさらに下の半導体層に設けられ、半導体層の表面に対してほぼ垂直方向に第1のチャネル領域の底部と接し、該第1のチャネル領域の底部とPN接合を形成する。第1導電型のドレインおよび第2導電型のソースが、第1のチャネル領域の両側にある半導体層内にそれぞれ設けられている。側壁絶縁膜は、第1のチャネル領域の拡散層側の側面を被覆する。

(もっと読む)

半導体装置の製造方法

【課題】レーザ光の照射を利用したエッチング加工による半導体装置の製造方法であって、複雑形状や深くて大きい除去領域等のエッチング加工が必要な広範囲の半導体装置の製造に適用可能で、高いエッチング速度が得られる半導体装置の製造方法を提供する。

【解決手段】単結晶シリコンからなる基板10に対して、焦点位置を移動させてレーザ光Lをパルス照射し、前記単結晶シリコンを部分的に多結晶化して、前記単結晶シリコン中に連続した改質層11を形成する改質層形成工程と、前記改質層11をエッチングして除去するエッチング工程と、を備える半導体装置の製造方法とする。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル移動度のような電気的特性の優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、<01−10>方向における(0−33−8)面に対するオフ角が−3°以上+5°以下である主表面2Aを有し、炭化珪素からなる基板2と、基板2の主表面2A上にエピタキシャル成長により形成され、炭化珪素からなるp型層4と、p型層4の表面に接触するように形成された酸化膜8とを備えている。そして、p型層4と酸化膜8との界面から10nm以内の領域における窒素原子濃度の最大値は1×1021cm−3以上となっている。

(もっと読む)

低周波雑音の低い微細化素子の製造法とそれを適用した集積回路製品

【課題】MOS集積回路のP型ウェーハ基板やバイポーラ集積回路のNPNトランジスタのベース領域など、N型不純物を添加する以前の下地となるP型領域形成時の特に270〜150℃の範囲の冷却には問題があり、それらの問題を解決し低周波雑音を低減し、平坦性の良い微細化PN接合界面を提供する。

【解決手段】1つ目は下地となるP型領域内の歪エネルギーを最小の状態で固定化することで、2つ目は問題となる素子の近傍に線状欠陥領域を設け、素子の重要な接合部中に発生している格子間シリコンを欠陥のIG能力で吸着せしめる。前者はMOS集積回路の場合は全ての熱処理工程の最初にP型基板を150℃16時間以上、160℃8時間以上等の条件でアニールしておく。このようにすることでP型基板に直接形成するNMOSのチャンネル雑音を低減することが出来る。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチゲート型FIN−FETにおいて、微細化に対してもFIN型トランジスタの利点を十分に発揮し、また、活性領域において十分なコンタクト面積を確保し、オン電流の低下を抑制したトレンチゲート型FIN−FETを提供する。

【解決手段】チャネル領域のFIN幅(162)を活性領域の幅(161)よりも狭くする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体素子の電気的特性へ悪影響を及ぼすことを阻止する素子分離構造を備えた半導体装置とその製造方法を提供する。

【解決手段】相対的に幅が狭い素子分離溝に残されるシリコン酸化膜9の膜厚が、相対的に幅が広い素子分離溝に残されるシリコン酸化膜9の膜厚よりも薄い。シリコン酸化膜9が薄くなった分、圧縮応力の比較的高いHDP−CVD法によるシリコン酸化膜10(上層)が、下層のシリコン酸化膜9の上により厚く積層されている。相対的に幅が狭い素子分離溝に最終的に形成される素子分離酸化膜の圧縮応力がより高められる。

(もっと読む)

高誘電率ゲート絶縁膜を備えた電界効果トランジスタを有する半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜を用いるFET及びその製造方法において、閾値電圧の制御性を向上する。

【解決手段】基板101上に高誘電率ゲート絶縁膜110、その上にゲート電極111aを形成する。少なくともゲート電極111aをマスクとして基板101にN型不純物を導入し、N型イクステンション領域113を形成する。少なくともゲート電極111aをマスクとして、基板101におけるN型イクステンション領域113の下にP型不純物を導入し、P型ポケット領域114を形成する。N型イクステンション領域113に対するN型不純物のうちのAsの導入量を、当該Asと高誘電率ゲート絶縁膜110中の元素との結合によって生じる異常な短チャネル効果が実質的に抑制される臨界点以下である範囲に設定する。臨界点は、高誘電率ゲート絶縁膜110の膜厚に基づいて算出される。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MOSFETを含む半導体装置において、プロセスフロー及び工程数を増やさずに、短チャネル効果を抑制した高耐圧MOSFETを製造する。

【解決手段】閾値電圧制御のために、チャネル形成領域に不純物のイオン注入をするとき、チャネル形成領域に、不純物導入する領域と不純物導入されない領域を設ける。上記不純物導入されない領域をうまくパターニングすることによって、ウェル領域とソース領域、及び、ウェル領域とドレイン領域それぞれの、境界近傍のチャネル形成領域における、ウェル領域と同じ導電型の不純物濃度を濃くし、逆短チャネル効果を誘起させることができる。上記の手段で誘起させた逆短チャネル効果と、短チャネル効果とを相殺させることによって、高耐圧MOSFETの短チャネル効果を抑制することができる。

(もっと読む)

減少させられたゲート電極ピッチを有する非対称トランジスタのための段階的なウエル注入

【解決手段】

洗練された半導体デバイスにおいて、非対称ウエル注入に基いて非対称トランジスタ構造が得られる一方で傾斜注入プロセスは回避し得る。この目的のために、段階的なレジストマスクのような段階的な注入マスクが形成されてよく、段階的な注入マスクは、非対称トランジスタのソース側と比較してドレイン側で高いイオン遮断能力を有していてよい。例えば、非対称構造は、高度な性能向上を伴う非傾斜注入プロセスに基いて得ことができ、また考慮されている技術標準にかかわりなく完成され得る。

(もっと読む)

半導体装置およびその製造方法

【課題】 エッチング処理を行わなくても、基底面内転位を有する半導体層から結晶成長された半導体層に基底面内転位が伝播することを防止することができる技術を提供する。

【解決手段】 本発明の方法は、半導体層2の表面2aにおける基底面内転位6の位置8を特定する特定工程と、特定工程で特定された位置8において結晶の再配列を行う結晶再配列工程と、結晶再配列工程の後に表面2aから半導体層を結晶成長させる結晶成長工程とを備えている。本発明によると、結晶成長された半導体層に基底面内転位6が伝播しない。基底面内転位6が結晶成長された半導体層に伝播していないために、リーク電流を抑えることができる。

(もっと読む)

III族窒化物系化合物半導体素子及びその製造方法

【課題】積層された各層に平面的に電極が形成された、III族窒化物系化合物半導体素子

【解決手段】pnpトランジスタ100は、基板10の上に、図示しないバッファ層を介して、p型GaN層11、n型GaN層12、p型GaN層13を順に形成した後、ケミカルポリシングにより露出部である傾斜面11t、12t及び13tを形成し、そこに各々、コレクタ電極C、ベース電極B、エミッタ電極Eを形成して構成したものである。図1のpnp型トランジスタ100は、水平形状が1辺が500μmの矩形状で、その外周の1辺に水平面と10度の角度を成す傾斜面が形成されている。p型GaN層11、n型GaN層12及びp型GaN層13の膜厚はいずれも1μmであり、p型GaN層11の傾斜面11t、n型GaN層12の傾斜面12t及びp型GaN層13の傾斜面13tの幅はいずれも約5.8μmである。

(もっと読む)

半導体装置およびその製造方法

【課題】STI構造の素子分離を行う場合にソース/ドレイン領域の形成時点で半導体基板に対する転位の発生を抑制できるようにする。

【解決手段】素子分離絶縁膜3を活性領域2との間の接触領域においてシリコン基板1の表面の高さよりも深く且つソース/ドレイン領域1bのピーク濃度となる高濃度不純物拡散領域1bの形成深さd4(もしくはPN接合部)よりも浅い高さに位置し、当該領域よりも外方領域に遠ざかるに連れて深さd4よりも深い深さd2に位置するように形成する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成された所定の導電型を有する半導体層と、エピタキシャル成長によって前記半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、前記所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によって前記ドレイン電極側のコンタクト層と前記半導体層との間にゲート絶縁膜を介してゲート電極と重畳するように形成された、前記所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、を備える。

(もっと読む)

半導体装置

【課題】同一基板上に複数のトランジスタを備え、各トランジスタの動作特性を劣化させることなく、各々に適切な閾値電圧を設定することのできる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、素子分離領域2により分離された第1および第2のトランジスタ領域10、20を有する半導体基板1と、第1および第2のトランジスタ領域10、20において、半導体基板上1に形成された不純物拡散抑制層12、22と、不純物拡散抑制層12、22上に形成されたエピタキシャル結晶層13、23と、を有し、不純物拡散抑制層22の厚さは、不純物拡散抑制層12の厚さよりも厚く、チャネル領域11に含まれる導電型不純物は、エピタキシャル結晶層13中の領域における濃度が、半導体基板1中の領域における濃度よりも低く、チャネル領域21に含まれる導電型不純物は、エピタキシャル結晶層23中の領域における濃度が、半導体基板1中の領域における濃度よりも低い。

(もっと読む)

半導体デバイスの製造方法およびその半導体デバイス

【課題】フィンの角を丸み付けし、フィンの側壁面を円滑化できる半導体デバイスの製造方法を提供する。

【解決手段】半導体デバイスの製造方法は、半導体材料を含む基板を用意するステップと、上面、少なくとも1つの側壁面および少なくとも1つの角を備える少なくとも1つのフィンを前記基板にパターン形成するステップと、少なくとも1つのフィンに、熱力学平衡におけるフィンでの点欠陥の密度より大きい点欠陥の密度である点欠陥の過飽和を生成するステップと、少なくとも1つのフィンをアニールして、続いて冷却し、これにより半導体材料の半導体原子が点欠陥を介してマイグレーションを行うようにしたステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に応力を印加して、チャネル領域に歪みを与えるための新たな手法を提供する。

【解決手段】基板と、前記基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極の側面に設けられた側壁絶縁膜と、前記基板のソースドレイン領域に埋め込まれており、前記基板のチャネル領域に応力を印加する応力印加層であって、前記基板と前記応力印加層との界面の上端の高さが、前記基板と前記ゲート絶縁膜との界面の下端の高さよりも高いような応力印加層と、を備えることを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の注入量及びチャネル領域中の不純物濃度を容易に制御する。動作特性に優れたFin型電界効果型トランジスタを備えた半導体装置を提供する。

【解決手段】Fin状の半導体基板の部分に犠牲酸化膜を形成した後、マスクパターンをマスクに用いて半導体基板に不純物を注入する。この後、犠牲酸化膜を除去して、半導体基板を露出させた後、露出した半導体基板上にゲート絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高い平坦性の素子分離領域を得ることを課題とする。

【解決手段】トレンチ領域形成用のマスクとしての第1絶縁膜を半導体基板の直上に形成する工程と、マスクを用いて半導体基板にトレンチ領域を形成する工程と、トレンチ領域を含む半導体基板及び第1絶縁膜の直上に第2絶縁膜を形成することで、トレンチ領域上の第2絶縁膜からなる凹部と、第1絶縁膜上の第2絶縁膜からなる凸部と得る工程と、凹部の底面まで凸部を構成する第2絶縁膜を除去する第1除去工程と、第1絶縁膜及び第2絶縁膜を所定の膜厚まで化学的機械研磨法により除去することで、凹部及び凸部より形成された段差を20nm以下に低減する第2除去工程とを含み、第1絶縁膜及び第2絶縁膜が、同一の化学的機械研磨条件で研磨レートに差がない絶縁膜からなり、第2除去工程が、0.2〜0.6重量%の研磨粒子を含むスラリーを用いて行なわれることを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

1 - 20 / 66

[ Back to top ]