Fターム[5F140BD13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート絶縁膜 (8,730) | 材料 (6,782) | 金属酸化膜 (2,702) | 複合金属酸化膜 (873)

Fターム[5F140BD13]に分類される特許

861 - 873 / 873

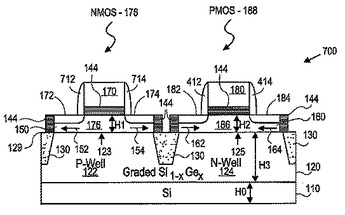

CMOS用歪トランジスタの集積化

【解決手段】CMOSデバイスに関連する本発明の様々な実施形態は、(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

(もっと読む)

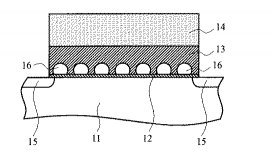

乱数生成素子

【課題】 増幅回路を用いなくても1Mbit/s以上の乱数生成レートが可能となるような物理現象中のランダムノイズを利用した乱数生成素子を提供することを目的とする。

【解決手段】 半導体表面との間で非常に薄いトンネル絶縁膜を介して電子の充放電が可能な導電性微粒子をチャネル上に設け、チャネル幅Wを狭く、かつ導電性微粒子の面密度Ddotを多く、かつチャネル〜導電性微粒子間のトンネル抵抗を小さくする。例えば、膜厚0.8nmのシリコン窒化膜をトンネル絶縁膜とするバルク基盤上の素子の場合、チャネル幅W=0.1μm、平均粒径d=8nm程度のSi微結晶粒子群を1.7×1012cm−2程度の面密度で形成すると、1MHzのノイズ成分を0.1%にできる。

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

シリコン基板(101)上に、RTO法によりシリコン酸化物からなる下地層(103)を形成する。このとき、下地層(103)の膜厚を1.5nm以上とする。次に、下地層(103)上に、CVD法によりハフニウム窒化物を0.5乃至1.0nmの厚さに堆積させ、金属化合物層(104)とする。次に、水素雰囲気中において熱処理を施し、金属化合物層(104)から下地層(103)中にハフニウム元素を拡散させてシリケート化させ、ゲート絶縁膜(106)を形成する。その後、酸化雰囲気中において熱処理を行う。このとき、シリコン基板(101)とゲート絶縁膜(106)との界面には、ハフニウム元素が到達しないようにする。  (もっと読む)

(もっと読む)

等方性エッチングプロセスを使ったショットキーバリアMOSFET製造方法

【課題】電流の流れを調整するトランジスタデバイスの組立て方法において、更なる駆動電流を可能にし、デバイスの動作を最適化するプロセスを提供すること。

【解決手段】本発明の一実施形態における方法は、チャンネル領域に対するショットキーバリア接合位置のより良い制御を与えるために、メタルソースドレイン接触の形成に先行して等方性エッチングプロセスを利用する。このショットキーバリア10接合の配置の制御性からの改善により、更なる駆動電流を可能にし、デバイスの動作を最適化する。

(もっと読む)

同じ半導体チップ内のPMOSおよびNMOSトランジスタの薄いゲート誘電体を個々に最適化する方法、およびそれによって製造されたデバイス

【課題】半導体基板(12)に形成され、シリコン酸化物およびそれの異なる程度の窒化(18Dと18E)で構成されたPFETゲート誘電体層(16)およびNFETゲート誘電体層(14)でそれぞれ覆われたPFET領域およびNFET領域を有するCMOS半導体(10)材料を形成する方法を提供すること

【解決手段】シリコン基板(12)にPFET領域(16)およびNFET領域(14)を設け、その上にPFETおよびNFETゲート酸化物層を形成する。PFET領域の上のPFETゲート酸化物層の窒化を行って、PFET領域の上のPFETゲート酸化物層に、第1の濃度レベルの窒素原子を有する、PFET領域の上のPFETゲート誘電体層(42)を形成する。NFETゲート酸化物層の窒化を行って、第1の濃度レベルと異なる濃度レベルの窒素原子を有する、NFET領域の上のNFETゲート誘電体層(40)を形成する。NFETゲート誘電体層(40)およびPFETゲート誘電体層(42)は、同じ厚さを有することができる。

(もっと読む)

ハフニウムベースの高誘電率誘電体の原子層堆積

ハフニウムベースの誘電体膜を堆積する方法が提供される。本方法は、オゾンとハフニウム前駆体を含む1つ又はそれ以上の反応物質とを用いた原子層堆積段階を含む。半導体デバイスもまた提供される。該デバイスは、基板と、基板上に形成されたハフニウムベースの誘電体層と、基板及びハフニウムベースの誘電体層間に形成された界面層とを含み、該界面層は二酸化ケイ素を含み且つ結晶構造を有する。 (もっと読む)

高度に均一な酸化物層、とりわけ超薄層の調節された成長

【課題】高度に均一性の酸化物層、とりわけ超薄層の調節された成長方法を提供する。

【解決手段】本発明は、高水準の均一性を持つ酸化物層、とりわけ超薄層の作成方法に関するものである。このような方法の一つは、実質的に飽和された又は飽和された酸化物層を、半導体基材の半導体表面上に直接又は間接的に形成する段階、及び前記実質的に飽和された又は飽和された酸化物層の厚さをエッチングにより減少させる段階であって、エッチングされた酸化物層が前記実質的に飽和された又は飽和された酸化物層より薄い厚さを有するような量だけ減少させる段階を含む。特定の実施態様において、本発明の方法は、約±10%未満の均一性を持つエッチングされた酸化物層を提供する。本発明はまた、本発明の方法により作成されてなるミクロ電子デバイス、及び本発明の方法を実施するための製造システムに関するものである。

(もっと読む)

自己制限的界面酸化による超極薄酸化物層および酸窒化物層の形成。

【課題】 自己制限的界面酸化による超極薄酸化物層および酸窒化物層の形成の提供。

【解決手段】 超極薄酸化物層および酸窒化物層は、基板の自己制限的酸化を達成するように、および超極薄酸化物並びに酸窒化物を提供するように、低圧プロセスを利用して形成される。被処理基板は、酸化物層、酸窒化物層、窒化物層、およびhigh−k層のような初期の誘電体層を含むことができるか、あるいは、初期の誘電体層をなくすことができる。プロセスは、バッチ型処理チャンバを使用するか、あるいは、単一のウェーハ処理チャンバを使用することによって、実行されることができる。本発明の一実施例は、厚さ約15ÅのSiO2層をもたらす、Si基板の自己制限的酸化を提供し、そこにおいて、SiO2層の厚さは、基板にわたって約1Å未満で変化する。

(もっと読む)

半導体装置及びその製造方法

Si(100)基板の表面にシリコン酸化膜を形成した後、このシリコン酸化膜をプラズマ窒化して酸窒化シリコン膜にする。その後NOガス雰囲気中で770乃至970℃の温度条件下で熱処理することにより、ゲート絶縁膜における基板との界面部分の窒素濃度を1乃至10原子%にすると共に、基板と酸窒化シリコン膜との界面に存在する界面Si結合欠陥の結合手の方位角分布が、基板の[100]方位に対して25°以上の角度にピークをもつようにする。 (もっと読む)

振幅変調された高周波エネルギーを使用してゲート誘電体をプラズマ窒化するための方法及び装置

窒化ゲート誘電体層を形成するための方法及び装置。この方法は、電子温度スパイクを減少するために、滑らかに変化する変調のRF電源により処理チャンバー内に窒素含有プラズマを発生することを含む。電源が滑らかに変化する変調のものであるときには、方形波変調のものに比して、電界効果トランジスタのチャンネル移動度及びゲート漏洩電流の結果が改善される。 (もっと読む)

多成分誘電体膜を形成するためのシステム及び方法

【課題】半導体用途における誘電体膜を形成するためのシステム及び方法、特に、混合気化前駆体を用いて基板上に多成分誘電体膜を作製するためのシステム及び方法を提供する。

【解決手段】本発明は、気化した前駆体の混合物が、原子層堆積(ALD)処理における単一パルス段階中にチャンバ内に一緒に存在して多成分膜を形成するような気化前駆体の混合をもたらすためのシステム及び方法を提供する。気化前駆体は、少なくとも1つの異なる化学成分から成り、そのような異なる成分が単層を形成して多成分膜を生成することになる。本発明の更に別の態様では、組成勾配を有する誘電体膜が提供される。

(もっと読む)

861 - 873 / 873

[ Back to top ]