Fターム[5F140BF42]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 形状、配置 (2,388) | 断面形状 (1,038)

Fターム[5F140BF42]の下位に属するFターム

溝掘りゲート (564)

Fターム[5F140BF42]に分類される特許

461 - 474 / 474

エレベイテッドサリサイドソース/ドレイン領域の形成方法、および半導体素子

【課題】エレベイテッドサリサイドソース/ドレイン領域の形成方法及びT型素子分離膜を有する半導体素子を提供する。

る。

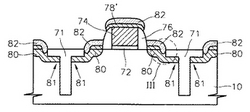

【解決手段】本発明に係るエレベイテッドサリサイドソース/ドレイン領域80の形成方法には、拡幅トレンチ領域の深さを調節することによってソース/ドレイン領域80を形成するためのイオン注入段階で、前記T型素子分離膜71のヘッド部を構成し、前記狭幅トレンチ領域の上端部から左右側に延長された前記拡幅トレンチ領域の下部81にも導電型不純物を注入可能にする。

(もっと読む)

非対称なヘテロドープされた高電圧のMOSFET(AH2MOS)

非対称なヘテロドープされた金属酸化物(AH2MOS)半導体デバイスは基板と、前記基板の頂部にあってソース領域とドレイン領域との間に配置された絶縁ゲートと、からなる。ゲートの一方の側面には、ヘテロドープされたタブ及びソース領域が形成されている。タブ領域は第2極性のドーパントを有している。ソース領域が各タブ領域内に配置されており、第2極性と反対の第1極性のドーパントを有している。ゲートの他方の側面には、ヘテロドープされたバッファ及びドリフト領域が形成されている。バッファ領域は第2極性のドーパントからなる。ドリフト領域がバッファ領域内に配置され、第1極性のドーパントによってドーピングされている。ドレインn+タップ領域がドリフト領域内に配置されている。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート直下のpウェルとnウェルとの接合近傍のnウェル濃度を高めること。pウェルの直下におけるnウェルの不純物量および厚さを増加させ、ハイサイドスイッチに適した高いパンチスルー耐圧を得ること。

【解決手段】p型半導体基板1の表面層にnウェル2が形成され、nウェル2内にn+ドレイン領域8とpウェル3が形成され、pウェル3内にn+ソース領域4が形成され、pウェル3の、n+ソース領域4とnウェル2とに挟まれた部分の表面上にゲート酸化膜6を介してゲート電極7が形成された横型MOSFETにおいて、pウェル3を内包するように第2のnウェル13を形成し、ゲート直下のpウェル3とnウェル2との接合近傍におけるn型不純物濃度を高くするとともに、pウェル3の直下におけるn型半導体領域の不純物量と厚さを増加させる。

(もっと読む)

半導体装置

【課題】高耐圧化と低オン抵抗化を図ることができる半導体装置を提供する。

【解決手段】半導体基板1上に形成されたpウエル領域であるP−well35と、このP−well35の表面層に形成されるpオフセット領域であるP−off5と、P−off5の表面からP−well35に達するように形成したトレンチ19と、このトレンチ19の側壁にゲート酸化膜20を介して形成したゲート電極21と、トレンチ底に形成した拡張ドレイン領域である拡張ドレイン領域であるN−body6と、このN−body6と接するようにトレンチ19内部上方に向かって形成されたドレイン領域となるnエピタキシャル層30と、Pwell35の表面層に形成したソース領域となる上部のn+ 領域8とで構成する。この構成では、タングステン層23を形成する箇所にドレイン領域となるnエピタキシャル層30を形成するために、トレンチ19を広げることなく、ゲート電極21とドレイン領域となるnエピタキシャル層30の間隔を広げることができるために、高耐圧化と、低オン抵抗化を図ることができる。

(もっと読む)

メモリデバイス、トランジスタ、メモリセル並びにそれらの製造方法

メモリデバイスはメモリセルのアレイと周辺デバイスを含んでいる。少なくとも一部の個別メモリセルはSiCを含む炭酸化部分を含んでいる。少なくとも一部の周辺デバイスは炭酸化部分を含まない。トランジスタは第1ソース/ドレーン、第2ソース/ドレーン、第1ソース/ドレーンと第2ソース/ドレーンとの間にSiCを含む半導体基板の炭酸化部分を含んだチャンネル、及びチャンネルの両側と作動式に関係するゲートを含んでいる。 (もっと読む)

半導体装置およびその製造方法

【課題】厚み均一で且つ低抵抗のシリサイド層をゲート電極に有する半導体装置およびその製造方法を提供する。

【解決手段】シリサイド化する高融点金属の堆積前に、ゲート電極上面に角が発生しないように端部丸めを実施した後にシリサイド化を行ことで、熱処理時に発生する膜応力の集中を緩和し、均一でかつ十分な厚さのシリサイド層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 ダマシンゲートトランジスタのゲート絶縁破壊を抑制し、デバイスの信頼性を確保することのできる半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1の上に、犠牲ゲート絶縁膜104および犠牲ゲート電極105を形成した後、犠牲ゲート電極105の側面に第1の側壁膜106を形成する。次に、第1の側壁膜106を介して、犠牲ゲート電極105の側面に、第1の側壁膜106とエッチングレートの異なる第2の側壁膜110を形成する。ここで、第1の側壁膜106の膜厚は、犠牲ゲート絶縁膜104の膜厚より厚くなるようにする。これにより、第1の側壁膜106および犠牲ゲート絶縁膜104をウェットエッチングする際のプロセスマージンを大きくして、第2の側壁膜110のゲート電極側下部にスリットが入るのを防ぐことができる。

(もっと読む)

半導体装置

【課題】 ゲート−ドレイン間の容量が小さく、尚且つ、オン抵抗の低いパワー半導体装置を提供する。

【解決手段】

半導体装置100は、N型の半導体層20と、半導体層20の表面に形成されたP型のソース30およびP型のドレイン40と、ソース30とドレイン40との間のチャネル領域上にゲート絶縁膜60を介して設けられたゲート電極70であって、チャネル領域のチャネル長方向の長さがLgであるゲート電極70と、チャネル領域にイオン注入して形成されたボディ領域80であって、深さがXj、ゲート絶縁膜60を介してゲート電極70と対向するイオン注入された部分のチャネル長方向の長さがLaであるボディ領域80とを備え、La≦Lg−Xjを満たすことを特徴とする。

(もっと読む)

半導体構造、メモリ素子構造、及び半導体構造の形成方法

本発明は、垂直のソース/ドレイン領域(88)を囲むゲート線格子(94)を有する半導体構造(10)を含む。ある側面では、ソース/ドレイン領域は、ペアで提供され、各ペアのソース/ドレイン領域のうちの1つがディジットライン(120、122)に延伸し、もう1つのソース/ドレイン領域がキャパシタのようなメモリストレージ素子(145)に延伸してDRAMを形成することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子(145)に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに半導体構造を形成する方法を含む。典型的な方法では、第1の材料を含む格子は第2の材料の繰り返し領域を囲むように提供される。その後、前記第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、本発明のうちの少なくとも一部は、垂直のソース/ドレイン領域を囲むゲート線格子を有する半導体構造を含む。ある側面では、ソース/ドレイン領域はペアで提供され、各ペアのソース/ドレイン領域のうちの1つはディジットラインまで延伸し、もう1つのソース/ドレイン領域はキャパシタのようなメモリストレージ素子まで延伸することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに、第1の材料を含む格子が第2の材料の繰り返し領域を囲むように提供される方法を含む。その後、第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、第2の材料のうちの少なくとも一部は垂直のソース/ドレイン領域で置換される。  (もっと読む)

(もっと読む)

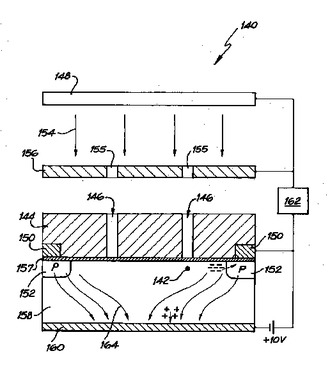

注入され計数されたドーパントイオン

本発明は、実質的に真性な半導体の基板(158)の領域に注入された、計数された数のドーパントイオン(142)を有する汎用タイプの半導体装置に関する。基板(158)の一つ以上のドープされた表面領域は、金属化され、電極(150)が形成される。計数された数のドーパントイオン(142)が、実質的に真性な半導体の領域に注入される。

【その他】

原文には、請求項11及び請求項11Aが存在する。請求項11Aは、オンライン手続上、請求項11内に記載した。

(もっと読む)

(もっと読む)

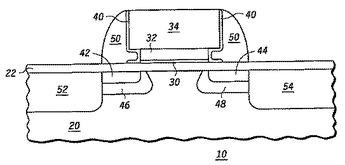

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

トライゲートトランジスタ及びその製造方法

本発明の実施形態は、均一なシリコンボディ高さをもたらすSOIトランジスタの製造方法を提供する。一実施形態では、犠牲酸化物層が半導体基板上に配置される。酸化物層はトレンチを形成するようにエッチングされ、トレンチは半導体材料で充填される。そして、半導体材料は酸化物層の残部を用いて平坦化され、その後、酸化物層の残部は除去される。こうして露出された半導体フィンは仕様の許容範囲内で均一な高さを有する。  (もっと読む)

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

窒化ガリウム材料デバイスおよびその形成方法を提供する。該デバイスは、電極規定層を包含する。電極規定層は典型的にはその内部に形成されたビアを有し、該ビア内に電極が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。 (もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

461 - 474 / 474

[ Back to top ]