Fターム[5F140BG26]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666)

Fターム[5F140BG26]の下位に属するFターム

堆積 (2,821)

不純物の導入 (644)

熱処理 (1,248)

ゲート電極の形状を形成する方法 (2,844)

Fターム[5F140BG26]に分類される特許

101 - 109 / 109

半導体装置の製造方法

【課題】 未反応の高融点金属膜等を確実にエッチング除去することが可能な半導体装置の製造方法を提供する。

【解決手段】 ソース/ドレイン用の拡散層34n、34pを有する被処理基板を用意する工程と、被処理基板上に高融点金属膜を形成する工程と、拡散層と高融点金属膜との反応によってシリサイド膜52n、52pを形成する工程と、シリサイド膜を形成する工程において拡散層と反応せずに残った未反応の高融点金属膜51aを除去する工程とを備え、未反応の高融点金属膜を除去する工程は、硫酸液中にバブリングによってオゾンが導入されたエッチング液を用いて行われる。

(もっと読む)

ゲート及びチャネル内に歪を誘起させてCMOSトランジスタの性能を向上させる方法

【課題】 ゲート内の応力を調節することによってトランジスタ・チャネル内に歪を誘起させること。

【解決手段】 相補型金属酸化物半導体トランジスタを製造する方法は、異なる型のトランジスタ、例えばN型金属酸化物半導体(NMOS)トランジスタ及びP型金属酸化物半導体(PMOS)トランジスタ(第1及び第2型トランジスタ)を基板(12)上に形成する。この方法は、これらのNMOSトランジスタ及びPMOSトランジスタ上に任意の酸化物層を形成し、次いでNMOSトランジスタ及びPMOSトランジスタを硬い材料(50)、例えば窒化ケイ素層で覆う。この後、この方法は、この硬い材料層(50)の一部をパターン形成し、硬い材料層がNMOSトランジスタ上にのみ残るようにする。次に、この方法は、NMOSトランジスタを加熱し(178、204)、次いで硬い材料層(50)の残存部分を除去する。PMOSトランジスタ(PFET)のゲート(20)又はチャネル領域内に応力を生じさせることなく、NMOSトランジスタ(NFET)のゲート(22)内に圧縮応力、チャネル領域内に引張応力(70)を生じさせることによって、この方法は、PFETの性能を低下させることなく、NFETの性能を改善する。

(もっと読む)

ドープされたチタン酸ボディを有するMOS(Metal−Oxide−Semiconductor)デバイス

単結晶のチタン酸ストロンチウム又はチタン酸バリウム(10)のボディを有するMOS(Metal-Oxide-Semiconductor)デバイスが提供され、ボディは、絶縁領域に隣接するドープされた半導体領域(24)を備えている。ボディは、絶縁領域により、半導体領域から分離した、ドープされた導通領域を、さらに備えていてもよい。様々な手法でドープされた場合の単結晶チタン酸ストロンチウムの材料特性は、MOSスタックの絶縁構成部、導通構成部、及び、半導体構成部を提供するために、用いられる。有利なことに、単一のボディを用いることにより、スタック構成部の間のインターフェースレイヤの存在を回避することができ、電界効果トランジスタなどのMOSデバイスの特性を改善する。  (もっと読む)

(もっと読む)

FETにおける埋め込みバイアス・ウェル

【課題】 リーク電流及び接合キャパシタンスを除去又は減少させるために、半導体デバイスにおける新規な構造体を提供する。

【解決手段】 半導体装置の構造体及び該構造体を製造するための方法が開示される。半導体構造体は、第1及び第2のソース/ドレイン領域、該第1及び第2のソース/ドレイン領域の間に配置されたチャネル領域、該チャネル領域と物理的に接する埋め込みウェル領域、該埋め込みウェル領域と該第1のソース/ドレイン領域との間に配置され、かつ、該埋め込みウェル領域と該第2のソース/ドレイン領域との間に配置される埋め込みバリア領域とを含み、該埋め込みバリア領域が、該埋め込みウェル領域と該第1のソース/ドレイン領域との間のリーク電流及びドーパント拡散、並びに該埋め込みウェル領域と該第2のソース/ドレイン領域との間のリーク電流及びドーパント拡散を防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

絶縁ゲート型電界効果トランジスタの製法

【課題】微細なゲート電極を有するLDD(Lightly Doped Drain)構造の絶縁ゲート型電界効果トランジスタを製造する方法において、製造歩留りを向上させる。

【解決手段】P型ウェル領域14の表面に素子孔を有するフィールド絶縁膜16を形成した後、素子孔内の半導体表面にゲート絶縁膜20を形成する。絶縁膜20の上に破線で示すようにポリシリコン等のゲート電極層24を形成した後、電極層24及び絶縁膜20の積層と絶縁膜16とをマスクとするイオン注入処理によりN+型ソース領域28及びN+型ドレイン領域30を形成する。等方性エッチング処理により電極層24を実線で示すように細く且つ薄くした後、電極層24及び絶縁膜20の積層と絶縁膜16とをマスクとするイオン注入処理によりN−型ソース領域32及びN−型ドレイン領域34を形成する。

(もっと読む)

ボイドのないゲート電極を具備したトランジスタの製造方法

【課題】 ボイドのないゲート電極を具備したトランジスタの製造方法を提供する。

【解決手段】 半導体基板上にゲート酸化膜を形成した後、前記ゲート酸化膜の上部にゲート電極用ポリシリコン膜を蒸着する。次いで、前記ポリシリコン膜にp型不純物をイオン注入し、前記ポリシリコン膜の所定厚さほどを化学機械的研磨方法で除去する。

(もっと読む)

半導体装置及びかかる半導体装置の製造方法

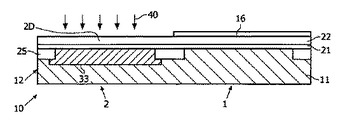

本発明は、金属及び更なる元素の両方を含有する化合物を含むゲート領域(1D、2D)を有するNMOST1及びPMOST2を備えるCMOSデバイス(10)に関する。本発明によれば、第1及び第2導電材料はいずれも、モリブデン及びタングステンを含むグループから選択される金属を前記金属として含む化合物を備えると共に、炭素、酸素、カルコゲナイドを含むグループから選択される元素を前記更なる元素として含んでいる。第1及び第2導電材料はいずれも、モリブデン及び炭素または酸素から成る化合物を含むことが好ましい。また本発明は、かかるデバイスを製造する魅力的な方法も提供する。  (もっと読む)

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

101 - 109 / 109

[ Back to top ]