Fターム[5F140BG26]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666)

Fターム[5F140BG26]の下位に属するFターム

堆積 (2,821)

不純物の導入 (644)

熱処理 (1,248)

ゲート電極の形状を形成する方法 (2,844)

Fターム[5F140BG26]に分類される特許

21 - 40 / 109

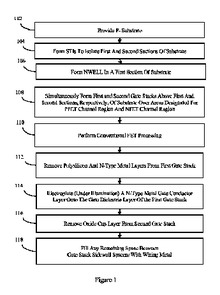

半導体デバイスを形成する方法

【課題】 ボイドフリーかつシームフリーの金属ゲート導体層が比較的薄い高kゲート誘電体層の上に位置決めされている少なくとも1つの高アスペクト比ゲート構造を有する相補型金属酸化膜半導体(CMOS)デバイスを形成する方法を提供する。

【解決手段】 これらの方法実施形態は、高アスペクト比ゲート・スタック開口部を下から上に金属ゲート導体層で充填するために電気メッキ・プロセスを使用するゲート交換戦略を取り入れている。電気メッキ・プロセス用の電子の発生源は、基板の裏面を直接通過する電流である。これは、シード層の必要性を排除し、ボイドまたはシームなしで金属ゲート導体層が形成されることを保証するものである。さらに、実施形態次第で、電気メッキ・プロセスは、所与の領域への電子流を増強するために(すなわち、メッキを増強するために)照明を受けて実行され、所与の領域への電子流を防止するために(すなわち、メッキを防止するために)暗闇で実行される。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタのゲート電極、及びp型MISトランジスタのゲート電極の双方を精度良く実現する。

【解決手段】第1のMISトランジスタと第2のMISトランジスタとを備えた半導体装置において、第1のMISトランジスタは、半導体基板10における第1の活性領域10a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成され、シリコン膜14aとシリコン膜14a上に形成された第1の金属シリサイド膜20aとからなる第1のゲート電極26aとを備え、第2のMISトランジスタは、半導体基板10における第2の活性領域10b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜13b上に形成され、フルシリサイド化された第2の金属シリサイド膜20Bからなる第2のゲート電極26bとを備え、第1の金属シリサイド膜20aは、第2の金属シリサイド膜20Bに比べて膜厚が薄い。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、NiSiの潜り込み成長を抑え、オフリーク電流の増加を抑制できる半導体装置を提供することを目的とする。

【解決手段】本発明の1実施形態は、シリコン基板1上に形成されるソース領域及びドレイン領域と、ソース領域とドレイン領域との間にゲート絶縁膜3を介して形成されるゲート領域とを備える半導体装置である。さらに、本発明の1実施形態は、少なくともソース領域及びドレイン領域上に成膜した所定の添加金属を含むニッケル膜10を、Ni2Si膜へと反応させる温度でアニールし、さらにNiSi膜へと反応させる温度でアニールして形成されたシリサイド膜22を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、EOTの増膜が抑制され、且つ、良好な品質を有する高誘電率膜を備えた信頼性の高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、半導体基板1内に形成された第1導電型の第1の領域3及び第2導電型の第2の領域4と、半導体基板1上であって、第1の領域3及び第2の領域4の上に形成されたゲート絶縁膜5と、ゲート絶縁膜5上に形成された保護膜6と、保護膜6のうち第1の領域3の上に設けられた部分上に形成され、金属からなる第1のゲート電極9と、保護膜6のうち第2の領域4の上に設けられた部分上に形成された第2のゲート電極12とを備えている。ゲート絶縁膜5及び保護膜6は、高誘電率膜からなる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、FIN状の半導体部やゲート電極を精度良く形成すること、又は素子間の特性バラツキを改善することで、特性の優れたFIN型トランジスタを備える半導体装置を提供することを目的とする。

【解決手段】本発明は、一方にソース領域、他方にドレイン領域が形成されたFIN状の半導体部10と、ソース領域とドレイン領域との間で、FIN状の半導体部10をゲート絶縁膜を介して囲むように形成されたゲート電極17とを備える半導体装置である。そして、本発明に係る1つ解決手段は、ゲート電極17が、ウェットエッチング可能なメタル材料又はシリサイド材料を用いている。

(もっと読む)

半導体装置およびその製造方法

【課題】金属シリサイド膜の膜厚が薄くなってきたり、拡散層幅が小さくなってくると、拡散層上の金属シリサイドが凝集反応を起こしやすくなる、という問題があった。

【解決手段】半導体装置100は、半導体基板2と、半導体基板内に設けられた拡散層4と、半導体基板上に設けられたゲート絶縁膜12と、ゲート絶縁膜上に設けられたゲート電極14と、拡散層上に選択的に設けられたNiシリサイド層8と、を含み、Niシリサイド層8上にはCoを主成分とするメタルキャップ膜18が選択的に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

半導体製造装置及び半導体装置の製造方法

【課題】基板上の表面角の異なる領域を選択的に局所加熱することができる半導体製造装置を提供する。

【解決手段】第1の領域と前記第1の領域と面方位が異なる第2の領域が形成された基板6の前記第2の領域へ偏光した光を入射する照射部1〜5と、前記第2の領域からの前記偏光した光の反射光が入射される回転検光子8と、回転検光子8を介して前記反射光を受光し、前記反射光の強度を検出する光検出器9と、回転検光子8の回転角度及び前記検出された強度に基づいて前記第2の領域の屈折率を算出する解析部10と、基板6へレーザを照射するレーザ照射部12、13と、前記屈折率に基づいて前記第2の領域のブリュースター角を求め、前記第2の領域の表面に前記ブリュースター角で前記レーザが入射するようにレーザ照射部12、13を制御するコントローラ11と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、各ゲートについて均一で十分なフル・シリサイド化を実現する、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極の表層部分及びソース/ドレイン領域16a,16bの表層部分がシリサイド化されている状態において、半導体基板1にフラッシュランプアニールを施す。この処理により、ソース/ドレイン領域16a,16bには(NiPt)2Si層19bが形成された状態が保持されて、ゲート電極のみが選択的にフル・シリサイド化され、フル・シリサイドゲート電極21が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】コストを低減した半導体装置を提供する。

【解決手段】半導体基板100表面部にチャネル領域101を挟むように形成された拡散層102と、チャネル領域101上に形成されたゲート絶縁膜103を有し、N型MOSFETのゲート電極104は第1のニッケルシリサイド層104a及び第1のニッケルシリサイド層104a上に形成され第1のニッケルシリサイド層104aよりニッケル含有率が高い第2のニッケルシリサイド層104bからなり、P型MOSFETのゲート電極104は第2のニッケルシリサイド層104bよりニッケル含有率が高い第3のニッケルシリサイド層からなる。

(もっと読む)

半導体装置とその製造方法

【課題】絶縁膜を研磨せずに、該絶縁膜からゲート電極の上面を露出させることが可能な半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板1の上にゲート絶縁膜5を形成する工程と、ゲート絶縁膜5の上にゲート電極7aを形成する工程と、ゲート電極7aを覆うように液状の絶縁性材料20を塗布する工程と、絶縁性材料20に鋳型100を押し当てることにより、ゲート電極7aの上方の絶縁性材料20を押し流す工程と、絶縁性材料20を硬化して絶縁膜21にする工程と、硬化の後、ゲート電極7a上に高融点金属膜を形成する工程と、高融点金属膜をアニールすることにより、ゲート電極7aの全体をシリサイド化する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型トランジスタとPNゲートで構成されるプレーナ型トランジスタとが共存する半導体装置において、溝型トランジスタの溝ゲートの空乏化現象によるオン電流の低下を抑制し、溝型トランジスタと異なる導電型のP又はNゲートで構成されるプレーナ型トランジスタの閾値電圧のバラツキ増加を防止する。

【解決手段】溝型トランジスタのゲート電極であるポリシリコン膜中に高濃度不純物拡散材料9が埋設された構造を有する。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極の側壁絶縁膜のエッチングを効果的に防止することが可能な半導体装置を提供する。

【解決手段】 半導体基板11と、半導体基板上に形成されたゲート絶縁膜13と、ゲート絶縁膜上に形成されたゲート電極22と、ゲート電極の側面に形成された第1の絶縁膜17と、第1の絶縁膜の表面を覆い、第1の絶縁膜とは異なった材料で形成された第2の絶縁膜28と、半導体基板、ゲート電極及び第2の絶縁膜を覆い、第2の絶縁膜とは異なった材料で形成された第3の絶縁膜23とを備える。

(もっと読む)

半導体装置の製造方法

【課題】酸化シリコンより比誘電率の高い酸化物を含んで構成されるゲート絶縁膜を備えたMISトランジスタのトランジスタ特性を向上する。

【解決手段】基板SUBの主面上に酸化ハフニウムから構成される高誘電体層HK1を形成した後、基板SUBの主面を非酸化性雰囲気中で熱処理する。次いで、高誘電体層HK1上に、ALD法によって堆積された酸化ハフニウムから構成され、かつ、高誘電体層HK1より薄い酸素供給層HK2を形成し、さらに、窒化タンタルから構成されるキャップ層CLを形成した後、基板SUBの主面を熱処理する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲート電極の全領域がシリサイド化されたMISトランジスタを備える半導体装置の性能を向上させる技術を提供する。

【解決手段】MISトランジスタのゲート絶縁膜502、ゲート電極503及びソース・ドレイン領域506を半導体基板501に形成し、ソース・ドレイン領域506上に、シリサイド反応に必要な金属の拡散を抑制する拡散抑制膜511を形成する。そして、ゲート電極上503及び拡散抑制膜511上に、当該拡散抑制膜511が拡散を抑制する金属から成る金属膜531を形成する。その後、金属膜531とゲート電極503とを反応させて、ゲート電極503の全領域をシリサイド化するとともに、拡散抑制膜511を介して金属膜531とソース・ドレイン領域506とを反応させて、ソース・ドレイン領域を506シリサイド化する。

(もっと読む)

半導体装置の製造方法

【課題】シリコンから構成される導電パターンの下から上までの幅を均一化すること。

【解決手段】半導体基板1上に絶縁膜5を介して第1シリコン膜6を形成し、第1シリコン膜6に高濃度で一導電型不純物を導入し、第1シリコン膜6上に第2シリコン膜9を形成し、第2シリコン膜9上に所定パターンのマスク10mを形成した後、マスク10mから露出する領域で、第1シリコン膜6が露出しない深さまで第1条件により第2シリコン膜9をエッチングし、ついで第1条件に比べて半導体基板1の垂直方向へのエッチング成分の高い第2条件によって第2シリコン膜9の残りと第1シリコン膜6を絶縁膜5が露出しない深さまでエッチングし、さらに第2条件に比べて絶縁膜に対する第1シリコン膜6のエッチング選択比が大きな第3条件により第1シリコン膜6の残りをエッチングする工程とを有している。

(もっと読む)

半導体装置

【課題】トランジスタのサイズによらない普遍的な引っ張り歪みをnチャネル型MOSトランジスタに印加できる半導体装置を提供する。

【解決手段】nチャネル型MOSトランジスタのゲート絶縁膜として、高誘電率絶縁膜を使用し、この高誘電率絶縁膜を半導体基板上に界面層を介さず直接形成することにより、チャネル領域に引張り歪を与える。チャネル領域に圧縮歪を有するpチャネル型MOSトランジスタと組み合わせることにより、相補型の高性能半導体装置を構成できる。

(もっと読む)

半導体装置およびその製造方法

【課題】金属とシリコンおよび/またはゲルマニウムを必須として含む金属半導体化合物をゲート電極とする金属絶縁膜半導体電界効果トランジスタを利用した半導体装置において、ゲート絶縁膜やチャネル等によらずに複数の閾値電圧を設定する。

【解決手段】半導体装置が、MAxで表される組成を有する第1のゲート電極を含む第1のトランジスタと、MAyで表される組成を有する第2のゲート電極を含む第2のトランジスタを少なくとも含むMIS電界効果トランジスタを含む(式中、MはW、Mo、Ni、Pt、Ta、Pd、Co、およびTiからなる群より選択される少なくとも1種の金属元素であり、Aはシリコンおよび/またはゲルマニウムであり、0<x≦3、および0<y≦3であり、xとyは異なる)。

(もっと読む)

窒化物半導体素子、窒化物半導体パッケージおよび窒化物半導体素子の製造方法

【課題】高耐圧性を確保するとともに、低いゲート閾値電圧を実現することができる窒化物半導体素子およびその製造方法を提供すること。

【解決手段】この電界効果トランジスタは、n型GaN層2、p型GaN層3およびn型GaN層4が、順に積層された窒化物半導体積層構造部1を備えている。窒化物半導体積層構造部1には、断面台形(メサ形状)となるようにエッチングされることにより、壁面7が形成されている。この壁面7の形成によって露出したp型GaN層3の半導体表面部には、p型GaN層3とは異なる伝導特性を有する領域10が形成され、領域10に接するようにゲート絶縁膜8が形成されている。さらにこのゲート絶縁膜8を挟んで領域10に対向するようにゲート電極9が形成されている。

(もっと読む)

21 - 40 / 109

[ Back to top ]