Fターム[5F140BG26]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666)

Fターム[5F140BG26]の下位に属するFターム

堆積 (2,821)

不純物の導入 (644)

熱処理 (1,248)

ゲート電極の形状を形成する方法 (2,844)

Fターム[5F140BG26]に分類される特許

81 - 100 / 109

半導体装置およびその製造方法

【課題】微細化に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板の主表面中に設けられた第1絶縁膜21と、前記第1絶縁膜上に設けられ前記第1絶縁膜の構成元素と所定の金属元素との化合物を主成分とし前記第1絶縁膜よりも比誘電率が高い第1高誘電体膜22−1とを少なくとも備えたゲート絶縁膜12と、前記ゲート絶縁膜上に設けられ、CuまたはCuを主成分とするゲート電極13と、前記ゲート電極を挟むように前記半導体基板中に隔離して設けられたソースまたはドレイン15とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ポリメタルゲート構造及びデュアルゲート構造のゲート電極を有する半導体装置において、ポリシリコン層中の不純物の相互拡散を防止すると共に、N型ポリメタルゲート電極とP型ポリメタルゲート電極の抵抗を共に低くすることが可能な半導体装置の製造方法を提供する。

【解決手段】 P型ポリメタルゲート電極10pが、P型ポリシリコン層104pと、P型ポリシリコン層104p上に不連続に配置された複数のタングステンシリサイド(WSi2)粒子105gからなるWSi2層105と、WSi2層105の不連続部分に露出したP型シリコン層104p上及びWSi2層105(WSi2粒子105g)表面に連続的に形成されたシリコン膜106と、窒化タングステン(WN)層107と、タングステン(W)層108とを備えて構成される。

(もっと読む)

半導体装置の製造方法

【課題】薄いニッケル膜を用いてシリコンゲルマニウム層をシリサイド化する場合であっても、シート抵抗の上昇や接合リーク電流の増加を抑制し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板34上にゲート電極54pを形成する工程と、ゲート電極の両側の半導体基板内にソース/ドレイン拡散層64pを形成する工程と、ソース/ドレイン拡散層にシリコンゲルマニウム層100bを埋め込む工程と、シリコンゲルマニウム層の上部にアモルファス層101を形成する工程と、アモルファス層上にニッケル膜66を形成する工程と、熱処理を行い、ニッケル膜とアモルファス層とを反応させることにより、シリコンゲルマニウム層上にシリサイド膜102bを形成する工程とを有している。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、閾値電圧のシフトが少ないフルシリサイドゲート電極をもつ半導体装置を容易に実現できるようにする。

【解決手段】 基板1上に絶縁膜2a、2b及び第1のポリシリコン層3a、3bをこの順に積層して形成する工程と、イオン注入法を適用することに依って第1のポリシリコン層3a、3b中に不純物を導入する工程と、第1のポリシリコン層3a、3b上に第2のポリシリコン層11a、11bを形成する工程と、第2のポリシリコン層11a、11bの表面側から第1のポリシリコン層3a、3bと絶縁膜2a、2bとの界面側に至るまで全てをシリサイド化してフルシリサイドのゲート電極を形成する。

(もっと読む)

シリコン化合物の形成方法

【課題】 工程数を可及的に低減し得るとともに低温環境で所望の化合物を形成し得るシリコン化合物の形成方法を提供する。

【解決手段】 チャンバ1の内部に配設するとともにSiとの化合物を形成し得る元素を含む材料で形成した被エッチング部材11を、相対的に高温に保持した状態でハロゲンガスのラジカルを作用させることにより前記材料とハロゲンとの化合物である前駆体24のガスを形成する一方、Si界面を露出させて前記チャンバ1内に収納した基板3の温度を相対的に低温に保持することにより前記前駆体24を前記基板3のSi界面に吸着させ、その後Si界面に吸着させた前記前躯体24に前記ハロゲンガスのラジカルを作用させてこの前躯体24を還元することにより前記材料とSiとの化合物を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 シリサイド膜の底面とpn接合界面との間の距離を広く保つことが可能であり、しかも制御性よく半導体装置を製造することが可能な製造方法を提供する。

【解決手段】 第1導電型の半導体領域81上に形成された第2導電型の半導体領域87上に第1のシリサイド膜89を形成する工程と、第1のシリサイド膜上に(Si−H)基を含むシリコン化合物膜90を塗布によって形成する工程と、熱処理により第1のシリサイド膜に含まれる金属とシリコン化合物膜に含まれるシリコンとを反応させて第2のシリサイド膜91を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート電極および不純物拡散層にシリサイド膜が形成された半導体装置において、不純物拡散層のシリサイド膜の異常成長や凝集を抑える。

【解決手段】 半導体装置100は、シリコン基板102と、シリコン基板102上に形成され、ゲート電極132を含む半導体素子と、ゲート長方向の断面において、シリコン基板102の半導体素子が形成された領域の両側方に形成された不純物拡散層121(または122)と、不純物拡散層121(または122)表面に形成され、第1の金属のシリサイド化合物により構成された第1のシリサイド膜130と、ゲート電極132の少なくとも表面に形成され、第1の金属のシリサイド化合物よりシリサイド化の温度が低い第2の金属のシリサイド化合物により構成された第2のシリサイド膜131と、を含む。

(もっと読む)

ナノワイヤーの選択的な堆積を利用した、ナノワイヤーCHEMFETセンサ装置の製造方法

【課題】 ナノワイヤーCHEMFETセンサ機構を製造する方法を提供する。

【解決手段】シリコン基板34を用意する工程と、上記シリコン基板上に多結晶ZnOシード層42を堆積する工程と、上記多結晶ZnOシード層にパターンを形成し、エッチングする工程と、上記多結晶ZnOシード層および上記シリコン基板上に絶縁層46を堆積する工程と、上記絶縁層にパターンを形成およびエッチングし、ソース領域およびドレイン領域に対する接触孔を形成する工程と、上記接触孔を金属化し、上記ソース領域および上記ドレイン領域に対する接点54,56を形成する工程と、誘電層58を堆積し、上記絶縁層および上記接点を封止する工程と、上記封止した層にパターンを形成およびエッチングし、多結晶ZnOシード層を露出する工程と、上記露出したZnOシード層上においてZnOナノ構造66を成長させ、ZnOナノ構造体センサ装置を形成する工程と、を含む。

(もっと読む)

薄膜形成方法

【課題】 転写膜の汚染や分解・変質を生じないレーザ転写による薄膜形成方法を実現する。

【解決手段】 本発明のレーザ転写による薄膜形成方法では、レーザ光9を透過するガラス基板1上に、照射されるレーザ光9によりアブレーションされるアブレーション層(第1の有機膜)2、カーボンブラックを混入させてレーザ光9を遮蔽する効果を持たせた有機膜(第2の有機膜)3、及びグルコースオキシターゼを含む薄膜(酵素膜)からなる転写膜4が順次積層された転写基板5を用意する。この転写基板5の転写膜4と、被転写基板であるp型シリコン基板(回路基板)6を、回路基板6上に設けたスペーサ7を介して対向させる。その後、ガラス基板1側からアブレーション層2にレーザ光9を照射することで、転写膜4aを回路基板6側に転写する。

(もっと読む)

シリコンを導入することによって、仕事関数を微調整したメタルゲート構造を形成する方法

制御された仕事関数を備えるメタルゲート(30)を有する半導体構造を形成する方法である。この方法は、チャネルによって分離された活性領域(12)を備えた基板およびチャネル上および絶縁層(20)内の一時的ゲート(16)を有するプレカーサを形成するステップを含んでいる。この一時的ゲート(16)を除去して、絶縁層(20)中に底面およびサイドウォールを備える凹部(22)を形成する。非シリコン金属を含んでいるメタル層(26)を、この凹部(22)にたい積する。このメタル層(26)中にシリコンを導入し、メタル層(26)上にメタルをたい積する。シリコンの導入は、熱的シラン処理により行われる。この熱的シラン処理は、メタル層(26)をたい積する前、後、またはその前後に実行される。メタル層(26)中に導入するシリコンの量によって、形成されるメタルゲート(30)の仕事関数を制御する。  (もっと読む)

(もっと読む)

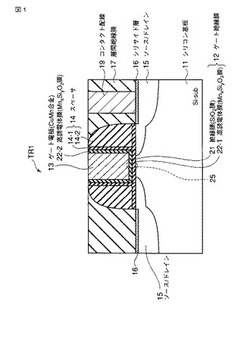

半導体装置の製造方法及び半導体装置

【課題】 サリサイドプロセスにおけるシリサイド細線化を防ぎ、設計により近い理想的なシリサイド寸法が確保できるポリサイドゲート電極を有する半導体装置及びその製造方法を提供する。

【解決手段】 基板11上にシリコン酸化膜等のゲート絶縁膜13、ポリシリコン層14を順次形成する。このポリシリコン層14を選択的に除去してポリシリコンパターン141を形成し、側壁として絶縁膜16を形成する。その後、ポリシリコンパターン141の上部を所定厚さT1だけ除去する。これにより、絶縁膜16の上部をポリシリコンパターン141の上面よりも高くする。所定厚さT1は、破線に示すように、ポリシリコンパターン141上に形成しようとするシリサイド層19の側部が絶縁膜16の上部で保護されるような形態となるように設定される。

(もっと読む)

半導体素子を形成する方法

【課題】 ゲートリーク電流の低減。

【解決手段】 本発明による半導体の製造方法は、基板を設ける工程と、誘電体層を基板の上に形成する工程と、アモルファス半導体層を誘電体層の上に成長させる工程と、アモルファス半導体層に不純物をドープする工程と、そして高温処理工程をアモルファス層に施して前記アモルファス半導体から結晶化層を形成する工程とを備える。

(もっと読む)

MOSトランジスタのためのゲート電極

一態様では、シリコン層(112')に第1の熱処理を施し、このシリコン層(112')上に金属積層体(110')を形成し、この金属積層体に第2の熱処理を施すことによって、トランジスタのゲートを形成する。第1の熱処理は、急速熱アニールステップを含み、第2の熱処理は、急速窒化ステップを含む。本発明により得られたるゲートは、シリコン層と金属積層体との間で比較的低い界面接触抵抗を示し、そのため、このゲートを高速デバイスで使用すると有利である。  (もっと読む)

(もっと読む)

絶縁ゲート型半導体装置の製造方法

【課題】 絶縁ゲート型半導体装置の製造方法に関し、ゲート電極を簡単な製造工程で結晶性の高い単結晶半導体で構成する。

【解決手段】 貼り合わせ用単結晶半導体基板4に剥離用元素5をイオン注入したのち、貼り合わせ用単結晶半導体基板4のイオン注入側が貼り合わせ面となるように絶縁膜3を形成した素子形成用単結晶半導体基板1に貼り合わせ、次いで、熱処理を行って貼り合わせ用単結晶半導体基板4を注入した元素の濃度ピーク位置近傍で剥離したのち、素子形成用単結晶半導体基板1側に残存した貼り合わせ用単結晶半導体基板4の残部6をゲート電極状にエッチングする。

(もっと読む)

互いに重ねて堆積させた金属層の積層体中に形成されたゲート電極を含むMOSトランジスタを備える半導体デバイスの製造方法

互いに重ねて堆積させたいくつかの金属層(8,9,13;8,12,13)として形成したゲート電極(15,16)を有するMOSトランジスタを備える半導体デバイスの製造方法。この方法では、シリコン本体(1)に、ゲート誘電体層(7)を備えるシリコン活性領域(4,5)およびこれらの領域を互いに絶縁するフィールド分離領域(6)を形成する。次いで、第1の金属層(8)を堆積させ、活性領域(4)の一部の位置でその層中に局所的に窒素を導入する。次いで、第1の金属層上に第2の金属層(13)を堆積させ、その後それらの金属層中にゲート電極をエッチングする。第1の金属層中に窒素を導入する前に、第1の金属層上に窒素透過性の第3の金属補助層(9)を堆積させる。したがって、その下にあるゲート電極に損傷を与える危険なく、第1の金属層を窒化することができる。金属の仕事関数を実質的に変えることが可能であるとともに、NMOSおよびPMOSを備える半導体デバイスが実現される。  (もっと読む)

(もっと読む)

絶縁ゲート型電界効果トランジスタを含む半導体装置

【課題】 NチャネルMISFETのゲート電極およびPチャネルMISFETのゲート

電極が共に適切な仕事関数を持ち、しきい値電圧の制御が容易な絶縁ゲート型電界効果ト

ランジスタを含む半導体装置を実現する。

【解決手段】 本発明の絶縁ゲート型電界効果トランジスタを含む半導体装置は、第1の

素子領域に形成されると共に、ゲート電極膜におけるゲート絶縁膜に接する領域が、タン

グステンシリサイドで構成されたNチャネルMISFETと、第2の素子領域に形成され

ると共に、ゲート電極膜が、白金シリサイド及びタングステンシリサイドと同じ構成材料

でかつNチャネルMISFETのゲート電極膜よりもシリコン含有量が少ないタングステ

ンシリサイドで構成されたPチャネルMISFETを有し、NチャネルMISFETのゲ

ート電極膜の仕事関数が、PチャネルMISFETのゲート電極膜の仕事関数よりも小さ

い。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極中への砒素のイオン注入を抑制することができる半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体基板上の素子形成領域にゲート絶縁膜を介して形成された砒素を含むシリコン膜5とNiシリサイド層11の積層構造からなるゲート電極5と、ゲート電極5の側面に形成された絶縁膜6、7からなるサイドウォール8と、ゲート電極5の両側の素子形成領域に形成された砒素を含むソース及びドレイン層9、10と、ソース及びドレイン層9、10上に形成されたNiシリサイド層11′とを備えている。また、ゲート電極5内に含まれる砒素のピーク濃度が、ソース及びドレイン層9、10に含まれる砒素のピーク濃度の10分の1以下であることを特徴としている。

(もっと読む)

高誘電率ゲート絶縁膜を備えた電界効果トランジスタを有する半導体装置及びその製造方法

【課題】 高誘電率ゲート絶縁膜を用いるFET及びその製造方法において、閾値電圧の制御性を向上する。

【解決手段】 基板101上に、高誘電率ゲート絶縁膜110を形成した後、高誘電率ゲート絶縁膜110上にゲート電極111aを形成する。次に、少なくともゲート電極111aをマスクとして基板101にN型不純物を導入し、N型イクステンション領域113を形成する。続いて、少なくともゲート電極111aをマスクとして、基板101におけるN型イクステンション領域113の下にP型不純物を導入することにより、P型ポケット領域114を形成する。ここで、N型イクステンション領域113に対するN型不純物としての砒素(As)の導入量を、高誘電率ゲート絶縁膜110の膜厚に基づいて定められる所定値以下である範囲に設定する。

(もっと読む)

半導体装置の製造方法

【課題】非シリサイド領域形成用の絶縁膜をウエットエッチングすることで生じる、分離絶縁膜の後退やサイドウオールの後退を防止する。

【解決手段】ポリシリコン膜表面およびシリコン基板表面を露出させる第1工程と、レジストパターンニングする第2工程と、レジスト膜5をマスクにして酸素イオンあるいは窒素イオンを注入し、レジスト膜5が存在しない領域のポリシリコン膜表面およびシリコン基板表面に酸素イオンあるいは窒素イオンを導入する第3工程と、レジスト膜5を除去する第4工程と、シリコン基板1上に高融点金属膜6を堆積した後に第1の熱処理を行って、イオン注入領域以外の領域のポリシリコン膜表面およびシリコン基板表面をシリサイド化して高融点金属シリサイド層7を形成する第5工程と、イオン注入領域上の高融点金属膜6を除去する第6工程とを含む。

(もっと読む)

半導体装置の製造方法および半導体製造装置

【課題】 n型不純物が導入されたレジスト膜を除去する工程において、異常生成物の発生を抑制することができる技術を提供する。

【解決手段】 ポリシリコン膜15上にレジスト膜16を形成した後、このレジスト膜16に対して露光・現像することにより、レジスト膜16をパターニングする。パターニングは、ポリシリコン膜15のゲート電極形成領域に開口部17が形成されるように行う。次に、パターニングしたレジスト膜16をマスクにして、開口部17から露出したポリシリコン膜15内にリンを注入する。このとき、マスクであるレジスト膜16にもリンが注入されて硬化層16aが形成される。次に、酸素ガスおよびフォーミングガスを導入して硬化層16aおよびレジスト膜16を除去する。ここで、酸素ガスとフォーミングガスとの混合ガスに対するフォーミングガスの体積比率を5%以上30%以下にする。

(もっと読む)

81 - 100 / 109

[ Back to top ]