半導体装置及びその製造方法

【課題】 ポリメタルゲート構造及びデュアルゲート構造のゲート電極を有する半導体装置において、ポリシリコン層中の不純物の相互拡散を防止すると共に、N型ポリメタルゲート電極とP型ポリメタルゲート電極の抵抗を共に低くすることが可能な半導体装置の製造方法を提供する。

【解決手段】 P型ポリメタルゲート電極10pが、P型ポリシリコン層104pと、P型ポリシリコン層104p上に不連続に配置された複数のタングステンシリサイド(WSi2)粒子105gからなるWSi2層105と、WSi2層105の不連続部分に露出したP型シリコン層104p上及びWSi2層105(WSi2粒子105g)表面に連続的に形成されたシリコン膜106と、窒化タングステン(WN)層107と、タングステン(W)層108とを備えて構成される。

【解決手段】 P型ポリメタルゲート電極10pが、P型ポリシリコン層104pと、P型ポリシリコン層104p上に不連続に配置された複数のタングステンシリサイド(WSi2)粒子105gからなるWSi2層105と、WSi2層105の不連続部分に露出したP型シリコン層104p上及びWSi2層105(WSi2粒子105g)表面に連続的に形成されたシリコン膜106と、窒化タングステン(WN)層107と、タングステン(W)層108とを備えて構成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は半導体装置及びその製造方法に関し、特に、ポリメタルゲート構造及びデュアルゲート構造のゲート電極を有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、半導体装置、特にDRAM(Dynamic Random Access Memory)においては、デバイスの動作速度を向上させるために、ポリメタルゲート構造が多く採用されている。

【0003】

ポリメタルゲート構造は、ポリシリコン層上に金属層を積層させたゲート電極構造であり、従来から用いられているポリサイドゲート構造よりもワード線の平面方向の抵抗(シート抵抗)を低くすることができる。しかしながら、ポリシリコン層上に金属層(例えばタングステン(W))を直接形成すると、後の高温熱処理においてポリシリコン層と金属層とが反応して、ポリシリコン層と金属層との間に厚いシリサイド層(例えばタングステンシリサイド(WSi)層)が形成される。シリサイド層は、電気抵抗が比較的高いため、デバイスの高速動作のためには、シリサイド層の形成を抑えることが必要となる。この対策として、特許文献1には、ポリシリコン層と金属層との間に窒化タングステン(WN)等の金属窒化層を形成することにより、ポリシリコン層と金属層との反応を抑制する技術が記載されている。

【0004】

しかし、ポリシリコン層上に直接金属窒化層を形成すると、後の熱処理において、ポリシリコン層と金属窒化層とが反応し、金属シリサイド窒化層が形成されてしまうこととなる。金属シリサイド窒化層は、組成もしくは積層膜の構成によっては高抵抗になることがあり、その膜厚が厚くなると、低抵抗のポリメタルゲート電極は望めない。

【0005】

そこで、本発明者は、特許文献2において、ポリシリコン層と金属窒化層との間に、薄いシリサイド層を介在させることにより、ポリシリコン層と金属窒化層との反応を抑制する方法を提案している。

【0006】

一方、デバイスの高性能化や駆動電圧の低電圧化のため、デュアルゲート構造も採用されている。デュアルゲート構造は、Nチャネルトランジスタのゲート電極にはN型不純物(リン等)を導入したN型ポリシリコンを含むゲート電極を、PチャネルトランジスタにはP型不純物(ボロン等)を導入したP型ポリシリコンを含むゲート電極を用いた構造である。

【0007】

しかし、特許文献2のように、ポリシリコン層、シリサイド層、金属窒化層及び金属層を積層した構造のポリメタルゲート構造の電極をデュアルゲート構造に適用した場合、ゲートパターニング前においては、N型ポリシリコン層とP型ポリシリコン層とは隣接して連続した膜となっており、その上全面にシリサイド層が形成された状態となるため、ゲートパターニング前の熱処理等によって、N型ポリシリコン層中のN型不純物及びP型ポリシリコン層中のP型不純物が、シリサイド層中に吸い上げられ、相互拡散することにより、界面抵抗の上昇やゲート換算膜厚の増加等の問題が発生することが判明した。そこで、本発明者は、特許文献3において、P型ポリシリコン層上に形成するシリサイド層を不連続にすることにより、N型及びP型ポリシリコン層中の不純物がシリサイド層を介して相互拡散することを防止する方法を提案している。

【特許文献1】特開平11−233451号公報

【特許文献2】特開2003−163348号公報

【特許文献3】特開2005−116693号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、P型ポリシリコン層上のシリサイド層を不連続とすると、P型ポリメタルゲート電極において、十分に低いシート抵抗値が得られなくなる場合が生じることが判明した。

【0009】

本発明は上記の問題点を解決すべくなされたものであって、本発明の目的は、ポリメタルゲート構造及びデュアルゲート構造のゲート電極を有する半導体装置において、シリサイド層中の不純物の相互拡散を防止すると共に、N型ポリメタルゲート電極とP型ポリメタルゲート電極のシート抵抗を共に低くすることが可能な半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0010】

本発明による半導体装置は、Nチャネルトランジスタ形成領域とPチャネルトランジスタ形成領域とを有する半導体基板と、前記半導体基板の前記Nチャネルトランジスタ形成領域上に設けられた第1のゲート電極と、前記半導体基板の前記Pチャネルトランジスタ形成領域上に設けられた第2のゲート電極とを有し、前記第1のゲート電極が、N型不純物を含むN型シリコン層と、前記N型シリコン層上に形成された第1のシリサイド層と、前記第1のシリサイド層上に形成された第1のシリコン膜と、前記第1のシリコン膜上に形成された第1の金属窒化層と、前記第1の金属窒化層上に形成された第1の金属層とを備え、前記第2のゲート電極が、P型不純物を含むP型シリコン層と、前記P型シリコン層上に形成され複数の粒状のシリサイドが前記半導体基板の表面と略平行な方向に不連続に配置されてなる第2のシリサイド層と、第2のシリサイド層の前記不連続部分に露出した前記P型シリコン層の表面及び前記第2のシリサイド層の表面上に連続的に形成された第2のシリコン膜と、前記第2のシリコン膜上に形成された第2の金属窒化層と、前記第2の金属窒化層上に形成された第2の金属層とを備えることを特徴とする。

【0011】

また、本発明による半導体装置の製造方法は、半導体基板のNチャネルトランジスタ形成領域上にN型不純物を含むN型シリコン層を形成し、前記半導体基板のPチャネルトランジスタ形成領域上にP型不純物を含むP型シリコン層を形成する第1の工程と、前記N型シリコン層上に第1のシリサイド層を形成し、前記P型シリコン層上に複数の粒状のシリサイドが前記半導体基板の表面と略平行な方向に不連続に配置されてなる第2のシリサイド層を形成する第2の工程と、前記第1のシリサイド層上、前記第2のシリサイド層の前記不連続部分に露出した前記P型シリコン層の表面及び前記第2のシリサイド層の表面上に連続的なシリコン膜を形成する第3の工程と、前記シリコン膜上に金属窒化層を形成する第4の工程と、前記金属窒化層上に金属層を形成する第5の工程と、前記金属層、前記金属窒化層、前記シリコン膜、前記第1のシリサイド層、前記第2のシリサイド層、前記N型シリコン層及び前記P型シリコン層をパターニングして、前記Nチャネルトランジスタ形成領域に前記N型シリコン層を含む第1のゲート電極を、前記Pチャネルトランジスタ形成領域に前記P型シリコン層を含む第2のゲート電極をそれぞれ形成する第6の工程とを備えることを特徴とする。

【発明の効果】

【0012】

本発明によれば、P型シリコン層上においてシリサイド層を不連続としていることにより、不純物の相互拡散によるゲート電極の抵抗値の増加を抑制することができると共に、シリサイド層の不連続部分に露出したP型シリコン層の表面と不連続なシリサイド層の表面を連続的にシリコン膜で覆うことにより、P型ポリメタルゲート電極(第2のゲート電極)を低シート抵抗にすることが可能となる。

【0013】

上記第1及び第2のシリコン膜としては、ノンドープのシリコン膜を用いることが好ましく、これによりP型ポリメタルゲート電極の電気抵抗のより高い低減効果が期待できる。これは、金属窒化層がP型不純物を多く含むシリコン層と接した場合、シリコン層に含まれるP型不純物によって金属窒化層とシリコン層との反応が促進されて、厚い金属シリサイド窒化層が形成されるのに対し、ノンドープのシリコン膜は金属窒化層との反応が少ないため、金属シリサイド窒化膜が形成されても、その膜厚をごく薄くすることができるためと考えられる。

【発明を実施するための最良の形態】

【0014】

以下、添付図面を参照しながら、本発明の好ましい実施の形態について説明する。

【0015】

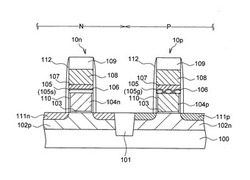

図1乃至図10は、本発明の実施の形態に係るポリメタルゲート/デュアルゲート構造のゲート電極を備えたNチャネルトランジスタ及びPチャネルトランジスタの製造工程を概略的に示す工程図である。図1乃至10において、「領域N」はN型ポリメタルゲート電極を含むNチャネルトランジスタを形成する領域を表し、「領域P」はP型ポリメタルゲート電極を含むPチャネルトランジスタを形成する領域を表している。

【0016】

まず、図1に示すように、半導体基板100の所定の領域に、STI(Shallow Trench Isolation)技術により、素子分離絶縁膜101を形成する。これにより、領域Nと領域Pが分離される。次に、領域NにP型不純物としてボロン(B)をドープしてPウェル102pを形成し、領域PにN型不純物としてリン(P)をドープしてNウェル102nを形成する。

【0017】

次に、図2に示すように、半導体基板100の表面を熱酸化することにより、厚さ約4nmのゲート酸化膜103を形成する。

【0018】

次に、ゲート酸化膜103上に、CVD(Chemical Vapor Deposition)法により、ノンドープのシリコン層104を厚さ約100nm形成する。シリコン層104としては、アモルファスシリコン又は多結晶シリコンのいずれを用いることも可能であるが、表面に凹凸無く形成でき、微細加工に適したアモルファスシリコンを用いるのが好ましい。

【0019】

次に、図3に示すように、領域Pをレジストマスク(図示せず)で覆い、領域Nのシリコン層104に、約10keVの加速エネルギー、約5×1015/cm2のドーズ量でN型不純物としてリン(P)をイオン注入し、領域Nのシリコン層104をN型シリコン層104nにする。続いて、領域Pを覆う上記レジストマスクを除去した後、領域Nを覆うレジストマスク(図示せず)を形成し、領域Pのシリコン層104に、約5keVの加速エネルギー、約1×1015〜5×1015/cm2、好ましくは約3×1015〜5×1015/cm2のドーズ量でP型不純物としてボロン(B)をイオン注入し、領域Pのシリコン層104をP型シリコン層104pにする。

【0020】

次に、フッ酸(HF)と過酸化水素水(H2O2)の混合液を用いて、シリコン層104(N型シリコン層104n及びP型シリコン層104p)の表面に形成された自然酸化膜を除去した後、図4に示すように、シリコン層104上にシリサイド層としてタングステンシリサイド(WSi2)層105を形成する。WSi2層105は、N型シリコン層104n上においては、N型シリコン層104nの表面全面を覆うWSi2層105sとして形成し、P型シリコン層104p上においては、粒状の複数のWSi2粒子105gが半導体基板の表面と略平行な方向に不連続に配置された状態となるように形成する。このように、WSi2層105をP型シリコン層104p上において不連続にすることにより、P型シリコン層104pに含まれるP型不純物とN型シリコン層104nに含まれるN型不純物が、WSi2層105を介して相互拡散することを抑制できる。

【0021】

WSi2層105は、CVD法により、反応室の圧力を約30〜100Pa、半導体基板100の温度を約550℃とし、流量約200sccmのジクロロシラン(SiH2Cl2)と流量約2sccmの六フッ化タングステン(WF6)とをそれぞれ供給し、約30秒間反応させることにより形成する。これにより、WSi2層105は、上述のように、N型シリコン層104n上においては連続膜として形成され、P型シリコン層104p上においては、P型シリコン層104p中のP型不純物の影響により、不連続な膜として形成される。このとき、N型シリコン層104n上に形成されるWSi2層105sの堆積膜厚が約3〜10nm、好ましくは約5〜7nmとなるように形成するのが好ましい。

【0022】

ここで、WSi2粒子105gの好ましい粒径は、約5〜30nmである。これは、粒径が5nmより小さいと、P型ポリメタルゲート電極の界面抵抗が高くなってしまう恐れがあり、30nmを超えると不純物の相互拡散を抑制する効果が弱まるためである。また、複数のWSi2粒子105gの隣接する2つの粒子間の間隔は、約2〜80nmであることが好ましい。間隔が2nmよりも狭いと、隣接するWSi粒子105g同士が接近しすぎて不純物の相互拡散を抑制できなくなる恐れがあり、80nmを超えると、WSi2が形成されない領域が広くなりすぎてP型ポリメタルゲート電極の界面抵抗が高くなってしまう恐れがあるためである。

【0023】

次に、図5に示すように、CVD法により、WSi2層105s、WSi2粒子105gの不連続部分に露出したP型シリコン層104p上及びWSi2粒子105gの表面上に連続的なノンドープのシリコン膜106を形成する。成膜条件は、WSi2層105を形成するためのガスとして反応室に供給していたWF6を停止し、ジクロロシランの流量を約300sccmにし、アルゴン(Ar)を約800sccmの流量で供給し、半導体基板100の温度を約500℃、反応室の圧力を約50〜300Paとして、約5〜120秒間、好ましくは40〜120秒間とする。シリコン膜106の膜厚は、薄くしすぎると、P型ポリメタルゲート電極においてWSi2層105を不連続にしたことによる抵抗の増大を抑制する効果が十分に得られなくなり、厚くしすぎると、後にこの上に形成する窒化タングステン(WN)層及びタングステン(W)層とWSi2層105及びシリコン層104との導電性が低くなり、N型及びP型ポリメタルゲート電極の抵抗が共に高くなってしまう恐れがある。そのため、シリコン膜106の膜厚は、約0.3〜1.5nmとするのが好ましい。シリコン膜106の膜厚は、反応室の圧力、成膜(処理)時間及びジクロロシランの流量を適宜変更することにより所望の厚さとすることができる。なお、シリコン膜106は、アモルファスシリコン及びポリシリコンのいずれを用いることも可能である。

【0024】

続いて、WSi2層105をCVD法で形成したことによりWSi2層105に残留した塩素やフッ素等のガスを除去する、いわゆる脱ガス処理として、約830℃、N2雰囲気で約30秒間の熱処理(RTA:Rapid Thermal Annealing)を行う。この熱処理によって、同時にN型シリコン層104nに注入されたN型不純物及びP型シリコン層104pに注入されたP型不純物が活性化される。また、アモルファスで形成されたシリコン膜104は、このときポリシリコン膜に変換される。

【0025】

なお、図5においてAで示した部分の拡大図である図11に示すように、上記脱ガスのための熱処理によって、シリコン膜106とWSi2層105(105s,105g)との界面部が反応し、シリサイド層20が形成される場合もあるが、シリサイド層20が形成されたとしても、その膜厚は非常に薄く、シリコン膜106のWSi2層105と反対側の表面までシリサイド化されることはない。

【0026】

次に、図6に示すように、スパッタ法により、シリコン膜106の上に、金属窒化層として厚さ約10nmの窒化タングステン(WN)層107を形成する。

【0027】

続いて、図7に示すように、スパッタ法により、WN層107上に、金属層として厚さ約80nmのタングステン(W)層108を形成する。

【0028】

次に、図8に示すように、CVD法により、W層108上に厚さ約200nmのシリコン窒化膜を形成し、これをゲート電極形状にパターニングして、キャップ絶縁膜109を形成する。

【0029】

続いて、図9に示すように、キャップ絶縁膜109をマスクとして、W層108、WN層107、シリコン膜106、WSi2層105(105s,105g)及びポリシリコン層104(104n,104p)の積層膜をドライエッチングによりパターニングして、領域NにN型ポリシリコン層104nを含むN型ポリメタルゲート電極10nを、領域PにP型ポリシリコン層104pを含むP型ポリメタルゲート電極10pを形成する。

【0030】

次に、このゲートパターニングのためのドライエッチングにより、各ゲート電極の端部がダメージを受けるため、これを改善すべく、熱処理を行い、各ゲート電極のポリシリコン層104の側面に側面酸化膜110を形成してダメージを回復させる。なお、図9においてBで示した部分の拡大図である図12に示すように、この側面酸化膜110形成のための熱処理によって、シリコン膜106とWN層107とが反応し、タングステンシリサイド窒化層(WSiN層)30が形成される。しかしながら、本実施形態によれば、WN層107は、高濃度に不純物を含むP型シリコン層104pとではなく、ノンドープのシリコン膜106と接してこの膜と反応するため、形成されるWSiN層30は非常に薄い膜となり、従って、P型ポリメタルゲート電極10pの電気抵抗が増大するのを抑制することができる。これは、WN層107がP型不純物を多量に含むシリコン層104pと接した状態で熱処理を行った場合(従来技術に相当)、シリコン層104pに含まれる不純物によって両者の反応が促進され、厚いWSiN層が形成され易いのに対し、本実施形態のように、WN層107とノンドープのシリコン膜106とが接している場合は、熱処理を行っても両者の反応が進みにくいためと推測される。

【0031】

次に、領域Pをレジストマスク(図示せず)で覆い、領域NにN型不純物(例えばヒ素(As))を高濃度にイオン注入することにより、N型ソース・ドレイン拡散層111nを形成する。続いて領域Pを覆うレジストマスクを除去した後、領域Nを覆うレジストマスク(図示せず)を形成し、領域PにP型不純物(例えばボロン(B))を高濃度にイオン注入することによりP型ソース・ドレイン拡散層111pを形成する。

【0032】

次に、全面に厚さ約40nmのシリコン窒化膜を形成した後、エッチバックを行って、図10に示すように、N型ポリメタルゲート電極10n及びP型ポリメタルゲート電極10pそれぞれの側面にサイドウォール絶縁膜112を形成する。

【0033】

以上の工程により、領域NにN型ポリメタルゲート電極10nを備えたNチャネルトランジスタが、領域PにP型ポリメタルゲート電極10pを備えたPチャネルトランジスタが完成する。

【0034】

図13に、シリコン膜106のCVDによる成膜時間と、N型ポリメタルゲート電極10nの界面抵抗(N型ポリシリコン層104nとWSi2層105(105s)との接触抵抗)及びP型ポリメタルゲート電極10pの界面抵抗(P型ポリシリコン層104pとWSi2層105(105g)との接触抵抗)との関係を示す。図13において、(p)はP型シリコン層104pとWSi2層105(105g)との界面抵抗、(n)はN型シリコン層104nとWSi2層105(105s)との界面抵抗を示している。N型ポリメタルゲート電極10nにおいては、N型シリコン層104nの表面全面にWSi2層105が形成されているため、界面抵抗(n)はシリコン膜106の成膜時間に関わらず、低くほぼ一定である。一方、P型ポリメタルゲート電極10pにおいては、シリコン膜106の成膜時間が長くなるにつれて界面抵抗(p)を低下させることができることがわかる。具体的には、成膜時間が長くなるに従い界面抵抗は徐々に低下していき、40秒を超えたところからほぼ飽和した状態となっている。

【0035】

図14に、WSi2層105のCVDにおけるWF6の流量と、P型ポリメタルゲート電極10pにおけるWSi2層105のシート抵抗との関係を示す。図14において、(a)はWSi2層105上にシリコン膜106を形成しなかった場合(従来技術による場合)のシート抵抗、(b)は、WSi2層105上にシリコン膜106を形成した場合(本実施形態による場合)のシート抵抗を示している。WF6の流量が多くなるほどWSi2層105の不連続性が高くなるため、WSi2層105上にシリコン膜106を形成しなかった場合のシート抵抗(a)は、WF6の流量の増加につれて高くなる。これに対し、シリコン膜106を形成した場合のシート抵抗(b)は、WF6の流量が多くなっても、すなわちWSi2層105の不連続性が高くなっても、低いシート抵抗を得ることができるといえる。

【0036】

以上説明したように、本実施形態によれば、P型シリコン層104p上においてWSi2層105を不連続としていることにより、不純物の相互拡散によるゲート電極の抵抗値の増加を抑制することができると共に、WSi2層105の不連続部分に露出したP型シリコン層104pの表面と不連続なWSi2層105(WSi2粒子105g)の表面を連続的にシリコン膜106で覆うことにより、P型ポリメタルゲート電極10pを低抵抗にすることが可能となる。

【0037】

以上、本発明の好ましい実施の形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

【0038】

例えば、上記実施形態においては、金属層としてタングステン(W)を、金属窒化層としてタングステン窒化(WN)層を、シリサイド層としてタングステンシリサイド(WSi2)層を用いた例を示したが、これに代えて、コバルト(Co)、チタン(Ti)、ニッケル(Ni)又はタンタル(Ta)等他の高融点金属とこれらの窒化層及びシリサイド層を用いることも可能である。

【0039】

また、シリコン膜106はノンドープに限らず、図12に示すWSiN層30(金属シリサイド窒化層)が厚く形成されてP型ポリメタルゲート電極の界面抵抗が増大することのない範囲であれば、低濃度に不純物を含んでいてもよい。

【0040】

また、WSi2層の脱ガスのための熱処理は、シリコン膜106の形成前に行ってもよい。

【0041】

さらに、上記実施形態においては、WSi2層105の成膜に引き続き、同じCVD装置において、WSi2層105の成膜に用いたジクロロシランを用いてシリコン膜106を成膜する例を示したが、これに限らず、例えば、WSi2層105の成膜後、半導体基板を別のCVD装置に移し、モノシラン(SiH4)を用いたCVD法により成膜することも可能である。

【図面の簡単な説明】

【0042】

【図1】本発明の好ましい実施形態による半導体装置の製造方法の一工程(素子分離絶縁膜101の形成〜Pウェル102p、Nウェル102nの形成)を示す断面図である。

【図2】本発明の好ましい実施形態による半導体装置の製造方法の一工程(ゲート酸化膜103の形成〜シリコン層104の形成)を示す断面図である。

【図3】本発明の好ましい実施形態による半導体装置の製造方法の一工程(N型シリコン層104n及びP型シリコン層104pの形成)を示す断面図である。

【図4】本発明の好ましい実施形態による半導体装置の製造方法の一工程(WSi2層105の形成)を示す断面図である。

【図5】本発明の好ましい実施形態による半導体装置の製造方法の一工程(シリコン膜106の形成)を示す断面図である。

【図6】本発明の好ましい実施形態による半導体装置の製造方法の一工程(WN層107の形成)を示す断面図である。

【図7】本発明の好ましい実施形態による半導体装置の製造方法の一工程(W層108の形成)を示す断面図である。

【図8】本発明の好ましい実施形態による半導体装置の製造方法の一工程(キャップ絶縁膜109の形成)を示す断面図である。

【図9】本発明の好ましい実施形態による半導体装置の製造方法の一工程(ゲートパターニング〜N型ソース・ドレイン拡散層111n及びP型ソース・ドレイン拡散層111pの形成)を示す断面図である。

【図10】本発明の好ましい実施形態による半導体装置の製造方法の一工程(サイドウォール絶縁膜112の形成)を示す断面図である。

【図11】本発明の好ましい実施形態による半導体装置の製造方法の図5の工程におけるA部の部分拡大図である。

【図12】本発明の好ましい実施形態による半導体装置の製造方法の図8の工程におけるB部の部分拡大図である。

【図13】シリコン膜106のCVDによる形成における成膜時間と、N型ポリメタルゲート電極10n及びP型ポリメタルゲート電極10pの界面抵抗との関係を示すグラフである。

【図14】WSi2層105のCVDにおけるWF6の流量と、P型ポリメタルゲート電極10pにおけるWSi2層105のシート抵抗との関係を示すグラフである。

【符号の説明】

【0043】

100 半導体基板

101 素子分離絶縁膜

102n ウェル

102p ウェル

103 ゲート酸化膜

104 シリコン層

104n N型シリコン層

104p P型シリコン層

105(105s,105g) WSi2層

106 シリコン膜

107 WN層

108 W層

109 キャップ絶縁膜

110 側面酸化膜

10n 型ポリメタルゲート電極

10p 型ポリメタルゲート電極

111n N型ソース・ドレイン拡散層

111p P型ソース・ドレイン拡散層

112 サイドウォール絶縁膜

20 シリサイド層

30 WSiN層

【技術分野】

【0001】

本発明は半導体装置及びその製造方法に関し、特に、ポリメタルゲート構造及びデュアルゲート構造のゲート電極を有する半導体装置及びその製造方法に関する。

【背景技術】

【0002】

近年、半導体装置、特にDRAM(Dynamic Random Access Memory)においては、デバイスの動作速度を向上させるために、ポリメタルゲート構造が多く採用されている。

【0003】

ポリメタルゲート構造は、ポリシリコン層上に金属層を積層させたゲート電極構造であり、従来から用いられているポリサイドゲート構造よりもワード線の平面方向の抵抗(シート抵抗)を低くすることができる。しかしながら、ポリシリコン層上に金属層(例えばタングステン(W))を直接形成すると、後の高温熱処理においてポリシリコン層と金属層とが反応して、ポリシリコン層と金属層との間に厚いシリサイド層(例えばタングステンシリサイド(WSi)層)が形成される。シリサイド層は、電気抵抗が比較的高いため、デバイスの高速動作のためには、シリサイド層の形成を抑えることが必要となる。この対策として、特許文献1には、ポリシリコン層と金属層との間に窒化タングステン(WN)等の金属窒化層を形成することにより、ポリシリコン層と金属層との反応を抑制する技術が記載されている。

【0004】

しかし、ポリシリコン層上に直接金属窒化層を形成すると、後の熱処理において、ポリシリコン層と金属窒化層とが反応し、金属シリサイド窒化層が形成されてしまうこととなる。金属シリサイド窒化層は、組成もしくは積層膜の構成によっては高抵抗になることがあり、その膜厚が厚くなると、低抵抗のポリメタルゲート電極は望めない。

【0005】

そこで、本発明者は、特許文献2において、ポリシリコン層と金属窒化層との間に、薄いシリサイド層を介在させることにより、ポリシリコン層と金属窒化層との反応を抑制する方法を提案している。

【0006】

一方、デバイスの高性能化や駆動電圧の低電圧化のため、デュアルゲート構造も採用されている。デュアルゲート構造は、Nチャネルトランジスタのゲート電極にはN型不純物(リン等)を導入したN型ポリシリコンを含むゲート電極を、PチャネルトランジスタにはP型不純物(ボロン等)を導入したP型ポリシリコンを含むゲート電極を用いた構造である。

【0007】

しかし、特許文献2のように、ポリシリコン層、シリサイド層、金属窒化層及び金属層を積層した構造のポリメタルゲート構造の電極をデュアルゲート構造に適用した場合、ゲートパターニング前においては、N型ポリシリコン層とP型ポリシリコン層とは隣接して連続した膜となっており、その上全面にシリサイド層が形成された状態となるため、ゲートパターニング前の熱処理等によって、N型ポリシリコン層中のN型不純物及びP型ポリシリコン層中のP型不純物が、シリサイド層中に吸い上げられ、相互拡散することにより、界面抵抗の上昇やゲート換算膜厚の増加等の問題が発生することが判明した。そこで、本発明者は、特許文献3において、P型ポリシリコン層上に形成するシリサイド層を不連続にすることにより、N型及びP型ポリシリコン層中の不純物がシリサイド層を介して相互拡散することを防止する方法を提案している。

【特許文献1】特開平11−233451号公報

【特許文献2】特開2003−163348号公報

【特許文献3】特開2005−116693号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

しかしながら、P型ポリシリコン層上のシリサイド層を不連続とすると、P型ポリメタルゲート電極において、十分に低いシート抵抗値が得られなくなる場合が生じることが判明した。

【0009】

本発明は上記の問題点を解決すべくなされたものであって、本発明の目的は、ポリメタルゲート構造及びデュアルゲート構造のゲート電極を有する半導体装置において、シリサイド層中の不純物の相互拡散を防止すると共に、N型ポリメタルゲート電極とP型ポリメタルゲート電極のシート抵抗を共に低くすることが可能な半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0010】

本発明による半導体装置は、Nチャネルトランジスタ形成領域とPチャネルトランジスタ形成領域とを有する半導体基板と、前記半導体基板の前記Nチャネルトランジスタ形成領域上に設けられた第1のゲート電極と、前記半導体基板の前記Pチャネルトランジスタ形成領域上に設けられた第2のゲート電極とを有し、前記第1のゲート電極が、N型不純物を含むN型シリコン層と、前記N型シリコン層上に形成された第1のシリサイド層と、前記第1のシリサイド層上に形成された第1のシリコン膜と、前記第1のシリコン膜上に形成された第1の金属窒化層と、前記第1の金属窒化層上に形成された第1の金属層とを備え、前記第2のゲート電極が、P型不純物を含むP型シリコン層と、前記P型シリコン層上に形成され複数の粒状のシリサイドが前記半導体基板の表面と略平行な方向に不連続に配置されてなる第2のシリサイド層と、第2のシリサイド層の前記不連続部分に露出した前記P型シリコン層の表面及び前記第2のシリサイド層の表面上に連続的に形成された第2のシリコン膜と、前記第2のシリコン膜上に形成された第2の金属窒化層と、前記第2の金属窒化層上に形成された第2の金属層とを備えることを特徴とする。

【0011】

また、本発明による半導体装置の製造方法は、半導体基板のNチャネルトランジスタ形成領域上にN型不純物を含むN型シリコン層を形成し、前記半導体基板のPチャネルトランジスタ形成領域上にP型不純物を含むP型シリコン層を形成する第1の工程と、前記N型シリコン層上に第1のシリサイド層を形成し、前記P型シリコン層上に複数の粒状のシリサイドが前記半導体基板の表面と略平行な方向に不連続に配置されてなる第2のシリサイド層を形成する第2の工程と、前記第1のシリサイド層上、前記第2のシリサイド層の前記不連続部分に露出した前記P型シリコン層の表面及び前記第2のシリサイド層の表面上に連続的なシリコン膜を形成する第3の工程と、前記シリコン膜上に金属窒化層を形成する第4の工程と、前記金属窒化層上に金属層を形成する第5の工程と、前記金属層、前記金属窒化層、前記シリコン膜、前記第1のシリサイド層、前記第2のシリサイド層、前記N型シリコン層及び前記P型シリコン層をパターニングして、前記Nチャネルトランジスタ形成領域に前記N型シリコン層を含む第1のゲート電極を、前記Pチャネルトランジスタ形成領域に前記P型シリコン層を含む第2のゲート電極をそれぞれ形成する第6の工程とを備えることを特徴とする。

【発明の効果】

【0012】

本発明によれば、P型シリコン層上においてシリサイド層を不連続としていることにより、不純物の相互拡散によるゲート電極の抵抗値の増加を抑制することができると共に、シリサイド層の不連続部分に露出したP型シリコン層の表面と不連続なシリサイド層の表面を連続的にシリコン膜で覆うことにより、P型ポリメタルゲート電極(第2のゲート電極)を低シート抵抗にすることが可能となる。

【0013】

上記第1及び第2のシリコン膜としては、ノンドープのシリコン膜を用いることが好ましく、これによりP型ポリメタルゲート電極の電気抵抗のより高い低減効果が期待できる。これは、金属窒化層がP型不純物を多く含むシリコン層と接した場合、シリコン層に含まれるP型不純物によって金属窒化層とシリコン層との反応が促進されて、厚い金属シリサイド窒化層が形成されるのに対し、ノンドープのシリコン膜は金属窒化層との反応が少ないため、金属シリサイド窒化膜が形成されても、その膜厚をごく薄くすることができるためと考えられる。

【発明を実施するための最良の形態】

【0014】

以下、添付図面を参照しながら、本発明の好ましい実施の形態について説明する。

【0015】

図1乃至図10は、本発明の実施の形態に係るポリメタルゲート/デュアルゲート構造のゲート電極を備えたNチャネルトランジスタ及びPチャネルトランジスタの製造工程を概略的に示す工程図である。図1乃至10において、「領域N」はN型ポリメタルゲート電極を含むNチャネルトランジスタを形成する領域を表し、「領域P」はP型ポリメタルゲート電極を含むPチャネルトランジスタを形成する領域を表している。

【0016】

まず、図1に示すように、半導体基板100の所定の領域に、STI(Shallow Trench Isolation)技術により、素子分離絶縁膜101を形成する。これにより、領域Nと領域Pが分離される。次に、領域NにP型不純物としてボロン(B)をドープしてPウェル102pを形成し、領域PにN型不純物としてリン(P)をドープしてNウェル102nを形成する。

【0017】

次に、図2に示すように、半導体基板100の表面を熱酸化することにより、厚さ約4nmのゲート酸化膜103を形成する。

【0018】

次に、ゲート酸化膜103上に、CVD(Chemical Vapor Deposition)法により、ノンドープのシリコン層104を厚さ約100nm形成する。シリコン層104としては、アモルファスシリコン又は多結晶シリコンのいずれを用いることも可能であるが、表面に凹凸無く形成でき、微細加工に適したアモルファスシリコンを用いるのが好ましい。

【0019】

次に、図3に示すように、領域Pをレジストマスク(図示せず)で覆い、領域Nのシリコン層104に、約10keVの加速エネルギー、約5×1015/cm2のドーズ量でN型不純物としてリン(P)をイオン注入し、領域Nのシリコン層104をN型シリコン層104nにする。続いて、領域Pを覆う上記レジストマスクを除去した後、領域Nを覆うレジストマスク(図示せず)を形成し、領域Pのシリコン層104に、約5keVの加速エネルギー、約1×1015〜5×1015/cm2、好ましくは約3×1015〜5×1015/cm2のドーズ量でP型不純物としてボロン(B)をイオン注入し、領域Pのシリコン層104をP型シリコン層104pにする。

【0020】

次に、フッ酸(HF)と過酸化水素水(H2O2)の混合液を用いて、シリコン層104(N型シリコン層104n及びP型シリコン層104p)の表面に形成された自然酸化膜を除去した後、図4に示すように、シリコン層104上にシリサイド層としてタングステンシリサイド(WSi2)層105を形成する。WSi2層105は、N型シリコン層104n上においては、N型シリコン層104nの表面全面を覆うWSi2層105sとして形成し、P型シリコン層104p上においては、粒状の複数のWSi2粒子105gが半導体基板の表面と略平行な方向に不連続に配置された状態となるように形成する。このように、WSi2層105をP型シリコン層104p上において不連続にすることにより、P型シリコン層104pに含まれるP型不純物とN型シリコン層104nに含まれるN型不純物が、WSi2層105を介して相互拡散することを抑制できる。

【0021】

WSi2層105は、CVD法により、反応室の圧力を約30〜100Pa、半導体基板100の温度を約550℃とし、流量約200sccmのジクロロシラン(SiH2Cl2)と流量約2sccmの六フッ化タングステン(WF6)とをそれぞれ供給し、約30秒間反応させることにより形成する。これにより、WSi2層105は、上述のように、N型シリコン層104n上においては連続膜として形成され、P型シリコン層104p上においては、P型シリコン層104p中のP型不純物の影響により、不連続な膜として形成される。このとき、N型シリコン層104n上に形成されるWSi2層105sの堆積膜厚が約3〜10nm、好ましくは約5〜7nmとなるように形成するのが好ましい。

【0022】

ここで、WSi2粒子105gの好ましい粒径は、約5〜30nmである。これは、粒径が5nmより小さいと、P型ポリメタルゲート電極の界面抵抗が高くなってしまう恐れがあり、30nmを超えると不純物の相互拡散を抑制する効果が弱まるためである。また、複数のWSi2粒子105gの隣接する2つの粒子間の間隔は、約2〜80nmであることが好ましい。間隔が2nmよりも狭いと、隣接するWSi粒子105g同士が接近しすぎて不純物の相互拡散を抑制できなくなる恐れがあり、80nmを超えると、WSi2が形成されない領域が広くなりすぎてP型ポリメタルゲート電極の界面抵抗が高くなってしまう恐れがあるためである。

【0023】

次に、図5に示すように、CVD法により、WSi2層105s、WSi2粒子105gの不連続部分に露出したP型シリコン層104p上及びWSi2粒子105gの表面上に連続的なノンドープのシリコン膜106を形成する。成膜条件は、WSi2層105を形成するためのガスとして反応室に供給していたWF6を停止し、ジクロロシランの流量を約300sccmにし、アルゴン(Ar)を約800sccmの流量で供給し、半導体基板100の温度を約500℃、反応室の圧力を約50〜300Paとして、約5〜120秒間、好ましくは40〜120秒間とする。シリコン膜106の膜厚は、薄くしすぎると、P型ポリメタルゲート電極においてWSi2層105を不連続にしたことによる抵抗の増大を抑制する効果が十分に得られなくなり、厚くしすぎると、後にこの上に形成する窒化タングステン(WN)層及びタングステン(W)層とWSi2層105及びシリコン層104との導電性が低くなり、N型及びP型ポリメタルゲート電極の抵抗が共に高くなってしまう恐れがある。そのため、シリコン膜106の膜厚は、約0.3〜1.5nmとするのが好ましい。シリコン膜106の膜厚は、反応室の圧力、成膜(処理)時間及びジクロロシランの流量を適宜変更することにより所望の厚さとすることができる。なお、シリコン膜106は、アモルファスシリコン及びポリシリコンのいずれを用いることも可能である。

【0024】

続いて、WSi2層105をCVD法で形成したことによりWSi2層105に残留した塩素やフッ素等のガスを除去する、いわゆる脱ガス処理として、約830℃、N2雰囲気で約30秒間の熱処理(RTA:Rapid Thermal Annealing)を行う。この熱処理によって、同時にN型シリコン層104nに注入されたN型不純物及びP型シリコン層104pに注入されたP型不純物が活性化される。また、アモルファスで形成されたシリコン膜104は、このときポリシリコン膜に変換される。

【0025】

なお、図5においてAで示した部分の拡大図である図11に示すように、上記脱ガスのための熱処理によって、シリコン膜106とWSi2層105(105s,105g)との界面部が反応し、シリサイド層20が形成される場合もあるが、シリサイド層20が形成されたとしても、その膜厚は非常に薄く、シリコン膜106のWSi2層105と反対側の表面までシリサイド化されることはない。

【0026】

次に、図6に示すように、スパッタ法により、シリコン膜106の上に、金属窒化層として厚さ約10nmの窒化タングステン(WN)層107を形成する。

【0027】

続いて、図7に示すように、スパッタ法により、WN層107上に、金属層として厚さ約80nmのタングステン(W)層108を形成する。

【0028】

次に、図8に示すように、CVD法により、W層108上に厚さ約200nmのシリコン窒化膜を形成し、これをゲート電極形状にパターニングして、キャップ絶縁膜109を形成する。

【0029】

続いて、図9に示すように、キャップ絶縁膜109をマスクとして、W層108、WN層107、シリコン膜106、WSi2層105(105s,105g)及びポリシリコン層104(104n,104p)の積層膜をドライエッチングによりパターニングして、領域NにN型ポリシリコン層104nを含むN型ポリメタルゲート電極10nを、領域PにP型ポリシリコン層104pを含むP型ポリメタルゲート電極10pを形成する。

【0030】

次に、このゲートパターニングのためのドライエッチングにより、各ゲート電極の端部がダメージを受けるため、これを改善すべく、熱処理を行い、各ゲート電極のポリシリコン層104の側面に側面酸化膜110を形成してダメージを回復させる。なお、図9においてBで示した部分の拡大図である図12に示すように、この側面酸化膜110形成のための熱処理によって、シリコン膜106とWN層107とが反応し、タングステンシリサイド窒化層(WSiN層)30が形成される。しかしながら、本実施形態によれば、WN層107は、高濃度に不純物を含むP型シリコン層104pとではなく、ノンドープのシリコン膜106と接してこの膜と反応するため、形成されるWSiN層30は非常に薄い膜となり、従って、P型ポリメタルゲート電極10pの電気抵抗が増大するのを抑制することができる。これは、WN層107がP型不純物を多量に含むシリコン層104pと接した状態で熱処理を行った場合(従来技術に相当)、シリコン層104pに含まれる不純物によって両者の反応が促進され、厚いWSiN層が形成され易いのに対し、本実施形態のように、WN層107とノンドープのシリコン膜106とが接している場合は、熱処理を行っても両者の反応が進みにくいためと推測される。

【0031】

次に、領域Pをレジストマスク(図示せず)で覆い、領域NにN型不純物(例えばヒ素(As))を高濃度にイオン注入することにより、N型ソース・ドレイン拡散層111nを形成する。続いて領域Pを覆うレジストマスクを除去した後、領域Nを覆うレジストマスク(図示せず)を形成し、領域PにP型不純物(例えばボロン(B))を高濃度にイオン注入することによりP型ソース・ドレイン拡散層111pを形成する。

【0032】

次に、全面に厚さ約40nmのシリコン窒化膜を形成した後、エッチバックを行って、図10に示すように、N型ポリメタルゲート電極10n及びP型ポリメタルゲート電極10pそれぞれの側面にサイドウォール絶縁膜112を形成する。

【0033】

以上の工程により、領域NにN型ポリメタルゲート電極10nを備えたNチャネルトランジスタが、領域PにP型ポリメタルゲート電極10pを備えたPチャネルトランジスタが完成する。

【0034】

図13に、シリコン膜106のCVDによる成膜時間と、N型ポリメタルゲート電極10nの界面抵抗(N型ポリシリコン層104nとWSi2層105(105s)との接触抵抗)及びP型ポリメタルゲート電極10pの界面抵抗(P型ポリシリコン層104pとWSi2層105(105g)との接触抵抗)との関係を示す。図13において、(p)はP型シリコン層104pとWSi2層105(105g)との界面抵抗、(n)はN型シリコン層104nとWSi2層105(105s)との界面抵抗を示している。N型ポリメタルゲート電極10nにおいては、N型シリコン層104nの表面全面にWSi2層105が形成されているため、界面抵抗(n)はシリコン膜106の成膜時間に関わらず、低くほぼ一定である。一方、P型ポリメタルゲート電極10pにおいては、シリコン膜106の成膜時間が長くなるにつれて界面抵抗(p)を低下させることができることがわかる。具体的には、成膜時間が長くなるに従い界面抵抗は徐々に低下していき、40秒を超えたところからほぼ飽和した状態となっている。

【0035】

図14に、WSi2層105のCVDにおけるWF6の流量と、P型ポリメタルゲート電極10pにおけるWSi2層105のシート抵抗との関係を示す。図14において、(a)はWSi2層105上にシリコン膜106を形成しなかった場合(従来技術による場合)のシート抵抗、(b)は、WSi2層105上にシリコン膜106を形成した場合(本実施形態による場合)のシート抵抗を示している。WF6の流量が多くなるほどWSi2層105の不連続性が高くなるため、WSi2層105上にシリコン膜106を形成しなかった場合のシート抵抗(a)は、WF6の流量の増加につれて高くなる。これに対し、シリコン膜106を形成した場合のシート抵抗(b)は、WF6の流量が多くなっても、すなわちWSi2層105の不連続性が高くなっても、低いシート抵抗を得ることができるといえる。

【0036】

以上説明したように、本実施形態によれば、P型シリコン層104p上においてWSi2層105を不連続としていることにより、不純物の相互拡散によるゲート電極の抵抗値の増加を抑制することができると共に、WSi2層105の不連続部分に露出したP型シリコン層104pの表面と不連続なWSi2層105(WSi2粒子105g)の表面を連続的にシリコン膜106で覆うことにより、P型ポリメタルゲート電極10pを低抵抗にすることが可能となる。

【0037】

以上、本発明の好ましい実施の形態について説明したが、本発明は、上記の実施形態に限定されることなく、本発明の主旨を逸脱しない範囲で種々の変更が可能であり、それらも本発明の範囲内に包含されるものであることはいうまでもない。

【0038】

例えば、上記実施形態においては、金属層としてタングステン(W)を、金属窒化層としてタングステン窒化(WN)層を、シリサイド層としてタングステンシリサイド(WSi2)層を用いた例を示したが、これに代えて、コバルト(Co)、チタン(Ti)、ニッケル(Ni)又はタンタル(Ta)等他の高融点金属とこれらの窒化層及びシリサイド層を用いることも可能である。

【0039】

また、シリコン膜106はノンドープに限らず、図12に示すWSiN層30(金属シリサイド窒化層)が厚く形成されてP型ポリメタルゲート電極の界面抵抗が増大することのない範囲であれば、低濃度に不純物を含んでいてもよい。

【0040】

また、WSi2層の脱ガスのための熱処理は、シリコン膜106の形成前に行ってもよい。

【0041】

さらに、上記実施形態においては、WSi2層105の成膜に引き続き、同じCVD装置において、WSi2層105の成膜に用いたジクロロシランを用いてシリコン膜106を成膜する例を示したが、これに限らず、例えば、WSi2層105の成膜後、半導体基板を別のCVD装置に移し、モノシラン(SiH4)を用いたCVD法により成膜することも可能である。

【図面の簡単な説明】

【0042】

【図1】本発明の好ましい実施形態による半導体装置の製造方法の一工程(素子分離絶縁膜101の形成〜Pウェル102p、Nウェル102nの形成)を示す断面図である。

【図2】本発明の好ましい実施形態による半導体装置の製造方法の一工程(ゲート酸化膜103の形成〜シリコン層104の形成)を示す断面図である。

【図3】本発明の好ましい実施形態による半導体装置の製造方法の一工程(N型シリコン層104n及びP型シリコン層104pの形成)を示す断面図である。

【図4】本発明の好ましい実施形態による半導体装置の製造方法の一工程(WSi2層105の形成)を示す断面図である。

【図5】本発明の好ましい実施形態による半導体装置の製造方法の一工程(シリコン膜106の形成)を示す断面図である。

【図6】本発明の好ましい実施形態による半導体装置の製造方法の一工程(WN層107の形成)を示す断面図である。

【図7】本発明の好ましい実施形態による半導体装置の製造方法の一工程(W層108の形成)を示す断面図である。

【図8】本発明の好ましい実施形態による半導体装置の製造方法の一工程(キャップ絶縁膜109の形成)を示す断面図である。

【図9】本発明の好ましい実施形態による半導体装置の製造方法の一工程(ゲートパターニング〜N型ソース・ドレイン拡散層111n及びP型ソース・ドレイン拡散層111pの形成)を示す断面図である。

【図10】本発明の好ましい実施形態による半導体装置の製造方法の一工程(サイドウォール絶縁膜112の形成)を示す断面図である。

【図11】本発明の好ましい実施形態による半導体装置の製造方法の図5の工程におけるA部の部分拡大図である。

【図12】本発明の好ましい実施形態による半導体装置の製造方法の図8の工程におけるB部の部分拡大図である。

【図13】シリコン膜106のCVDによる形成における成膜時間と、N型ポリメタルゲート電極10n及びP型ポリメタルゲート電極10pの界面抵抗との関係を示すグラフである。

【図14】WSi2層105のCVDにおけるWF6の流量と、P型ポリメタルゲート電極10pにおけるWSi2層105のシート抵抗との関係を示すグラフである。

【符号の説明】

【0043】

100 半導体基板

101 素子分離絶縁膜

102n ウェル

102p ウェル

103 ゲート酸化膜

104 シリコン層

104n N型シリコン層

104p P型シリコン層

105(105s,105g) WSi2層

106 シリコン膜

107 WN層

108 W層

109 キャップ絶縁膜

110 側面酸化膜

10n 型ポリメタルゲート電極

10p 型ポリメタルゲート電極

111n N型ソース・ドレイン拡散層

111p P型ソース・ドレイン拡散層

112 サイドウォール絶縁膜

20 シリサイド層

30 WSiN層

【特許請求の範囲】

【請求項1】

Nチャネルトランジスタ形成領域とPチャネルトランジスタ形成領域とを有する半導体基板と、

前記半導体基板の前記Nチャネルトランジスタ形成領域上に設けられた第1のゲート電極と、

前記半導体基板の前記Pチャネルトランジスタ形成領域上に設けられた第2のゲート電極とを有し、

前記第1のゲート電極が、N型不純物を含むN型シリコン層と、前記N型シリコン層上に形成された第1のシリサイド層と、前記第1のシリサイド層上に形成された第1のシリコン膜と、前記第1のシリコン膜上に形成された第1の金属窒化層と、前記第1の金属窒化層上に形成された第1の金属層とを備え、

前記第2のゲート電極が、P型不純物を含むP型シリコン層と、前記P型シリコン層上に形成され複数の粒状のシリサイドが前記半導体基板の表面と略平行な方向に不連続に配置されてなる第2のシリサイド層と、第2のシリサイド層の前記不連続部分に露出した前記P型シリコン層の表面及び前記第2のシリサイド層の表面上に連続的に形成された第2のシリコン膜と、前記第2のシリコン膜上に形成された第2の金属窒化層と、前記第2の金属窒化層上に形成された第2の金属層とを備えることを特徴とする半導体装置。

【請求項2】

前記第1及び第2のシリコン膜がノンドープであることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記シリサイド層、前記金属窒化層及び前記金属層が同一の高融点金属を含むことを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記高融点金属が、タングステン(W)、コバルト(Co)、チタン(Ti)、ニッケル(Ni)及びタンタル(Ta)のいずれかであることを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

【請求項5】

前記P型不純物がボロン(B)であることを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

半導体基板のNチャネルトランジスタ形成領域上にN型不純物を含むN型シリコン層を形成し、前記半導体基板のPチャネルトランジスタ形成領域上にP型不純物を含むP型シリコン層を形成する第1の工程と、

前記N型シリコン層上に第1のシリサイド層を形成し、前記P型シリコン層上に複数の粒状のシリサイドが前記半導体基板の表面と略平行な方向に不連続に配置されてなる第2のシリサイド層を形成する第2の工程と、

前記第1のシリサイド層上、前記第2のシリサイド層の前記不連続部分に露出した前記P型シリコン層の表面及び前記第2のシリサイド層の表面上に連続的なシリコン膜を形成する第3の工程と、

前記シリコン膜上に金属窒化層を形成する第4の工程と、

前記金属窒化層上に金属層を形成する第5の工程と、

前記金属層、前記金属窒化層、前記シリコン膜、前記第1のシリサイド層、前記第2のシリサイド層、前記N型シリコン層及び前記P型シリコン層をパターニングして、前記Nチャネルトランジスタ形成領域に前記N型シリコン層を含む第1のゲート電極を、前記Pチャネルトランジスタ形成領域に前記P型シリコン層を含む第2のゲート電極をそれぞれ形成する第6の工程とを備えることを特徴とする半導体装置の製造方法。

【請求項7】

前記シリコン膜がノンドープであることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記第3の工程で形成される前記シリコン膜の膜厚が0.3〜1.5nmであることを特徴とする請求項6又は7に記載の半導体装置の製造方法。

【請求項9】

前記シリコン膜は、CVD法により50〜300Paの圧力下で堆積されることを特徴とする請求項6乃至8のいずれか一項に記載の半導体装置の製造方法。

【請求項10】

前記シリコン膜の堆積は5〜120sec行われることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

前記第4の工程の前に、前記第3の工程において前記第1及び第2のシリサイド層に含まれた残留ガスを除去するための熱処理を行うことを特徴とする請求項6乃至10のいずれか一項に記載の半導体装置の製造方法。

【請求項12】

前記熱処理によって、前記シリコン膜の少なくとも前記第1及び第2のシリサイド層との界面部がシリサイド化することを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項13】

前記第1のシリサイド層、前記第2のシリサイド層、前記金属窒化層及び前記金属層が同一の高融点金属を含むことを特徴とする請求項6乃至12のいずれか一項に記載の半導体装置の製造方法。

【請求項14】

前記高融点金属が、タングステン(W)、コバルト(Co)、チタン(Ti)、ニッケル(Ni)及びタンタル(Ta)のいずれかであることを特徴とする請求項13に記載の半導体装置の製造方法。

【請求項15】

前記P型不純物がボロン(B)であることを特徴とする請求項6乃至14のいずれか一項に記載の半導体装置の製造方法。

【請求項1】

Nチャネルトランジスタ形成領域とPチャネルトランジスタ形成領域とを有する半導体基板と、

前記半導体基板の前記Nチャネルトランジスタ形成領域上に設けられた第1のゲート電極と、

前記半導体基板の前記Pチャネルトランジスタ形成領域上に設けられた第2のゲート電極とを有し、

前記第1のゲート電極が、N型不純物を含むN型シリコン層と、前記N型シリコン層上に形成された第1のシリサイド層と、前記第1のシリサイド層上に形成された第1のシリコン膜と、前記第1のシリコン膜上に形成された第1の金属窒化層と、前記第1の金属窒化層上に形成された第1の金属層とを備え、

前記第2のゲート電極が、P型不純物を含むP型シリコン層と、前記P型シリコン層上に形成され複数の粒状のシリサイドが前記半導体基板の表面と略平行な方向に不連続に配置されてなる第2のシリサイド層と、第2のシリサイド層の前記不連続部分に露出した前記P型シリコン層の表面及び前記第2のシリサイド層の表面上に連続的に形成された第2のシリコン膜と、前記第2のシリコン膜上に形成された第2の金属窒化層と、前記第2の金属窒化層上に形成された第2の金属層とを備えることを特徴とする半導体装置。

【請求項2】

前記第1及び第2のシリコン膜がノンドープであることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記シリサイド層、前記金属窒化層及び前記金属層が同一の高融点金属を含むことを特徴とする請求項1又は2に記載の半導体装置。

【請求項4】

前記高融点金属が、タングステン(W)、コバルト(Co)、チタン(Ti)、ニッケル(Ni)及びタンタル(Ta)のいずれかであることを特徴とする請求項1乃至3のいずれか一項に記載の半導体装置。

【請求項5】

前記P型不純物がボロン(B)であることを特徴とする請求項1乃至4のいずれか一項に記載の半導体装置。

【請求項6】

半導体基板のNチャネルトランジスタ形成領域上にN型不純物を含むN型シリコン層を形成し、前記半導体基板のPチャネルトランジスタ形成領域上にP型不純物を含むP型シリコン層を形成する第1の工程と、

前記N型シリコン層上に第1のシリサイド層を形成し、前記P型シリコン層上に複数の粒状のシリサイドが前記半導体基板の表面と略平行な方向に不連続に配置されてなる第2のシリサイド層を形成する第2の工程と、

前記第1のシリサイド層上、前記第2のシリサイド層の前記不連続部分に露出した前記P型シリコン層の表面及び前記第2のシリサイド層の表面上に連続的なシリコン膜を形成する第3の工程と、

前記シリコン膜上に金属窒化層を形成する第4の工程と、

前記金属窒化層上に金属層を形成する第5の工程と、

前記金属層、前記金属窒化層、前記シリコン膜、前記第1のシリサイド層、前記第2のシリサイド層、前記N型シリコン層及び前記P型シリコン層をパターニングして、前記Nチャネルトランジスタ形成領域に前記N型シリコン層を含む第1のゲート電極を、前記Pチャネルトランジスタ形成領域に前記P型シリコン層を含む第2のゲート電極をそれぞれ形成する第6の工程とを備えることを特徴とする半導体装置の製造方法。

【請求項7】

前記シリコン膜がノンドープであることを特徴とする請求項6に記載の半導体装置の製造方法。

【請求項8】

前記第3の工程で形成される前記シリコン膜の膜厚が0.3〜1.5nmであることを特徴とする請求項6又は7に記載の半導体装置の製造方法。

【請求項9】

前記シリコン膜は、CVD法により50〜300Paの圧力下で堆積されることを特徴とする請求項6乃至8のいずれか一項に記載の半導体装置の製造方法。

【請求項10】

前記シリコン膜の堆積は5〜120sec行われることを特徴とする請求項9に記載の半導体装置の製造方法。

【請求項11】

前記第4の工程の前に、前記第3の工程において前記第1及び第2のシリサイド層に含まれた残留ガスを除去するための熱処理を行うことを特徴とする請求項6乃至10のいずれか一項に記載の半導体装置の製造方法。

【請求項12】

前記熱処理によって、前記シリコン膜の少なくとも前記第1及び第2のシリサイド層との界面部がシリサイド化することを特徴とする請求項11に記載の半導体装置の製造方法。

【請求項13】

前記第1のシリサイド層、前記第2のシリサイド層、前記金属窒化層及び前記金属層が同一の高融点金属を含むことを特徴とする請求項6乃至12のいずれか一項に記載の半導体装置の製造方法。

【請求項14】

前記高融点金属が、タングステン(W)、コバルト(Co)、チタン(Ti)、ニッケル(Ni)及びタンタル(Ta)のいずれかであることを特徴とする請求項13に記載の半導体装置の製造方法。

【請求項15】

前記P型不純物がボロン(B)であることを特徴とする請求項6乃至14のいずれか一項に記載の半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2007−5355(P2007−5355A)

【公開日】平成19年1月11日(2007.1.11)

【国際特許分類】

【出願番号】特願2005−180427(P2005−180427)

【出願日】平成17年6月21日(2005.6.21)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

【公開日】平成19年1月11日(2007.1.11)

【国際特許分類】

【出願日】平成17年6月21日(2005.6.21)

【出願人】(500174247)エルピーダメモリ株式会社 (2,599)

【Fターム(参考)】

[ Back to top ]