Fターム[5F140BF56]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | マスク性能の向上(プロセス時を含む) (49)

Fターム[5F140BF56]に分類される特許

1 - 20 / 49

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

プラズマ窒化処理方法、プラズマ窒化処理装置および半導体装置の製造方法

【課題】選択的に窒化物膜を形成する。

【解決手段】処理容器2内に窒素含有ガスを供給し、処理容器2内の圧力を133Pa以上1333Pa以下の範囲内に設定して、処理容器2内に窒素含有プラズマを生成し、該窒素含有プラズマによって、シリコンを含有する第2の部分100Bの表面100Baを窒化させずに、タングステンを含有する第1の部分100Aの表面100Aaを選択的に窒化して、第1の部分100Aの表面100Aaに窒化タングステン膜107を形成する。

(もっと読む)

半導体装置の製造方法

【課題】基板に対して斜め方向からイオン注入を行う工程を含む半導体装置の製造方法においてゲート電極サイズの縮小化とリーク電流特性の改善を両立することができる製造方法を提供する。

【解決手段】

半導体基板の表面にゲート電極を形成する。ゲート電極のゲート長方向と交差するゲート幅方向における両端面を被覆するレジストマスクを形成する。半導体基板にゲート長方向成分およびゲート幅方向成分を有する注入方向で不純物イオンを注入して半導体基板の表面のゲート電極を挟む両側にゲート電極とオーバーラップした低濃度不純物層を形成する。ゲート電極の側面を覆うサイドウォールを形成する。ゲート電極およびサイドウォールをマスクとして不純物イオンを注入して半導体基板の表面のゲート電極を挟む両側にゲート電極から離間した高濃度不純物層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧を向上した半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、第4半導体領域、ゲート領域、ゲート絶縁膜及び電界緩和領域を備える。第1導電形の第1半導体領域は、第1部分と第1方向に延出した第2部分とを有する。第1導電形の第2半導体領域は、第1部分上の第3部分と第2部分と隣接する第4部分とを有する。第2導電形の第3半導体領域は、第3部分上の第5部分と第4部分と隣接する第6部分とを有する。第1導電形の第4半導体領域は、第5部分上で第6部分と隣接する。ゲート領域は、第2半導体領域、第3半導体領域及び第4半導体領域を第2方向に貫通するトレンチ内に設けられる。ゲート絶縁膜は、トレンチ内壁とゲート領域との間に設けられる。第2導電形の電界緩和領域は、第3部分と第5部分との間に設けられ、第3半導体領域よりも不純物濃度が低い。

(もっと読む)

半導体装置の製造方法

【課題】溝部を絶縁膜で埋設する際に、溝部のアスペクト比が大きい場合であっても、内部にボイドを残存させることなく、溝部内に絶縁膜を充填する。これにより微細化した半導体装置の製造を容易に行うことを可能とする。

【解決手段】隣り合う凸部の間に形成される溝部の上端部においてオーバーハング形状を有すると共に、溝部の上部にボイドを有するように溝部内に溝部用絶縁膜を形成する。凸部の高さ方向に対して斜め方向から、溝部用絶縁膜に不純物をイオン注入することにより、溝部内に形成された溝部用絶縁膜の一部に不純物をドープする。溝部用絶縁膜の不純物がドープされた部分を除去した後、溝部内に溝部用絶縁膜を充填する。

(もっと読む)

半導体装置の製造方法

【課題】工程を増加することなく、エクステンション領域をゲート端から遠ざけ、実効ゲート長の拡大を図ると同時に、狭ピッチ化に対応する。

【解決手段】裾引き状のオフセットサイドウォール6aをマスクにエクステンション注入を行い、エクステンション領域7を形成し、オフセットサイドウォール6a上にソース・ドレイン注入用のサイドウォール9を形成し、ソース・ドレイン領域10を形成する。

(もっと読む)

半導体装置の製造方法

【課題】工程数が多く、煩雑になる問題を解決する半導体装置の製造方法を提供する。

【解決手段】半導体基板1に第1絶縁膜2を形成し、第1領域Aに第1導電型の第1ウエル層31を形成し、第1領域A以外の第1絶縁膜2上に第1半導体膜3を形成し、第1ウエル層31にトランジスタを形成し、第1半導体膜3及び第1領域Aの第1絶縁膜2の上に、トランジスタのビットコンタクトを兼ねる第2半導体膜7を形成する工程、第2半導体膜7上に、第2領域用B1のマスク8を積層してから、第1または第2導電型ドーパントを注入して第2ウエル層32を形成し、次いで、第2領域B1の少なくとも第2半導体膜7に、ドーパントを注入する工程、第2半導体膜7上に導電膜を積層してから、第1、第2半導体膜3,7及び導電膜を部分的にエッチングして、第1領域Aにトランジスタのビット配線層を、第2領域B1,B2に別の配線層を形成する工程、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】メモリセルMCは、半導体基板1の主面上のゲート絶縁膜5を介して設けられたコントロールゲート電極CGと、コントロールゲート電極CGの側面および半導体基板1の主面に沿って設けられたONO膜9と、ONO膜9を介してコントロールゲート電極CGの側面および半導体基板1の主面上に設けられたメモリゲート電極MGとを有する。コントロールゲート電極CGおよびメモリゲート電極MGの上部には、シリサイド膜15およびシリサイド膜15の表面の酸化によって形成された絶縁膜51が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】バリアメタルの膜厚を抑制しながらメタルゲートの拡散性材料が高誘電率誘電体に拡散することを防ぐ。

【解決手段】半導体装置がゲート積層体構造を含む。ゲート積層体構造は、半導体基板5の上に形成された界面層4と、界面層4の上に形成された高誘電率誘電体3と、拡散性材料と不純物金属を含み、高誘電率誘電体の上方に形成されたシリサイドゲート1と、拡散性材料に対するバリア効果を持ち、高誘電率誘電体3とシリサイドゲート1の間に形成されたバリアメタル2とを備えている。不純物金属は、シリサイドゲート1の拡散性材料が高誘電率誘電体に導入されることを防ぐことができるような、拡散性材料に対するバリア効果を有している。

(もっと読む)

マルチフィン高さを有するFinFET

【課題】マルチフィン高さを有するFinFETを提供する。

【解決手段】集積回路構造は、半導体基板と、半導体基板上のFinFETと、を含む。FinFETは、半導体フィンと、半導体フィンの頂面および側壁上のゲート誘電体と、ゲート誘電体上のゲート電極と、半導体フィン一端に位置するソース/ドレイン領域と、を備える。一対の第一STI領域は、ソース/ドレイン領域の一部分の真下に位置する部分を含み、一対の第一STI領域は、半導体ストリップにより分離され、且つ、半導体ストリップに隣接する。一対の第一STI領域は、更に、第一頂面を有する。一対の第二STI領域は、ゲート電極の真下に位置する部分を含み、一対の第二STI領域は、半導体ストリップにより互いに分離され、且つ、半導体ストリップに隣接する。第二STI領域は、第一頂面より高い第二頂面を有する。

(もっと読む)

埋め込みストレッサを有する高性能FETを形成するための方法および構造

【課題】 高性能の半導体構造およびかかる構造を製造する方法を提供する。

【解決手段】 半導体構造は、半導体基板12の上面14上に位置する、例えばFETのような少なくとも1つのゲート・スタック18を含む。構造は更に、少なくとも1つのゲート・スタックのチャネル40上にひずみを誘発する第1のエピタキシ半導体材料34を含む。第1のエピタキシ半導体材料は、少なくとも1つのゲート・スタックの対向側に存在する基板内の1対のくぼみ領域28の実質的に内部で少なくとも1つのゲート・スタックの設置場所に位置する。くぼみ領域の各々において第1のエピタキシ半導体材料の上面内に拡散拡張領域38が位置する。構造は更に、拡散拡張領域の上面上に位置する第2のエピタキシ半導体材料36を含む。第2のエピタキシ半導体材料は、第1のエピタキシ半導体材料よりも高いドーパント濃度を有する。

(もっと読む)

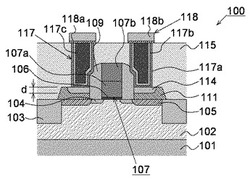

半導体装置及びその製造方法

【課題】トレンチゲート型FIN−FETにおいて、微細化に対してもFIN型トランジスタの利点を十分に発揮し、また、活性領域において十分なコンタクト面積を確保し、オン電流の低下を抑制したトレンチゲート型FIN−FETを提供する。

【解決手段】チャネル領域のFIN幅(162)を活性領域の幅(161)よりも狭くする。

(もっと読む)

不純物活性化方法、半導体装置の製造方法

【課題】低いシート抵抗を得る不純物活性化方法、および、ソース・ドレイン拡張部を均一な深さで再現性よく形成する製造方法を提供。

【解決手段】半導体基板21において半導体基板21よりも不純物濃度が高いボロンイオン注入層43が形成されており、ボロンイオン注入層43にパルス幅が10〜1000フェムト秒のパルスレーザー光を照射して、ボロンイオン注入層43を活性化させる。パルスレーザー光におけるパルス幅、レーザーフルーエンスおよび照射パルス数を含む照射条件を変更することにより、パルスレーザー光照射後のボロンイオン注入層43のシート抵抗を制御する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】同一の工程で、同一半導体基板上に異なる構造のトランジスタを形成する半導体装置の提供。

【解決手段】半導体基板上に第一及び第二のゲート電極40,41を形成する工程と、第一のゲート電極の側壁面に第一の絶縁層122を形成するとともに、第二のゲート電極のゲート幅方向両側の半導体基板上にエピタキシャル成長層9aを形成する工程と、第二のゲート電極の側壁面に第二の絶縁層を形成する工程と、第一の絶縁層及び第二の絶縁層を覆うように第三の絶縁層を形成する工程と、第二の絶縁層を覆う第三の絶縁層を除去する工程と、第一のゲート電極のゲート幅方向両側の半導体基板及びエピタキシャル成長層にそれぞれ不純物を拡散させて、第一及び第二の不純物拡散領域6,8を形成する工程と、第一及び第二の不純物拡散領域にコンタクトプラグ12,15を接続させる工程と、を具備してなることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:ハフニウムおよび/またはジルコニウムを含む第1の酸化物材料を含む高誘電体層と;前記高誘電体層の上部に蒸着され、ランタン、ランタニド、および/または、アルミニウムを含む第2の酸化物材料を含むキャップ層と、を備えたスタックを準備する工程と;酸化剤を含む水溶液である液体Aを前記半導体ウエハの表面に供給する工程SAと;工程SAの後に、6未満のpH値の液体である液体Bを前記半導体ウエハの前記表面に供給する工程SBと;工程SBの後に、少なくとも10ppmのフッ素濃度の酸性水溶液である液体Cを前記半導体ウエハの前記表面に供給する工程SCとを備える方法が開示されている。

(もっと読む)

半導体装置の製造方法

【課題】希土類含有複合酸化物膜の新規なエッチング方法を含む、半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、希土類元素と、希土類でない他の金属元素と、Oとを含む希土類含有複合酸化物膜を形成する工程と、希土類含有複合酸化物膜に対し、フッ素を含まない酸によるエッチングと、他の金属元素の酸化物を溶解するフッ素含有溶液によるエッチングとを、交互に複数回行なうエッチング工程とを有する。

(もっと読む)

L形状スペーサを使用した非対称的電界効果トランジスタの製造及び構成体

【課題】 非対称的電界効果トランジスタ(102)の製造は、半導体ボディのボディ物質のチャンネルゾーン(284)の上方でそれからゲート誘電体層(300)によって垂直方向に分離されているゲート電極(302)を画定することとなる。

【解決手段】 該ゲート電極をドーパント阻止用シールドとして使用して、半導体ドーパントを該ボディ物質内に導入させて、一層高度にドープしたポケット部分(290)を画定する。該ゲート電極に沿ってスペーサ(304T)を設ける。該スペーサは、(i)該ゲート電極に沿って位置されている誘電体部分、(ii)該半導体ボディに沿って位置されている誘電体部分、及び(iii)該他の2つのスペーサ部分の間の空間をほぼ占有するフィラー部分(SC)、を包含している。該ゲート電極及び該スペーサをドーパント阻止用シールドとして使用して、半導体ドーパントを該半導体ボディ内に導入させて、一対のソース/ドレイン部分(280M及び282M)を画定する。該フィラースペーサ部分を除去して該スペーサをL形状(304)へ変換させる。一対の電気的コンタクト(310及び312)を夫々該主要ソース/ドレイン部分に対して形成する。

(もっと読む)

複数の局所的濃度最大によって画定されたソース/ドレイン延長部を有する電界効果トランジスタの構成及び製造

【課題】 絶縁ゲート電界効果トランジスタ(100W)は、半導体ボディのボディ物質(180)のチャンネルゾーン(244)によって横方向に分離されているソース(980)及びドレイン(242)を有している。

【解決手段】 ゲート電極(262)が該チャンネルゾーンの上方でゲート誘電体層(260)の上側に位置している。該ボディ物質の一層高度にドープしたポケット部分(250)が、通常、該ソースのみにほぼ沿って延在しており、従って該IGFETは非対称的装置である。該ソースを画定する半導体ドーパントはソース延長部を画定する場合に複数の局所的濃度最大に到達する。2つのこの様な局所的濃度最大に到達する半導体ドーパントで該ソース延長部を画定する場合に関与する手順は、3個の絶縁ゲート電界効果トランジスタ用の相互に異なる特性のソース/ドレイン延長部を2つのソース/ドレイン延長部ドーピング操作のみで画定することを可能とする。

(もっと読む)

1 - 20 / 49

[ Back to top ]