Fターム[5F140BJ13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 2層目より上層の材料 (1,508)

Fターム[5F140BJ13]の下位に属するFターム

Fターム[5F140BJ13]に分類される特許

41 - 48 / 48

半導体装置及びその製造方法

【課題】 ゲート電極中への砒素のイオン注入を抑制することができる半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体基板上の素子形成領域にゲート絶縁膜を介して形成された砒素を含むシリコン膜5とNiシリサイド層11の積層構造からなるゲート電極5と、ゲート電極5の側面に形成された絶縁膜6、7からなるサイドウォール8と、ゲート電極5の両側の素子形成領域に形成された砒素を含むソース及びドレイン層9、10と、ソース及びドレイン層9、10上に形成されたNiシリサイド層11′とを備えている。また、ゲート電極5内に含まれる砒素のピーク濃度が、ソース及びドレイン層9、10に含まれる砒素のピーク濃度の10分の1以下であることを特徴としている。

(もっと読む)

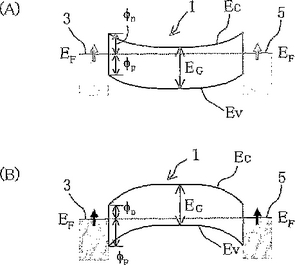

スピン依存伝達特性を有する電界効果トランジスタ及びそれを用いた不揮発性メモリ

ゲート電圧VGSの印加によって、強磁性ソースにおける金属的スピンバンドによるショットキー障壁幅が減少し、この金属的スピンバンドからのアップスピン電子がチャネル領域にトンネル注入される。このとき強磁性ソース3aの半導体的スピンバンドによるエネルギー障壁により非磁性コンタクト3bからダウンスピン電子は注入されない。すなわち、強磁性ソース3aからはチャネル層へアップスピン電子のみが注入される。強磁性ソース3aと強磁性ドレイン5aとが平行磁化の場合では、アップスピン電子は強磁性ドレインの金属的スピンバンドを伝導してドレイン電流となるが、反平行磁化を持つ場合では、アップスピン電子は強磁性ドレイン5aにおける半導体的スピンバンドによる高さΔEcのエネルギー障壁よって強磁性ドレイン5aを伝導することができない。 上記動作原理のMISFETに基づき、高性能・高集積密度の不揮発性メモリを構成することができる。  (もっと読む)

(もっと読む)

垂直導電パワー電子デバイス及びその実現方法

【課題】出力抵抗、熱抵抗、サイズ及びゲート変化値を低減した垂直導電電子パワーデバイスを提供する。

【解決手段】半導体基板10上のエピタキシャル層40内にゲート領域20、ソース領域25、ドレイン領域30、及び第1メタライゼーション・レベルによるゲート部21、ソース部26、ドレイン部31、及び第2メタライゼーション・レベルによるゲート端子/パッド、ソース端子/パッド65、ドレイン端子/パッドを具える。このデバイスは、基板10に対して垂直に延びドレイン領域30の第1領域及び第2領域の両方の下に配置されたシンカーSの格子によって形成されるシンカー構造45を具えて、このシンカー構造は、ソース領域25から基板10を通ってドレイン領域30に向かう電流用の導電チャンネルとして作用する。

(もっと読む)

カーボンナノチューブ構造体、半導体装置、および半導体パッケージ

【課題】 カーボンナノチューブ束の密度を向上し、電気抵抗や熱抵抗の低減を図るカーボンナノチューブ構造体、半導体装置、および半導体パッケージを提供する。

【解決手段】 第1配線層21、層間絶縁膜22、第2配線層23が順次積層され、層間絶縁膜22を貫通するビアホール24に、第1配線層21と第2配線層23を電気的に接続するカーボンナノチューブ束25が形成されてなるビア26から構成する。カーボンナノチューブ束25は、第1配線層21の凹部28の側面および底面に形成された触媒層29から成長させ、側面から成長したカーボンナノチューブ25aによりカーボンナノチューブ束25の密度を向上する。

(もっと読む)

半導体装置およびその製造方法

【課題】低電気抵抗化および高信頼性化可能なコンタクトを備え、高速伝送が可能で信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】 コンタクト20、23を、CVD法を用いて、シリサイド膜19、22、シリコン窒化膜15aおよび第1層間絶縁膜15bの内壁に接する表面に、表面からコンタクト内部方向への距離に応じて窒素含有量が減少する組成勾配を有する窒化タングステン部24を形成し、その内側にタングステンが充填されたタングステン部25を形成する。窒化タングステン部24とタングステン部25との界面の酸化や汚染を防止する。

(もっと読む)

絶縁ゲート型電界効果トランジスタの製造方法

【課題】絶縁ゲート型電界効果トランジスタの製造方法において、ゲート−ドレイン間の絶縁不良を増やすことなく、より短時間に効率的にトレンチ埋め込み絶縁膜を形成することのできる絶縁ゲート型電界効果トランジスタの製造方法を提供すること。

【解決手段】第一TEOS酸化膜を前記トレンチ間に凹部が残る厚さに堆積してアニール処理をすることにより前記トレンチ間に第一絶縁膜を形成する工程と、該第一絶縁膜上に第二TEOS酸化膜からなる第二絶縁膜を形成する工程とから前記トレンチ内に埋め込まれる絶縁膜を形成する絶縁ゲート型電界効果トランジスタの製造方法とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 閾値の変動を回避するとともに、電気的ストレスに対する信頼性の高いMOSトランジスタを備えた半導体装置を提供する。

【解決手段】 素子領域を画定する素子分離領域(12)が設けられた半導体基板(11)と、前記半導体基板の前記素子領域に離間して設けられたソース/ドレイン領域(25)と、前記半導体基板の前記素子領域上に設けられたゲート絶縁膜(13,14)と、前記ゲート絶縁膜上に設けられ、半導体を含むゲート電極(15)とを具備する半導体装置である。前記ゲート絶縁膜は、金属および酸素を含有する第1の絶縁膜(13)と、この第1の絶縁膜上に形成され、シリコンおよび酸素を含有する第2の絶縁膜(14)とを含み、前記第2の絶縁膜は、前記ゲート電極との界面における前記金属の含有量が6.6atomic.%未満であることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 小型化を図ることができる半導体装置を提供する。また、放熱効率を向上させた半導体装置を提供する。

【解決手段】 配線基板10の裏面にGND用外部配線12を形成する。そして、このGND用外部配線12に接続する複数のビア18を、配線基板10を貫通するように形成し、配線基板10の主面にHBTを含む高消費電力の第1の半導体チップ19を実装する。第1の半導体チップ19のエミッタバンプ電極19bは、第1の半導体チップ19内に形成された複数のHBTのエミッタ電極に共通接続しており、HBTが並んだ方向に延在している。第1の半導体チップ19は、この延在したエミッタバンプ電極19bに複数のビア18が接続するように配線基板10に実装されている。また、第1の半導体チップ19上に第1の半導体チップ19より発熱量の少ない第2の半導体チップ21を搭載して配線基板10の小型化を図る。

(もっと読む)

41 - 48 / 48

[ Back to top ]