Fターム[5F140BJ14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン電極 (8,852) | 2層目より上層の材料 (1,508) | 半導体 (26)

Fターム[5F140BJ14]に分類される特許

1 - 20 / 26

スイッチ装置

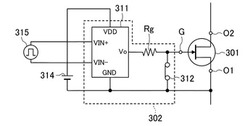

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】高性能なIII−V族MISFETの実現を可能にする、より効果的なIII−V族化合物半導体表面のパッシベーション技術を提供する。

【解決手段】エピタキシャル成長により化合物半導体層をベース基板上に形成するステップと、前記化合物半導体層の表面をセレン化合物を含む洗浄液で洗浄するステップと、前記化合物半導体層の上に絶縁層を形成するステップと、を有する半導体基板の製造方法を提供する。前記セレン化合物として、セレン酸化物が挙げられる。前記セレン酸化物として、H2SeO3が挙げられる。前記洗浄液が、水、アンモニアおよびエタノールからなる群から選択された1以上の物質をさらに含んでもよい。前記化合物半導体層の表面がInxGa1−xAs(0≦x≦1)からなる場合、前記絶縁層がAl2O3からなるものであることが好ましく、Al2O3は、ALD法により形成されることが好ましい。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

電界効果型トランジスタ

【課題】従来の電界効果型トランジスタでは、ソース領域およびドレイン領域に形成する高濃度不純物のイオン注入工程により半導体基板表面がアモルファス化されるため、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、活性化熱処理により結晶欠陥を誘発し、電界効果型トランジスタの信頼性を低下させる問題があった。

【解決手段】本発明の電界効果型トランジスタは、ソース領域およびドレイン領域を構成する部分の上部に高濃度不純物を含有する導電性膜を設ける。高濃度不純物のイオン注入を行う必要がないことから、この領域の半導体基板表面がアモルファス化することがない。これにより、低濃度不純物拡散領域と高濃度不純物拡散領域との境界部において、再結晶化による結晶欠陥の発生を防ぐことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】CMPによるダミーゲート電極の頭出し工程およびCMPによるメタルゲート電極の形成工程を回避できる製造方法を提供する。

【解決手段】シリサイド膜24S,24D上に選択的に、シリコン膜25S,25Dを形成する工程と、側壁絶縁膜23WA,23WBの間にシリコン基板の表面を露出する凹部23Vを形成する工程と、側壁絶縁膜23WA,23WBの表面および露出されたシリコン基板表面を連続して覆うように、誘電体膜を形成する工程と、シリコン基板上に金属または導電性金属窒化物を含む導電膜を、凹部23Vに誘電体膜を介して充填するように形成する工程と、導電膜をエッチバックし、側壁絶縁膜23WA,23WBの間において凹部23Vを誘電体膜を介して充填するゲート電極を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法、半導体装置及びデータ処理システム

【課題】第1配線の比抵抗が小さく、シリサイド異常成長が抑制された半導体装置の製造方法の提供。

【解決手段】第1溝を半導体基板1に設けた後、第1溝内に、シリコンとの間でシリサイドを形成しない材料からなる導体層6と半導体層10とを含む第1配線11を形成して、半導体層と半導体基板とを直接に接触させる工程と、半導体層に含まれるドーパントを半導体基板に拡散させて第1不純物拡散領域13を形成する工程と、第1溝と交差する方向に延在する第2溝を半導体基板に設けることで、第1不純物拡散領域を包含して半導体基板に立設されたピラー部1bを形成する工程と、第2溝の側壁面にゲート絶縁膜16を形成してから、ゲート絶縁膜を介してピラー部に対向する第2配線17を第2溝内に形成する工程と、ピラー部の先端部に、第2不純物拡散領域19を形成する工程と、を具備してなる半導体装置の製造方法を採用する。

(もっと読む)

電磁気素子の製造方法

【課題】レジスト残渣に起因するリーク電流の増大を生じさせることがなく、微細パターンの形成が可能であり、電極のエッジ部分の絶縁膜が薄くなることに起因するリーク電流の増大を抑制することが可能な電磁気素子の製造方法を提供すること。

【解決手段】基板上に、12(CaxSr1-x)O・7Al2O3(0≦x≦1)を含む絶縁膜を形成する絶縁膜形成工程と、絶縁膜の上にアンモニウム塩アルカリ溶液を含む現像液で現像可能な第1フォトレジストを塗布し、第1フォトマスクパターンに応じて第1フォトレジストを露光する第1フォトレジストパターン形成工程と、第1フォトレジストをアンモニウム塩アルカリ溶液を含む現像液に接触させ、第1フォトレジストの可溶部分の溶解と同時に、絶縁膜をエッチングする現像・エッチング工程とを備えた電磁気素子の製造方法。

(もっと読む)

半導体装置、ウエハ構造体および半導体装置の製造方法

【課題】放熱効率を向上し且つ歩留りや信頼性の低下を防止することが可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】裏面に凹部DP1が形成されたシリコン基板101と、シリコン基板101における裏面と反対側の上面上に成長されたp型半導体層103と、p型半導体層103の上方または側方に互いに離間して形成されたソース電極108sおよびドレイン電極108dと、を含むMOSFETと、を備える。p型半導体層103は、シリコン基板101に対して格子定数および熱膨張係数のうち少なくとも1つが異なる。凹部DP1は、シリコン基板101の厚み方向から見て少なくともソース電極108sおよびドレイン電極108dで挟まれた領域を内包する領域に形成されている。

(もっと読む)

コンタクト構造物の形成方法、及びこれを利用した半導体装置の製造方法

【課題】コンタクト構造物の形成方法及びこれを利用した半導体装置の製造方法を提供する。

【解決手段】コンタクト領域103を有する対象体100上に絶縁層106を形成した後、絶縁層106をエッチングしてコンタクト領域103を露出させる開口を形成する。露出されたコンタクト領域103上にシリコン及び酸素を含む物質膜を形成した後、シリコン及び酸素を含む物質膜上に金属膜を形成する。シリコン及び酸素を含有する物質膜と金属膜を反応させて、少なくともコンタクト領域103上に金属酸化物シリサイド膜121を形成した後、金属酸化物シリサイド膜121上の開口を埋める導電膜を形成する。コンタクト領域とコンタクトとの間に金属、シリコン、及び酸素が三成分系を成す金属酸化物シリサイド膜を均一に形成することができるため、改善された熱安定性及び電気的特性を有する。

(もっと読む)

半導体装置

【課題】ビット線の容量を小さくし、高速動作が得られるダイナミックランダムアクセスメモリを得ること。

【解決手段】ソース/ドレイン領域の一方になる第1の導電層6の上に、第1の半導体層11、チャネル半導体層12、ソース/ドレイン領域の他方になり、かつストレージノード26にもなる第2の導電層13が設けられている。第2の導電層13の上にキャパシタ絶縁膜21が設けられる。キャパシタ絶縁膜21を介在させて、ストレージノード26の上にセルプレート22が設けられている。

(もっと読む)

GaN系電界効果トランジスタ

【課題】簡易な製造工程によって形成可能なノーマリーオフ型のGaN系FETを提供すること。

【解決手段】本発明においては、ソース電極S直下およびドレイン電極D直下にそれぞれn−AlGaN層16を形成し、さらにn−AlGaN層16の間に位置するチャネル層であるp−GaN層14上に形成される絶縁膜17の上にゲート電極Gを形成することによって、ソース電極Sおよびドレイン電極Dとn−AlGaN層16との接触抵抗を低下させたノーマリーオフ型のGaN系のFET1を実現することができる。

(もっと読む)

電界効果型トランジスタの修復方法、半導体装置の修復方法、半導体装置の作製方法、及び半導体装置

【課題】電界効果型トランジスタのリーク電流を低減し、寿命の向上を図るための簡便な修復方法を提供することを課題とする。また、作製コストの増加を抑え、消費電力が小さく、且つ信頼性の高い半導体装置を提供することを課題とする。

【解決手段】ソース電極又はドレイン電極の一方と、ゲート電極との間に、電気的な衝撃を加える。または、ソース電極又はドレイン電極の一方と、ソース電極又はドレイン電極の他方との間に、電気的な衝撃を加える。これにより、リークパスを絶縁化し、リーク電流を低減することができる。なお、上記の電気的な衝撃は、静電気等の電気パルスであっても良いし、直流電圧、交流電圧、直流電流、交流電流等であっても良い。

(もっと読む)

半導体装置

【課題】高耐圧で、安全動作領域が広く、かつ、熱散逸性がよく、有効コンダクタンスおよび周波数特性が良好なSOIデバイスを提供すること。

【解決手段】半導体装置100において、p-基板101の表面層の一部にはBOX領域102が設けられる。BOX領域102は、ゲート電極110の中心から下ろした垂線Lc付近まで設けられており、ドレイン領域109および拡張ドレイン領域103をp-基板101から分離する。ドレイン領域109の厚さは150nm〜300nmのいずれかであり、BOX領域102の厚さは150nm以上である。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板に形成された電界効果トランジスタのソース領域やドレイン領域に生じる欠陥を抑制する。

【解決手段】半導基板1の主面上にゲート電極7Gを形成した後、ゲート電極7Gをマスクとして不純物を半導体基板1に導入することにより半導体基板1の主面に低濃度層11を形成する。続いて、ゲート電極7Gの側面に第1サイドウォール12および第2サイドウォール13を形成した後、第1サイドウォール12、第2サイドウォールおよびゲート電極7Gをマスクとして半導体基板1に窒素等をイオン打ち込みすることにより、半導体基板1の主面に結晶化抑制領域CCRを形成する。その後、第2サイドウォール13を除去した後、半導体基板1の主面に、ソースおよびドレイン用の高濃度層を形成する。

(もっと読む)

電界効果ヘテロ構造トランジスタ

装置は、電界効果トランジスタFETを含む。FETは、第1の半導体の領域と、第1の半導体の領域上に位置する第2の半導体の層とを含む。層および領域は、半導体ヘテロ構造を形成する。FETはまた、領域および層の1つの上に位置するソースおよびドレイン電極と、半導体ヘテロ構造のチャネル部の導電率を制御するように配置されたゲート電極とを含む。チャネル部は、ソース電極とドレイン電極の間に位置する。ゲート電極は、チャネル部、ならびにソースおよびドレイン電極の一部分の垂直上方に位置する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】応力の制御性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板の主表面上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極を挟むように前記半導体基板中に隔離して設けられたソースおよびドレインとを備えた絶縁ゲート型電界効果トランジスタP1と、前記ソース上に設けられた第1コンタクト配線26と、前記ドレイン上に設けられた第2コンタクト配線27と、前記ゲート電極上を覆うように設けられ、一端および他端が前記第1、第2コンタクト配線間に接続された圧電層22とを具備する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 短工期であり低消費電力および高駆動能力、高精度を有するパワーマネージメント半導体装置やアナログ半導体装置の実現を可能とする製造方法を提供する。

【解決手段】 CMOSを含むパワーマネージメント半導体装置やアナログ半導体装置の製造方法において、低濃度ドレインを構成する半導体領域の上方に熱伝導度の大きい物質を付加し、ドレイン領域を拡大することで、サージ入力時でのドレイン領域の熱伝達(熱放出)を向上させることにより局所的な温度上昇を抑えることで、熱破壊を抑止し、トランジスタの設計自由度を高めたパワーマネージメント半導体装置やアナログ半導体装置を実現する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コンタクト構造の煩雑化を抑制しつつ、コンタクト抵抗を低減させる。

【解決手段】エピタキシャル成長により、単結晶半導体層7a、7bをLDD層5a、5b上に選択的に形成し、層間絶縁膜9および単結晶半導体層7a、7bをそれぞれ介してソース層8aおよびドレイン層8bをそれぞれ露出させる開口部10a、10bを形成した後、バリアメタル膜11a、11bをそれぞれ介して埋め込まれたプラグ12a、12bを開口部10a、10b内にそれぞれ形成する。

(もっと読む)

半導体デバイスの製造方法および該方法で得られた半導体デバイス

本発明は、基板(11)と、少なくとも一つの半導体素子(E)を設けた半導体本体(12)とを有し、単結晶シリコン(1)領域を具え、該単結晶シリコン領域(1)の上に金属シリサイド領域(3)を設け、そして金属シリサイド領域(3)の上に低結晶性シリコン領域(4)を設け、その後、低結晶性シリコン領域(4)を加熱することにより高結晶性を有するエピタキシャルシリコン領域(2)に変化させ、その処理の間に金属シリサイド領域(3)を低結晶性シリコン領域(4)の下部からエピタキシャルシリコン領域(2)の上へと移動させることにより、単結晶シリコン領域(1)の上にエピタキシャルシリコン領域(2)を形成する、半導体デバイス(10)の製造方法に関する。上記本発明によれば、金属シリサイド領域(3)より高い位置に、孔(6)を設けた絶縁層(5)を形成し、低結晶性シリコン領域(4)を孔(6)中および絶縁層(5)の上に析出させ、絶縁層(5)上の低結晶性シリコン領域(4)の一部(4A、4B)を平坦化処理により取り除き、その後にエピタキシャルシリコン領域(2)を形成する。この方法では、自己整合方式で金属シリサイドコンタクト(領域)が設けられており、そしてトランジスタのような半導体素子(E)の一部を形成できる、エピタキシャルシリコン領域(2)、好ましくはナノワイヤ(2)が簡単に得られる。  (もっと読む)

(もっと読む)

1 - 20 / 26

[ Back to top ]