Fターム[5F140CA04]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 配線 (1,162) | 材料 (584) | 多結晶 (34)

Fターム[5F140CA04]に分類される特許

1 - 20 / 34

半導体装置およびその製造方法

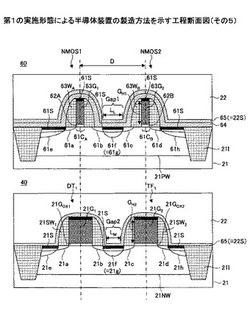

【課題】論理素子のnチャネルMOSトランジスタに十分な膜厚の引張応力膜を形成し、メモリ素子がゲート電極間の層間絶縁膜の埋込不良を生じない製造方法の提供。

【解決手段】論理素子は、第1及び第2のnチャネルMOSトランジスタを含み、第1のゲート高さGH1及び第1のゲート長を有するゲート電極を有し、ゲート電極は第1の間隔Dを有し、メモリ素子は、第3および第4のnチャネルMOSトランジスタを含み、ゲート高さGH2および第2のゲート長を有するゲート電極を含み、論理素子及びメモリ素子は第1の引張応力膜64で覆われ、論理素子は、さらに第2の引張応力膜65で覆われ、論理素子及びメモリ素子のゲート間に形成された引張応力膜の最小距離は各々第1の距離LL及び第1の距離LMで隔てられ、第1のアスペクト比(GH1/LL)と、第2のアスペクト比(GH2/LM)とは略等しい。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極用溝18の底部18cから活性領域の一部が突き出すように形成されたフィン部15と、ゲート電極用溝18及びフィン部15の表面を覆うゲート絶縁膜21と、ゲート電極用溝18の下部に埋め込まれ、ゲート絶縁膜21を介してフィン部15を跨ぐように形成されたゲート電極22と、第1の不純物拡散領域28と、第2の不純物拡散領域29と、フィン部15の表面に設けられた準位形成領域30と、を備える半導体装置10を選択する。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】Y方向に延在するように半導体基板13に設けられ、底面18c及び対向する第1及び第2の側面18a,18bを有するゲート電極用溝18と、ゲート絶縁膜21を介して、ゲート電極用溝18の下部を埋め込むように配置されたゲート電極22と、ゲート電極用溝18を埋め込むように配置され、ゲート電極22の上面22aを覆う埋め込み絶縁膜24と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第1の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように、半導体基板13に設けられた第2の不純物拡散領域29と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】マイクロローディング効果を防止しながら、上層配線となる金属配線のレイアウト制約のない構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3の上に形成されたゲート電極4と、半導体基板1に形成された拡散層5と、半導体基板1の上に形成された絶縁膜7及び絶縁膜8と、絶縁膜及び絶縁膜8を貫通するホール9Dに埋め込まれ、側面を絶縁膜11で覆われた金属材料からなるプラグ12と、絶縁膜8を貫通しないホール10Bに埋め込まれ、絶縁膜11からなる絶縁体10Cと、絶縁膜8の上に形成され、プラグ12と電気的に接続する金属配線13Bとを備えている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

静電気保護素子及びその製造方法

【課題】リーク電流の少ない静電気保護素子を提供する。

【解決手段】半導体基板100nと、半導体基板内に形成され、第1の導電型の不純物が拡散された第1のウェル101と、第1のウェル内に、第1のウェルの一部の領域を挟んで形成され、第2の導電型の不純物が拡散されたコレクタ領域110及びエミッタ領域112と、第1のウェル内に、前記エミッタ領域と分離する第1の分離領域102を挟んで形成され、第1のウェル内に拡散された不純物の濃度よりも高い濃度の、第1の導電型の不純物が拡散されたベース拡散領域114と、前記エミッタ領域下方から前記エミッタ領域と前記ベース拡散領域との間までの第1のウェル内の領域に形成され、第2の導電型の不純物が拡散された拡散領域103aとを備えた静電気保護素子。

(もっと読む)

半導体装置及びその製造方法

【課題】応力絶縁膜により、MISトランジスタの駆動能力が劣化することを防止する。

【解決手段】第1のMISトランジスタpTr1は、第1の活性領域10aにおける第1のサイドウォール19Aの外側方下に設けられたトレンチ22内に形成され、第1の活性領域10aにおけるチャネル領域のゲート長方向に第1の応力を生じさせるシリコン混晶層23を含む第1導電型の第1のソースドレイン領域27aと、第1の活性領域10a上に第1のゲート電極14a、第1のサイドウォール19A及び第1のソースドレイン領域27aを覆うように形成され、第1の応力とは反対の第2の応力を生じさせる応力絶縁膜31とを備えている。シリコン混晶層23の最上面は、第1のゲート電極14a直下に位置する半導体基板10の表面よりも高く形成されている。シリコン混晶層23と第1のサイドウォール19Aとの隙間24には、第1の応力緩和膜28aが形成されている。

(もっと読む)

半導体装置の製造方法

【課題】配線層の加工マージンが大きく、微細化に適した半導体装置の製造方法を提供する。

【解決手段】半導体基板1にゲート電極溝を形成する工程と、ゲート電極溝の内壁面にゲート絶縁膜15を形成する工程と、ゲート電極溝の底部に埋め込みゲート電極23Aを形成する工程と、埋め込みゲート電極23Aの上面を覆うようにゲート電極溝の内部に絶縁膜を埋め込んだ後、エッチバックして当該ゲート電極溝の上部にキャップ絶縁膜22を形成する工程と、半導体基板1の上面に層間絶縁膜24を形成する工程と、層間絶縁膜24にビットコンタクト開口部を形成する工程と、を備え、半導体基板1の上面に層間絶縁膜24を形成する工程が、半導体基板1の上面とキャップ絶縁膜22の上面との間に生じた段差を埋め込むように層間絶縁膜24を成膜するとともに当該層間絶縁膜24の上面を平坦とすることを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】従来の同一サイズの半導体装置と比較してゲート耐圧を向上させるとともに、素子分離層をバーズビークを含まない構造とすることにより素子分割領域の面積を縮小し、素子の微細化を図ることができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板表面に素子形成領域から素子分割領域に亘って延在するLOCOS膜を形成する。素子形成領域内の半導体基板上にLOCOS膜に接続されたゲート酸化膜を形成する。LOCOS膜およびゲート酸化膜を覆うように導電膜を形成する。導電膜を部分的にエッチングしてゲート酸化膜およびLOCOS膜の一部を覆うゲート電極を形成する。導電膜のエッチングによって露出したLOCOS膜を部分的にエッチングしてLOCOS膜を素子分離層とゲート酸化膜の端部を構成する高膜厚部とに分割する。LOCOS膜のエッチングによって露出した半導体基板の表面にイオン注入を行ってゲート電極を挟む位置にドレイン領域およびソース領域を形成する。

(もっと読む)

半導体装置

【課題】電位を印加した溶液中の化学物質の測定の際、リーク電流が半導体基板に流れない膜厚のシリコン酸化膜にてゲート絶縁膜が形成され、容易にシランカップリングによるアミノ酸基の導入が行え、かつ溶液と配線間に流れるリーク電流を抑える溶液測定用半導体センサチップを提供する。

【解決手段】本発明の溶液測定用半導体センサチップは、ゲート絶縁膜が露出されたMOSトランジスタからなり、電位の印加された溶液中に浸して化学物質の検出を、MOSトランジスタに流れる電流変化を検出することで行うものであり、半導体基板上に形成されたMOSトランジスタのゲート絶縁膜上に固定された有機単分子層と、MOSトランジスタのソース及びドレインに接続された配線と、有機単分子層部分が露出する開口部を有するパッシベーション膜とを有し、ゲート絶縁膜の最表層がシリコン酸化膜で形成され、このゲート絶縁膜が30nm以上の厚さにて形成されている。

(もっと読む)

半導体装置

【課題】層間絶縁膜を厚くしなくてもソース配線の外にドレイン配線を引き出せ、かつ、LOCOS酸化膜や層間絶縁膜などの絶縁膜の絶縁破壊を防止できるようにする。

【解決手段】素子部8から配線引出し部9に延設されるようにn-型ドリフト層4の裏面に裏面電極19を備え、この裏面電極19とソース配線18との間に電流が流れるような構造、つまりn-型ドリフト層4の表裏を貫通して縦方向に電流を流す構造にする。そして、裏面電極19を配線引出し部9まで延設し、n+型コンタクト領域21、配線引出し部9のn-型ドリフト層4、nウェル領域20およびn+型コンタクト領域21を通じてドレイン配線23と接続する。すなわち、裏面電極19を通じて電流が流れるようにすることにより、ドレイン配線23を素子部8の外に引き出した構造とする。

(もっと読む)

高耐圧MOSトランジスタ装置

【課題】ドレイン配線の幅を従来よりも大きくして、ドレイン配線を導通可能な最大電流量を大きくすること。

【解決手段】高耐圧MOSトランジスタ装置10は、基板102に設けられたPウエル領域103中に形成されており、20V以上のソース−ドレイン間耐圧を有している。そして、Pウエル領域中のソース104a,104b及びドレイン108の間の領域部分が、外部電界の影響を受けて導電型が反転するのを防止する導電性膜を備えている。この導電性膜は、ゲート電極120a,120bと連続的に帯状層12として一体形成されており、基板の表面を平面的に見たとき、帯状層は、ソース及びドレインの一方又は双方を囲んで設けられている。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】極めて簡易に動作領域に負荷される応力を制御して、その移動度、さらには特性を制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の上方であって、その動作領域を被覆するようにして、前記動作領域に対して引張応力を作用させるための引張応力層を形成し、さらに、前記半導体基板の上方であって、前記引張応力層の上方または下方に前記動作領域を被覆するようにして、前記動作領域に対して圧縮応力を作用させるための圧縮応力層を形成する。次いで、前記圧縮応力層及び前記引張応力層の少なくとも一方に隣接するようにして金属層を形成するとともに、加熱処理を施して、前記金属層中の金属元素を前記圧縮応力層及び前記引張応力層の少なくとも一方内に拡散させて、前記層内に独立して内在する金属領域を形成する。

(もっと読む)

半導体装置

【課題】一方のゲート電極中の不純物が他方のゲート電極に拡散することを抑制するとともに、当該ゲート電極とコンタクトプラグとの接触抵抗を低減することが可能な技術を提供する。

【解決手段】ゲート電極30は、N型ゲート部分30NとP型ゲート部分30Pとを有している。ゲート電極30の側面31には、N型及びP型ゲート部分の境界領域BRに切り欠き部33が設けられている。N型ゲート部分30Nの側面31Nにおける切り欠き部33が形成されている領域31NNと、N型ゲート部分30Nの側面32Nとの間の最短距離は、N型ゲート部分30Nにおける第1活性領域の直上の部分の幅よりも小さく設定されている。コンタクトプラグ40は、N型及びP型ゲート部分の上面と、ゲート電極30の側面31の切り欠き部33が形成されている領域とに接触している。

(もっと読む)

半導体装置

【課題】電気特性の信頼性を向上させることができる半導体装置を提供する。

【解決手段】LCDドライバIC14(半導体装置)は、トランジスタ素子31と、トランジスタ素子31を電気的に分離するためのSTI分離層32と、STI分離層32及び拡散領域43上に跨って形成されたゲート配線34と、ゲート配線34とSTI分離層32との間に形成された絶縁膜41とを有する。絶縁膜41は、ゲート配線34に印加される高電圧に対して絶縁耐圧を確保するために用いられる。このような構成のLCDドライバIC14によれば、製造過程においてSTI分離層32に欠陥が生じた場合であっても、欠陥の影響を受けることなく、ゲート配線34に高電圧を印加することが可能となる。

(もっと読む)

半導体装置

【課題】複数の横型DMOS素子を備える構成において、ESD耐量を向上できる半導体装置を提供する。

【解決手段】LDMOS素子を複数備えた半導体装置であって、半導体基板における複数のLDMOS素子の形成領域として、半導体層とともに、半導体層のウェル形成面とは反対の面上に、半導体層よりも不純物濃度の高い第1導電型の高濃度層が形成され、半導体基板におけるゲート電極形成面の裏面であって、少なくとも高濃度層の半導体層との境界とは反対の表面全面にドレイン電極が直接形成され、ドレイン電極と複数のドレイン領域とが、それぞれ電気的に接続されている。

(もっと読む)

MOSトランジスタとその製造方法

【課題】素子サイズが増加せず、かつ困難な位置合わせを必要とせずに製造することができる基板接続部を有するMOSトランジスタを提供する。

【解決手段】例えばNMOSにおいて、ソース電極の一部に高濃度のp型不純物を注入した基板接続部12cは、ソース領域とドレイン領域に低濃度のn型不純物を拡散させたp型のシリコン基板1上に絶縁膜とポリシリコン膜を形成し、これらの絶縁膜とポリシリコン膜及びn型不純物拡散層を貫通してp型のシリコン基板に達するコンタクトホールを設け、このコンタクトホールに高濃度のp型不純物を注入して形成する。なお、ソース電極のn+拡散領域12bとドレイン電極のn+拡散領域13bは、同時に設けたコンタクトホールに高濃度のn型不純物を注入して形成する。その後、これらのコンタクトホールに配線層と同じ金属を充填してコンタクトを形成する。

(もっと読む)

1 - 20 / 34

[ Back to top ]