Fターム[5F140DB01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | シミュレーション (228) | 計算方法 (36)

Fターム[5F140DB01]の下位に属するFターム

Fターム[5F140DB01]に分類される特許

1 - 20 / 21

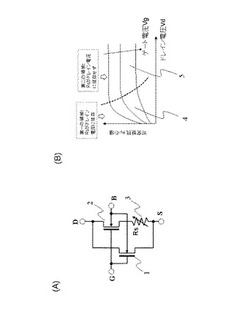

高耐圧MOSFETの回路シミュレーション用モデルの作成方法と装置並びにプログラム

【課題】高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーションの精度を向上させる。

【解決手段】ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、ソース領域のソース拡散層の幅とウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFET1、2と、第2のMOSFET2のソースに一端が接続された第1の可変抵抗素子3を備え、第2のMOSFET2のソースと第1の可変抵抗素子3の他端との接続点をソース端子Sとし、第1及び第2のMOSFETの共通接続したドレイン、共通接続したゲート、共通接続したバックゲートをそれぞれドレイン端子D、ゲート端子G、バックゲート端子Bとするモデルを作成し、モデリング対象の高耐圧MOSFETの電気特性データに基づき、第1の可変抵抗素子3の抵抗値を調整する。

(もっと読む)

半導体装置設計支援方法、半導体装置設計支援プログラム、及び半導体装置設計支援装置

【課題】バイアス条件によらず、モデルに対する解析精度を向上させる。

【解決手段】本発明による半導体回路の設計支援方法は、第1モデル22を用いて、プロセスパラメータが変動したときのデバイス特性の変動量102を算出するステップと、第2モデル23を用いて算出されたデバイス特性と実測値21との誤差に対して、変動量102で規格化するステップと、演算装置11が、規格化された誤差を用いて第2モデル23に対する解析を行うステップとを具備する。

(もっと読む)

デバイスシミュレーション装置、デバイスシミュレーション方法及びプログラム

【課題】キャリアの速度オーバーシュート効果を考慮した短チャネルトランジスタの電気特性を、高精度かつ数値的に安定に計算できるようにすること。

【解決手段】デバイスシミュレーション装置は、ドリフト拡散モデルとポアソン方程式に基づいてキャリアの電流密度及び静電ポテンシャルを算出するデバイス特性算出部と、キャリアのエネルギー保存式において熱伝導による拡散項を無視するとともに電流密度を一定としたものをチャネルに垂直な方向について積分した式に、電流密度及び静電ポテンシャルを代入して、局所的なキャリア温度を算出する温度算出部と、所定の移動度モデルにキャリア温度を代入して、局所的なキャリア移動度を算出する移動度算出部と、アインシュタインの関係式にキャリア移動度を代入して、局所的なキャリア拡散定数を算出する拡散定数算出部と、を有する。

(もっと読む)

状態密度が設計された電界効果トランジスタ

【課題】nチャネルおよびp型チャネルトランジスタに用いられる層構造を提供する。

【解決手段】nチャネルトランジスタを製作するのに用いる層構造を含む。層構造は、伝導帯底EC1を有する第1の半導体層、離散正孔準位H0を有する第2の半導体層、第1と第2の半導体層との間に配置された広バンドギャップ半導体バリア層、第1の半導体層の上方に配置されたゲート誘電体層、およびゲート誘電体層の上方に配置されたゲート金属層を含み、離散正孔準位H0は、伝導帯底EC1の下方に位置され、ゲート金属層にゼロバイアスが供給される。

(もっと読む)

ばらつきを考慮した半導体集積回路の設計方法

【課題】少数の離散的な電荷によって生じるトランジスタ特性のばらつきを考慮した半導体集積回路の設計方法を提供する。

【解決手段】単一の電荷が付加されることにより生じるトランジスタ特性の変位xの確率密度関数P1(x)を決定する工程と、P1(x)と、付加される電荷の個数nの出現確率と、を元に回路設計上想定すべき設計余裕Mを決定する工程と、を備える。単一の電荷が特性に影響を与えるほど微細なトランジスタを有する半導体集積回路においても、正確にばらつきが計算できる。

(もっと読む)

半導体装置の解析及び設計装置、及び半導体装置の解析及び設計方法

【課題】より精密な半導体装置の解析及び設計を可能とする。

【解決手段】半導体装置の解析及び設計装置は、トランジスタの構成情報と電気特性の測定値とを関連付けて格納する記憶部2と、第1トランジスタのチャネル領域を複数の領域に分割し、各領域の不純物濃度をパラメータとするパラメータ設定部11と、パラメータに基づいてチャネル領域の両端領域での不純物濃度を減少させた実効不純物濃度を算出し、実効不純物濃度を用いたポアソン方程式で計算された表面ポテンシャルから第1トランジスタの電気特性の第1計算値を求める素子特性計算部12と、記憶部2から読み出した測定値と第1計算値とが一致する場合、当該パラメータを第1トランジスタのパラメータとして、記憶部2に構成情報と関連付けて格納する判定部13とを具備する。パラメータ設定部11と素子特性計算部12とは、第1計算値と測定値とが一致するまで動作を実行する。

(もっと読む)

半導体装置の解析及び設計装置、及び半導体装置の解析及び設計方法

【課題】より精密な半導体装置の解析及び設計を可能とする。

【解決手段】半導体装置の解析及び設計装置は、トランジスタの構成情報とトランジスタの電気特性の測定値とを関連付けて格納している記憶部3と、第1トランジスタのチャネル領域の深さ方向の不純物濃度分布を示す関数を仮定する濃度分布設定部11と、関数を用いてポアソン方程式を表し空乏層幅を変数としてポアソン方程式を解き表面ポテンシャルを計算して第1トランジスタの電気特性の計算値を求める素子特性計算部12と、第1トランジスタの第1構成情報に基づいて、記憶部3を参照して、第1構成情報に対応する測定値を読み出し、測定値と計算値とが一致する場合、当該関数を第1トランジスタの不純物濃度分布と判定し、記憶部3に格納する判定部13とを具備する。濃度分布設定部11と素子特性計算部12とは計算値と測定値とが一致するまで動作を実行する。

(もっと読む)

高耐圧MOSトランジスタの回路シミュレーション方法

【課題】双方向MOSとしてのモデルを実現可能とし、高耐圧MOSのシミュレーション精度を向上する。

【解決手段】高耐圧MOSFETのシミュレーションを行うためのマクロモデルとして、NMOSFETのドレイン側とソース側に第1、第2のJFET(JN1、JN2)をそれぞれ付加し、第1のJFET(J1)のゲートに第1のダイオード(D1)の一端を接続し、第1のダイオード(D1)の他端を、前記NMOSFETのソースに接続し、第2のJFET(J2)のゲートに第2ダイオード(D2)の一端を接続し、第2のダイオード(D2)の他端を前記NMOSFETのドレインに接続してなるマクロモデルを用いてシミュレーションを行う。

(もっと読む)

シミュレーション方法及びシミュレーション装置

【課題】比較的簡単な計算で高精度にLDMOSFETデバイスの特性をシミュレートできるシミュレーション方法及びシミュレーション装置を提供する。

【解決手段】LDMOSFETにおける高耐圧化のためのドリフト領域を抵抗体と見なし、この抵抗を考慮したポテンシャル分布を反復計算で求めてデバイス全体のポテンシャル分布を計算する(STEP4、STEP5)。また、このドリフト領域部分に生じるキャパシタンスは、線形のポテンシャル分布を仮定して解析的に解く。更に、ゲート電極とドリフト領域とのオーバーラップ領域に生じるキャパシタンスは、ポテンシャルをディプリーション領域からアキュミュレーション領域まで考慮することによって計算する。

(もっと読む)

シミュレーション方法およびシミュレーション装置

【課題】ダイオード電流を高い精度で計算する。

【解決手段】回路シミュレーション実行部102には、シミュレーション対象であるダイオードのレイアウト情報が入力される。機械的応力パラメータ計算部103は、ダイオードのレイアウト情報から機械的応力に関するパラメータを計算する。ダイオード電流計算部104は、機械的応力パラメータ計算部103によって計算された機械的応力に関するパラメータを用いてダイオード電流を計算する。

(もっと読む)

回路シミュレーション方法及び回路シミュレーション装置

【課題】シミュレーション誤差が小さい回路シミュレーション装置を実現できるようにする。

【解決手段】回路シミュレーション装置は、トランジスタのデータを取得する手段52と、トランジスタのデータに基づいて、集積回路の接続情報を生成する手段53と、トランジスタのデータに基づいてモデルパラメータを定義する手段54と、接続情報を受け、モデルパラメータを組み込んだ回路シミュレーション実行プログラムを実行してトランジスタの電気的特性を算出する手段55とを備えている。モデルパラメータは、トランジスタの活性領域の幅に関する項と、トランジスタの活性領域とトランジスタの活性領域の周辺に設けられた活性領域との間の素子分離領域の幅に関する項と、周辺に設けられた活性領域の幅に関する項とを含む式により表される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】簡易な製造プロセスでCMOS半導体装置に付加する応力を制御し、電気的特性を向上する技術を提供する。

【解決手段】第1電界効果トランジスタおよび第2電界効果トランジスタを被覆するとともに第1電界効果トランジスタおよび第2電界効果トランジスタそれぞれの始点領域および終点領域を部分的に露出する開口が設けられた、第1電界効果型トランジスタおよび第2電界効果トランジスタそれぞれの少なくとも始点領域近傍から終点領域近傍に至る領域に応力を付勢するストレッサ膜4が形成され、第1ゲート電極3(3A)の第1絶縁層に略垂直な方向の高さが第2ゲート電極3(3B)の第2絶縁層に略垂直な方向の高さと異なる高さで形成された半導体装置である。

(もっと読む)

デバイスシミュレーションプログラム

【課題】比較的短い時間でポアソン方程式とシュレディンガ方程式を自己無撞着に解く手段を提供する。

【解決手段】与えられたポテンシャル分布および電子分布を基にポアソン方程式を解いてポテンシャル分布を求め、このポテンシャル分布が収束した場合に、収束したポテンシャル分布を基にシュレディンガ方程式を解いて電子分布を求め、この電子分布を基に演算したシュレディンガ方程式による電子密度と、収束したポテンシャル分布を基に演算したポアソン方程式による電子密度との差を基に電子密度の収束を判定し、電子密度が収束しなかった場合に、収束したポテンシャル分布およびシュレディンガ方程式から得られた電子分布をポアソン方程式にフィードバックしてチャネル領域の厚さ方向の電子分布を求める。

(もっと読む)

シミュレーション装置、シミュレーション方法、シミュレーションプログラム、及び記録媒体

【課題】 理論から一貫してデバイスのIV特性を予測でき、特にナノオーダーサイズの微小デバイスの特性予測に好適に用いることができるシミュレーション装置を提供する。

【解決手段】 本発明のシミュレーション装置は、前記デバイスの原子構造モデルを作成する原子構造作成部21と、前記原子構造モデルにおける電子構造計算を実行する電子構造計算部22と、前記電子構造に基づき量子効果及び原子構造を反映させて当該デバイスの電流−電圧特性を算出するIV特性計算部23と、前記計算により得られた電流−電圧特性に対して、電圧補正値による補正処理を実行する補正処理部24と、を有する。

(もっと読む)

最適化方法、最適化システム、及び、装置を製造する方法

【課題】 複数の特性値がトレードオフの関係を有していても構造因子の最適化が可能な最適化方法を提供する。

【解決手段】 複数の構造因子に複数の目標特性値が依存する一続きの系について構造因子から選択した複数の制御因子に複数の水準を設定し、水準を直交させて選択した複数の実験の組を設定し、トレードオフの関係にある目標特性値を基準特性値として選択し、基準特性値の系において満たすべき基準値を設定し、基準特性値を増減可能な構造因子を事前調整因子として選択し(S1)、基準特性値が実質的に基準値になるように実験の組毎に対応する系の事前調整因子の調整値を計算機を用いて決定し(S2)、調整値と実験の組毎に対応する系の目標特性値を複数の実験特性値として求め(S5)、実験の組と実験特性値に基づいて目標特性値の最適値と最適値を与える水準の組を最適の組として求める(S7)。

(もっと読む)

トランジスタモデル生成装置、および、トランジスタモデル生成方法

【課題】それぞれの拡散層に対応する拡散層長依存パラメータが反映されるトランジスタモデルを容易に作成するトランジスタモデル生成装置、トランジスタモデル生成方法を提供する。

【解決手段】トランジスタ抽出処理部は、マスクレイアウトデータから非矩形の拡散層領域に重なるゲート領域を有するトランジスタを抽出する。矩形分割処理部は、トランジスタのゲート長方向に分割線を設定して非矩形領域を複数の矩形領域に分割する。マスクレイアウトデータ関連付け処理部は、非矩形の拡散層領域と複数の矩形拡散層領域とをマスクレイアウトデータに関連付ける。サイズ計算処理部は、分割された複数の矩形領域の各々の大きさを示すサイズ情報を算出する。補正値計算処理部は、サイズ情報に基づいて、複数の矩形領域の各々の拡散層長依存パラメータを計算する。トランジスタモデル登録部は、拡散層長依存パラメータに基づいてトランジスタモデルを登録する。

(もっと読む)

BSIMモデルのパラメータ抽出方法

【課題】実測の電気特性に対し高精度なシミュレーションを実現可能で、且つ物理的に正当性の高いフィッティングパラメータを抽出可能にするBSIMモデルのパラメータ抽出方法を提供する。

【解決手段】BSIMモデルにおけるトランジスタの飽和電圧Vdsatの式はフィッティングパラメータVSATの関数であり、任意のVSAT値に対し1点の飽和点を所有する特徴がある。これを利用し、抽出対象であるVSAT値のみをスィープさせて飽和点の軌跡を描き、実測電気特性との一致点を与えるVSAT値を抽出する。

(もっと読む)

高周波トランジスタの設計方法、および、マルチフィンガーゲートを有する高周波トランジスタ

【課題】高周波半導体回路のトランジスタユニットの各電極引き出しノードまでの配線およびコンタクトを最適化する。

【解決手段】配線およびコンタクトの構成に応じて変化する等価回路パラメータのうち、ゲート配線、ソース配線およびドレイン配線の各配線間の結合容量、ならびに、各配線と半導体基板と間の結合容量について、高周波トランジスタの高周波特性に対する感度を測定する(ステップST21)。この感度に基づいて、ゲート配線、ソース配線およびドレイン配線の階層レベルを各々決定する(ステップST22)。そして、決定した各階層レベルにおけるゲート配線、ソース配線およびドレイン配線のパターンと、各配線間あるいは配線とトランジスタ部とを接続するコンタクトの配置と大きさとを設計する(ステップST23)。

(もっと読む)

デバイス計算方法

【課題】 短い時間で計算できるため実践性が高く、かつ、キャリア速度のオーバーシュートを高い精度で計算できるデバイスの計算方法を提供する。

【解決手段】1次元ポアソン方程式に併せて、5つの多重加速流定義をまとめた図8中のすべての式(流速の式と境界条件の式も含む)を用いることによって、半導体デバイス内部の電気的特性並びに電気的特性分布を推定する。

(もっと読む)

MOSトランジスタのシミュレーション方法

【課題】トランスコンダクタンスgm及びソースドレインコンダクタンスgdsの減衰を再現し、片側LDD構造を有する高耐圧MOSトランジスタのシミュレーション精度を向上する。

【解決手段】このMOSトランジスタモデルは、ドレイン側に、不変抵抗値を有する抵抗10がMOSトランジスタモデルMTに接続されたBISM3モデルに、さらにゲート電位VG及びドレイン電位VDに依存して抵抗値が変化する可変抵抗20を抵抗10に直列に接続したものである。即ち、可変抵抗20の抵抗値R20は、ゲート電位VG及びドレイン電位VDの関数であり、例えばそれらのパラメータの多項式(例えば、2次式や3次式)で表現される。そして、それらの多項式の各項の係数を実際のMOSトランジスタの電気的特性から抽出する。

(もっと読む)

1 - 20 / 21

[ Back to top ]