Fターム[5F152AA06]の内容

Fターム[5F152AA06]に分類される特許

141 - 160 / 636

レーザアニール装置

【課題】 フルメルト法による結晶化とパーシャルメルト法による結晶化を1回のレーザ照射によって簡単に実現することが可能なレーザアニール装置を提供する。

【解決手段】 光透過性を有する基板1上に形成された被結晶化薄膜(アモルファスシリコン薄膜3)に対してレーザ光(固体レーザの高調波)を照射して結晶化を行うレーザアニール装置である。被結晶化薄膜が形成された基板1を支持するステージ41を有し、ステージ41の表面は、基板1上に形成される回路のレイアウトに応じてレーザ光に対する反射率が変更されている。例えば、液晶表示パネルの作製において、ステージ41表面の反射率は、パネル領域21の画素部分31と周辺回路部分32とで異なる。

(もっと読む)

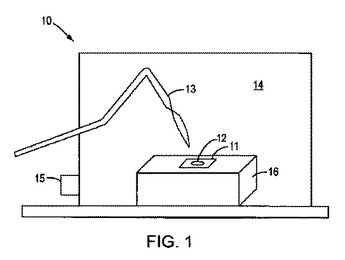

半導体処理装置および半導体処理方法

【課題】エネルギービームを用いた半導体膜の熱処理によって半導体素子を形成するにあたり、スループットを向上する。

【解決手段】本発明は、処理対象となる半導体膜11を備えた基板10を載置するステージ20と、ステージ20に載置された基板10の半導体膜11上に、複数のエネルギービームの照射点が一定間隔で並ぶようエネルギービームBを供給する供給部30と、供給部30によって供給される複数のエネルギービームBの照射点の並びと平行とならない方向に複数のエネルギービームBと基板10とを相対移動させ、複数のエネルギービームBの照射点を半導体膜11上で並列に走査し、半導体膜11の熱処理を制御する制御部40とを有する半導体処理装置である。

(もっと読む)

レーザアニール装置

【課題】 表面酸化膜除去から表面酸化膜形成までの前処理工程を速やかに行うことができ、均一な多結晶シリコン膜の作成が可能なレーザアニール装置を提供する。

【解決手段】 アモルファスシリコン薄膜に対して固体レーザアニール法により結晶化を行うレーザアニール装置である。アモルファスシリコン薄膜の表面酸化膜を除去する表面酸化膜除去装置1と、アモルファスシリコン薄膜の表面に所定の厚さの酸化膜を形成する表面酸化膜形成装置2とを前処理装置として有する。表面酸化膜除去装置1と表面酸化膜形成装置2は、連続処理可能な状態に配置されている。例えば、表面酸化膜除去装置1と表面酸化膜形成装置2は同一の搬送ロボット4の周囲に配置されている。あるいは、表面酸化膜除去装置1と表面酸化膜形成装置2が連結されている。

(もっと読む)

結像レンズ熱膨張補正方法、結像レンズ熱膨張補正装置、および結晶化装置

【課題】結像レンズがレーザー光を吸収して熱膨張することによる焦点位置の位置ずれを補正する。

【解決手段】基板の高さ変化量を換算して求めた結像レンズの位置ずれ量と、レーザー光の照射積算時間に基づいて求めた結像レンズの焦点の位置ずれ量とを加算して、結像レンズの熱膨張によるビーム集光位置の変動を補正するための補正移動量を算出し、この補正移動量を用いて結像レンズ移動部を駆動して結像レンズを移動することによって焦点位置の位置ずれを補正する。

(もっと読む)

半導体装置の作製方法

【課題】基板が設置されたステージをX方向やY方向に移動させるレーザー照射装置は、基板が大型化した場合、比例してフットプリント(処理に必要とされる平面での面積)が格段に大きくなり、装置全体の巨大化を招く問題が生じてしまう。

【解決手段】本発明のレーザ照射装置は、ガルバノミラーやポリゴンミラーによりレーザー光を半導体膜に照射して走査させ、さらにレーザー光照射の際は、常に半導体膜への入射角度θをある角度に一定に保つ。

(もっと読む)

半導体膜の形成方法および電気光学装置の製造方法

【課題】遮光層を有する構成でも、遮光層を有していない構成に対して液晶装置の製造工数や製造コストの上昇を抑えることができる半導体膜の形成方法および液晶装置の製造方法を提供すること。

【解決手段】半導体膜40の形成方法は、基板11上に、断面形状が台形状の遮光層21aを局所的に形成する遮光層形成工程と、遮光層21aを覆って、遮光層21aに重なる段差部22aを備えた絶縁層22を形成する絶縁層形成工程と、絶縁層22上に、段差部22aを覆う非晶質の半導体膜40を形成する半導体膜形成工程と、半導体膜40をアニールして結晶化させる結晶化工程と、を備え、遮光層形成工程では、遮光層21aにおける上底側の角部C1,C2が直角または鈍角をなして角張るように形成し、絶縁層形成工程では、絶縁層22の段差部22aにおける表面が角部C1,C2の形状に沿った形状となるように形成することを特徴とする。

(もっと読む)

薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置

【課題】薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置を提供する。

【解決手段】基板と、前記基板上に位置し、結晶化誘起金属を用いて結晶化された多結晶シリコン層からなり、ソース/ドレイン領域及びチャネル領域を含む半導体層と、前記半導体層上に位置するゲート絶縁膜と、前記ゲート絶縁膜上に位置するゲート電極と、前記ゲート電極上に位置する層間絶縁膜と、前記層間絶縁膜上に位置し、前記半導体層のソース/ドレイン領域と電気的に接続されるソース/ドレイン電極を含み、前記半導体層は前記半導体層の両端部に位置する第1ゲッタリングサイト及び前記第1ゲッタリングサイトと離隔されて位置する第2ゲッタリングサイトを含むことを特徴とする薄膜トランジスタ、その製造方法及びこれを含む有機発光ダイオード表示装置を提供する。

(もっと読む)

レーザ光源装置及びこれを用いたレーザ照射装置

【課題】安定で均一なビーム形状と強度をもち、干渉性が低く、小型で高効率なレーザ光源装置を提供する。

【解決手段】横マルチモードの光を出射する励起光源1と、共振器を構成し、少なくとも一部から異なる波長の光を外部に出力する共振器ミラー5,8,12と、励起光源1から出射される横マルチモードパターンの光で励起されるレーザ媒質6と、レーザ媒質6での発振により得られる横マルチモードの線状の基本波が照射されて、線状の変換波を出力する波長変換素子10と、を含む。

(もっと読む)

アクティブマトリクス基板、これを備えたパネル型表示装置、及びアクティブマトリクス基板の製造方法

【課題】アクティブマトリクス基板上における各トランジスタの利用目的に応じてその配置の方向を変更し、効率の良い回路設計を行う。

【解決手段】本発明のアクティブマトリクス基板は、ゲートドライバ21(第2の電気回路)およびソースドライバ22(第1の電気回路)が設けられた周辺領域を有している。ゲートドライバ21およびソースドライバ22に設けられている各トランジスタ25・26は、基板上にラテラル成長させて形成された結晶化半導体膜41を含んで構成されている。ソースドライバ22内に形成されているトランジスタ26では、半導体膜41内の結晶の成長方向D1に沿って、ソース電極45およびドレイン電極46が配置されている。一方、ゲートドライバ21内に形成されているトランジスタ25では、ソース電極45およびドレイン電極46の配置が成長方向D1に沿っているものと、沿っていないものとが混在している。

(もっと読む)

発振レーザ明示機能を有する結晶化装置及び結晶化装置における発振レーザ明示方法

【課題】定常運転時とメンテナンス時とにかかわらずレーザが発振しているか否かを常に明示して作業者が現場で直接的に安全確認をすることができる発振レーザ明示機能を有する結晶化装置及び結晶化装置における発振レーザ明示方法を提供する。

【解決手段】レーザ光路を取り囲む周囲部材の表面にレーザ光またはレーザ光からの散乱光を受けて発光する蛍光体を有する。

(もっと読む)

半導体装置の作製方法

【課題】高集積化を妨げずに、多結晶TFTのオン電流及び移動度を高めることができる半導体装置の作製方法と、それによって得られる半導体装置の提供を課題とする。

【解決手段】半導体膜に触媒元素を添加して加熱することで、結晶性が高められた第1の領域と、第1の領域と比較して結晶性が劣っている第2の領域とを形成し、第1の領域に第1のレーザー光を照射することで、第1の領域よりも結晶性が高められた第3の領域を形成し、第2の領域に第2のレーザー光を照射することで、第2の領域よりも結晶性が高められた第4の領域を形成し、第3の領域と第4の領域をパターニングして、第1の島状の半導体膜と、第2の島状の半導体膜をそれぞれ形成し、第1と第2のレーザー光は、互いにエネルギー密度が同じであり、第1のレーザー光の走査速度は第2のレーザー光の走査速度より速い半導体装置の作製方法。

(もっと読む)

薄膜トランジスタの製造方法

【課題】結晶粒界が大きく電気的特性の向上したTFTを、コスト上昇を抑制しつつ形成する。

【解決手段】平坦な表面を有する基板10の該表面上に、高熱伝導性を有する材料からなる熱伝導層37を形成する第1の工程と、熱伝導層37を、熱伝導層37の少なくとも一部が表面に対して傾斜する傾斜部38となるようにパターニングする第2の工程と、少なくとも傾斜部38を覆うように、基板10上に非晶質シリコン層32を形成する第3の工程と、非晶質シリコン層32をレーザーアニールにより結晶化して多結晶シリコン層34を形成する第4の工程と、多結晶シリコン層34上に、平面視で傾斜部38と少なくとも一部が重なるようにゲート電極42を形成する第5の工程と、を有することを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

レーザ結晶化装置、マスク、レーザ結晶化方法、結晶材、および半導体素子

【課題】粒内欠陥を抑制した高品質な結晶を得る。

【解決手段】投影マスク15は、第1スリットパターン15−1を介したレーザ光の照射によって、第1照射パターンを形成するためのブロックB1と、第2スリットパターン15−2を介した照射によって、第1照射パターンと平行であるとともに第1照射パターンの端部の一部を重畳する第2照射パターンを形成するためのブロックB2と、第3スリットパターン15−3を介した照射によって、第1照射パターンおよび第2照射パターンと直交する第3照射パターンを形成するためのブロックB3と、第4スリットパターン15−4を介した照射によって、第1照射パターンと平行である第4照射パターンを形成するためのブロックB4とを備え、第3レーザ光の照射により、第1照射パターンと第2照射パターンと第3照射パターンとの重畳領域に単結晶の種結晶領域を形成し、第4照射パターンが種結晶領域の一部と重畳する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】非晶質半導体薄膜の結晶化と選択的な高濃度不純物拡散をひとつの工程で行うことにより薄膜トランジスタの製造工程を簡単にし,製造コストを低減する。

【解決手段】絶縁基板上の非晶質半導体薄膜上に堆積した不純物を含む皮膜を所定の形状にパターン形成し、外方拡散防止膜で被覆したのち,連続発振レーザを照射することにより該非晶質の結晶化と同時に,該皮膜から不純物を該薄膜に選択的に高濃度に拡散させることにより半導体薄膜トランジスタを製造する。

(もっと読む)

薄膜トランジスタ

【課題】本発明は、結晶化触媒の均一な低濃度拡散制御で金属触媒から形成されるシードの位置を調整して多結晶シリコーン層内のチャネル領域を単結晶に近いように形成することによって薄膜トランジスタの素子特性を向上させて均一な値を得ることができる薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタは基板上に形成された金属触媒層、金属触媒層上に次々と形成された第1キャッピング層及び第2キャッピング層パターンを含む。製造方法は金属触媒層上に第1キャッピング層を形成する。第1キャッピング層上に第2キャッピング層を形成してパターニングする。パターニングされた第2キャッピング層上に非晶質シリコーン層を形成する。金属触媒を拡散させる。非晶質シリコーン層を結晶化して多結晶シリコーン層を形成する段階を含む。

(もっと読む)

多結晶層の製造方法

多結晶層の製造方法において、基材(1)上に一連の層を堆積し、前記一連の層は、非晶質初期層(4)、金属活性層(2)および初期層(4、10)と活性層(2、11)との間に堆積された中間層(3)を含む。中間層(3)をチタンをベースとして製造する。活性層(2)に位置する多結晶最終層を製造するために一連の層を熱処理する。 (もっと読む)

半導体装置

【課題】保護膜や層間絶縁膜を形成する際に、島状半導体層の段差によるカバレッジ不良を低減する半導体装置を提供することを課題とする。

【解決手段】リンを含む層は真性または実質的に真性な層上の一部に形成され、金属膜はリンを含む層上に形成され、半導体膜は、四方の周辺部の領域において真性または実質的に真性な層から形成された1μm以上300μm以下の突出部を有し、ゲイト電極と重なり、かつ金属膜と重ならない真性または実質的に真性な層と突出部は金属膜と重なる真性または実質的に真性な層より厚さが薄く、保護膜はゲイト電極と重なり、かつ金属膜と重ならない真性または実質的に真性な層と突出部とを覆っている半導体装置。

(もっと読む)

マスク、レーザ結晶化装置、レーザ結晶化方法、結晶材、および半導体素子

【課題】従来よりも大きな角型結晶を得る。

【解決手段】マスクには、レーザ光の照射によって略閉ループの結晶粒界に包囲された種結晶が形成するように種結晶形成用マスク要素群のスリットが配置され、種結晶中の特定位置を原点とするX−Y直交座標系について、kを1から4の自然数とし、第k象限におけるX軸正方向をkX+、X軸負方向をkX−、Y軸正方向をkY+、Y軸負方向をkY−とすると、種結晶形成用マスク要素群に続く種結晶伸張用マスク要素群を介して照射されるレーザ光の照射タイミングの制御と当該マスクの相対的な移動の制御とにより、略閉ループの結晶粒界に包囲された種結晶が、1X+、1Y+、2X−、2Y+、3X−、3Y−、4X+、および4Y−の各方向に伸張するように、種結晶伸張用マスク要素群のスリットが配置される。

(もっと読む)

半導体材料の処理方法及び処理された半導体材料

半導体材料を処理するための方法が開示される。開示される方法において、結晶構造を有する半導体材料が提供され、半導体材料の少なくとも一部分が熱源にさらされてメルトプールが形成され、次いで半導体材料が冷却される。この方法で処理された半導体材料も開示される。  (もっと読む)

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法及び有機電界発光表示装置

【課題】チャネル領域における結晶粒のサイズを大きくし、エッチング工程時に半導体層のチャネル領域を効率的に保護することができ、工程コストを節減することのできる薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタは、基板100と、基板上に位置するゲート電極120と、ゲート電極上に位置するゲート絶縁膜130と、ゲート絶縁膜上に位置し、チャネル領域、ソース領域及びドレイン領域を含む半導体層パターン165と、半導体層パターンのチャネル領域上に位置し、20ないし60nmの厚さを有するエッチング阻止層パターン150と、半導体層パターンのソース/ドレイン領域上に位置するソース/ドレイン電極181、182とを含むことを特徴とする。

(もっと読む)

141 - 160 / 636

[ Back to top ]