Fターム[5F152AA06]の内容

Fターム[5F152AA06]に分類される特許

81 - 100 / 636

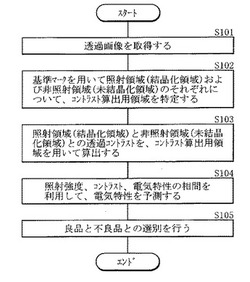

半導体薄膜の形成方法、半導体薄膜の検査装置および半導体薄膜

【課題】レーザアニールによる結晶化を利用した半導体薄膜の形成において、その結晶化度を従来よりも高精度に評価することが可能な半導体薄膜の形成方法を提供する。

【解決手段】p−Si膜23の結晶化度の検査処理の際に、p−Si膜23およびa−Si膜230へ向けて照射光Loutを照射し、p−Si膜23およびa−Si膜230の透過画像を取得する。画像処理用コンピュータ15において、p−Si膜23(結晶化領域51)の透過輝度とa−Si膜230(未結晶化領域50)の透過輝度との透過コントラストを求める。この際、予め形成された基準マーク6を用いて、結晶化領域51内および未結晶化領域50内におけるコントラスト算出用領域60,61を特定し、これらのコントラスト算出用領域60,61を用いて透過コントラストを求める。そして、求めた透過コントラストに基づいて、p−Si膜23に対する選別を行う。

(もっと読む)

発光装置の作製方法

【課題】 本発明は、曲面を有する基材に被剥離層を貼りつけた半導体装置およびその作製方法を提供することを課題とする。特に、曲面を有するディスプレイ、具体的には曲面を有する基材に貼りつけられた有機発光素子を有する発光装置の提供を課題とする。

【解決手段】 金属層または窒化物層からなる第1の材料層と酸化物層からなる第2の材料層との積層を利用して基板に設けられた有機発光素子を含む被剥離層をフィルムに転写し、フィルム及び被剥離層を湾曲させることによって曲面を有するディスプレイを実現する。

(もっと読む)

パターン化結晶質半導体薄膜

【課題】フォトレジストを用いずに製造可能で、所望の形状に直接描画できるパターン化結晶質半導体薄膜を提供する。

【解決手段】酸化インジウムを主成分とする非晶質薄膜を成膜し、前記非晶質薄膜の一部を結晶化することにより半導体化し、前記一部が結晶化した薄膜の非晶質部分をエッチングによって除去することにより得られるパターン化結晶質半導体薄膜。

(もっと読む)

半導体製造装置および半導体の製造方法

【課題】熱プラズマジェットを用いて粒径の異なる結晶シリコンを製造する半導体製造装置を提供する。

【解決手段】圧電素子2によって噴出口18と基板60との距離が1mmに設定されると、プラズマ源10は、熱プラズマジェットを発生し、直径が300μmφである噴出口18から熱プラズマジェットTPJをa−Si:H膜61に照射する。これによって、a−Si:H膜61の一部が溶融結晶化する。その後、圧電素子2によって噴出口18と基板60との距離が5mmに設定されると、プラズマ源10は、熱プラズマジェットを発生し、噴出口18から熱プラズマジェットTPJをa−Si:H膜61に照射する。これによって、a−Si:H膜61の一部が固相結晶化する。

(もっと読む)

半導体装置の製造方法および製造装置

【課題】製造工数を増やすことなく、大粒径の多結晶シリコン膜を有する半導体装置を製造可能な製造装置、および、製造方法を提供する。

【解決手段】製造装置100は、反応室1と、ヒータ2と、圧力計3と、複数のガス導入管4a〜4gと、MFC5a〜5gと、ニッケル導入部6と、バルブ7a,7bと、ICP−MS8と、ガス排出管9と、APC10と、ポンプ11a,11bと、を備えている。製造装置100にニッケル導入部6を設けるため、製造工数を抑えて製造装置100内で大粒径の多結晶シリコン膜34の形成を行うことができ、製造コストを抑えることができる。

(もっと読む)

半導体装置の製造方法、半導体検査装置および結晶化度検査方法

【課題】本発明は、アニール処理後の結晶化の状態について、非接触で精度よく、しかも効率的に、評価を行えるようにする。

【解決手段】アニール処理後の半導体層を有する多層構造体210を搭載するステージ201と、前記半導体層に対して光を照射する光源202と、前記光源202による光の照射によって得られるラマン散乱光を受光する受光部205と、前記受光部205が受光した前記ラマン散乱光を用いて前記半導体層の結晶化度を検査する検査部207とを備えた半導体検査装置200において、前記検査部207は、前記ラマン散乱光のラマンスペクトルによって特定される領域を波数についての所定閾値で領域分割する領域分割部と、前記領域分割をする前の領域全体と前記領域分割をした後の前記所定閾値を超える領域部分との面積比を算出し、その算出結果を前記半導体層の結晶化度とする結晶化度算出部とを備える。

(もっと読む)

半導体装置の製造方法

【課題】 広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】 ガラス基板上に薄膜トランジスタ及び配線を有する半導体装置を製造する方法において、ガラス基板上に下地絶縁層を形成する工程と、前記下地絶縁層上に下地バリア層を形成する工程と、前記下地バリア層上にシード層を形成する工程と、前記シード層を前記配線に対応する形状にパターニングしてシード層パターンを形成する工程と、前記シード層パターンの表面に銅配線層を無電解めっき法で形成する工程と、前記銅配線層マスクとして前記下地バリア層をパターニングする工程と、前記銅配線層を被覆するように絶縁層を形成する工程とを備えたことを特徴する半導体装置の製造方法。

(もっと読む)

表示装置およびその製造方法

【課題】製造工数の増大をもたらすことなく、薄膜トランジスタのゲート絶縁膜と容量素子の誘電体膜を異なる層における絶縁膜を用いることによって、それらの特性に応じた膜厚に設定できる表示装置の提供。

【解決手段】基板上に薄膜トランジスタと容量素子が形成されている表示装置にであって、前記薄膜トランジスタは、

ゲート電極の形成領域を被って形成された第1の絶縁膜と、

前記第1の絶縁膜上に形成され、平面的に観て、前記ゲート電極の形成領域内に開口を備える第2の絶縁膜と、

前記第2の絶縁膜上に前記開口を横切って形成され、両端に高濃度領域を備える島状の多結晶化された半導体層と、

前記半導体層の上面に前記半導体層の両端の高濃度領域のそれぞれの一部を露出させて形成された第3の絶縁膜と、

前記第3の絶縁膜から露出された前記半導体層の両端の高濃度領域のそれぞれに電気的接続がなされて形成された一対の電極と、を備えて構成され、

前記容量素子は、その誘電体膜が前記第3の絶縁膜と同層で同材料の絶縁膜によって構成されている。

(もっと読む)

光照射装置及びアニール装置

【課題】微小スポットに絞り込んだレーザ光を走査することによってアニールを行うにあたり、タクトタイムを短縮することを目的とする。またさらには、タクトタイムの短縮を安価で容易な装置構成で実現することを目的とする。

【解決手段】光源1と、光源から出射する光を走査する走査部8と、光源1から出射された光を走査部8へ導く第1の光学系7と、走査部8により走査された光を複数の光路に分割する光束分割素子19とを含む。そしてさらに、走査部8により走査された光を光束分割素子19に導く第2の光学系10と、複数に分割された光をそれぞれ被照射面45に集光する対物レンズ42と、複数に分割された光を対物レンズ42に導く第3の光学系40と、を含む光照射装置とする。

(もっと読む)

半導体製造方法、半導体製造装置、半導体装置および表示装置

【課題】均一性の極めて高いアニール処理結果を実現しつつ、その場合であっても生産性が損なわれてしまうことなく高スループット化を実現できるようにする。

【解決手段】基板上に少なくとも非晶質シリコン膜14と光吸収層16とが積層されてなる多層構造体に対して、前記光吸収層16の側から光を照射して当該光による局所加熱を行い、前記非晶質シリコン膜14を微結晶シリコン膜または多結晶シリコン膜に改質するアニール処理工程を備え、前記アニール処理工程では、前記局所加熱にあたり同一走査ライン上に複数の光ビームを配置するとともに、前記光吸収層16の熱伝導率をk、密度をρ、比熱をc、走査すべきライン長/走査速度をtpとした場合に、前記複数の光ビームを少なくとも間隔L=2×{k・tp/(ρ・c)}1/2だけ隔てて配置する。

(もっと読む)

薄膜トランジスターの製造方法

【課題】エキシマレーザーにより、α−Si層に加えられた熱は、絶縁層を介して金属遮光層へ伝わり、冷却されることで再結晶化される。この場合、金属層のパターン形状により、α−Si層の冷却速度は影響を受ける。そのため、多結晶シリコン層の特性は金属層のパターン形状の影響によりばらつくという課題がある。

【解決手段】形状および間隔を揃えた矩形の金属遮光層105の、長手方向に向けてエキシマレーザーを走査し、α−Si層を多結晶シリコン層115に改質する。長手方向に向けてエキシマレーザーを走査することから、金属遮光層105が連続した状態でレーザーアニールが進む。そのため、金属遮光層105上での多結晶シリコン層115は均質性が高くなる。そのため、金属遮光層105上に形成されるTFT101の電気的特性が均質化し、液晶装置100の表示均一性を高めることが可能となる。

(もっと読む)

半導体装置及び電子機器

【課題】 本発明では剥離技術を用いることにより様々な基板上に薄膜素子を形成し、従

来の技術では不可能であると考えられていた部分に薄膜素子を形成することにより、省ス

ペース化を図ると共に耐衝撃性やフレキシビリティに優れた半導体装置を提供する。

【解決手段】 本発明では、剥離技術を用いて一旦基板から剥離させた膜厚50μm以下

の素子形成層を基板上に固着することにより、様々な基板上に薄膜素子を形成することを

特徴とする。例えば、可撓性基板上に固着された薄膜素子をパネルの裏面に貼り付けたり

、直接パネルの裏面に固着したり、さらには、パネルに貼り付けられたFPC上に薄膜素

子を固着することにより、省スペース化を図ることができる。

(もっと読む)

シリコン薄膜の成膜方法および半導体装置の製造方法

【課題】塗布法を適用したより簡便な方法で導電性の高いコンタクト層とイントリンシックなシリコン層とを積層させた構成のシリコン薄膜を得る方法を提供する。

【解決手段】鎖状の高次シラン化合物Bと、金属Mを含有する化合物と、高次シラン化合物Bよりも沸点が低く金属Mと相互作用する化合物からなる溶媒Cとを混合した塗布液を調整する。塗布液を用いて基板1上に塗布膜3を形成する。塗布膜3中から溶媒Cを除去して乾燥させる。この際塗布膜3を加熱する。これにより、表面側において金属Mの含有量が多いシリコン薄膜5を形成する。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】薄膜トランジスタ基板の製造コストの低減を図る。

【解決手段】基板10に設けられたゲート電極11と、ゲート電極11を覆うように設けられたゲート絶縁膜12と、ゲート絶縁膜12上にゲート電極11に重なるように設けられた半導体層15aと、半導体層13a上にゲート電極11に重なると共に互いに離間するように設けられたソース電極16a及びドレイン電極16bとをそれぞれ備えた複数のTFT5aが設けられたTFT基板20aであって、半導体層15aは、ゲート絶縁膜12側に設けられたシリコン系の第1半導体層13と、ソース電極16a及びドレイン電極16b側に設けられた酸化物半導体系の第2半導体層14とを備えている。

(もっと読む)

半導体装置の作製方法

【課題】半導体膜から金属元素を取り除く従来のゲッタリング工程と異なる方法により半導体膜中から金属元素を除去する方法を提供することを課題とする。

【解決手段】金属元素を用いて結晶化された半導体膜に対して、パルスレーザを照射することにより、半導体膜にリッジが形成される。このリッジを除去することで、金属元素を除去する。リッジを除去したため半導体膜表面が荒れている場合、不活性雰囲気下で半導体膜にレーザを照射し半導体膜表面を平坦化する。

(もっと読む)

薄膜トランジスタおよび薄膜トランジスタの製造方法、並びにその利用

【課題】ドーピング処理の条件の厳密な管理および新たな製造工程を追加することなく、良好なVg−Id特性を有する薄膜トランジスタを実現する。

【解決手段】基板25上に形成された薄膜トランジスタにおいて、島状の半導体層21は、略平坦な上面を有する中央部21aと、基板25に対して0度より大きく、且つ90度以下の傾斜角を有する端部21bとを有し、島状の半導体層21の中央部21aに含まれる半導体は、端部21bに含まれる半導体よりも結晶粒径が大きい、或いは島状の半導体層21の中央部21aは多結晶半導体を含み、且つ端部21bは非晶質半導体を含む。

(もっと読む)

半導体基板およびその製造方法、並びに半導体装置

【課題】段差部において膜厚の急激な変動が抑制された半導体膜を含む半導体基板、およびその製造方法、並びに、その半導体基板を備える半導体装置を提供する。

【解決手段】本発明に係る半導体基板1は、下地基板10と、下地基板10上の一部に形成されている金属膜20と、金属膜20を覆うようにして下地基板10上に形成されている絶縁膜30と、絶縁膜30上に形成され、かつ結晶化された半導体膜40とを備えている。絶縁膜30は、金属膜20の端部において段差部を有し、当該段差部の下地基板10に対して垂直な断面形状が、外に膨らむ「R」形状を呈している。上記段差面は、その上端部から下端部に向かって、テーパー角度ψが略0°から徐々に大きくなって、略40°〜90°であるテーパー角度θになるように形成されている。

(もっと読む)

配線基板およびその製造方法

【課題】製造コストおよび製造時間の低減を図りつつ、高性能な薄膜トランジスタを備えた配線基板およびその製造方法を提供することを目的とする。

【解決手段】 絶縁基板101と、絶縁基板101上の表示画素部DSPに配置され、非晶質の第1半導体層SC1Aと、第1半導層SC1Aの上に積層された微結晶または多結晶の第2半導体層SC1Bとを有する第1薄膜トランジスタTFT1と、絶縁基板101上の駆動回路部DCTに配置され、第2半導体層SC1Bより電子移動度が高い多結晶の第3半導体層SC2を有する第2薄膜トランジスタTFT2と、を備えたことを特徴とする。

(もっと読む)

半導体素子基板の製造方法及び半導体素子基板並びに表示装置

【課題】同一基板上に、結晶粒の平均粒径が互いに異なり、各々優れたキャリア移動度を有する2種類の結晶質半導体膜を形成し、それら2種類の結晶質半導体膜を用いて異なる電気特性が要求される各半導体素子に所望の電気特性を得る。

【解決手段】基板11上に非晶質半導体膜24を成膜する非晶質膜成膜工程と、非晶質半導体膜24の一部を溶融固化して結晶化することで第1結晶質半導体膜24Aを形成する第1結晶化工程と、残部の非晶質半導体膜24を固相成長させることで第1結晶質半導体膜24Aよりも結晶粒の平均粒径が大きい第2結晶質半導体膜24Bを形成する第2結晶化工程と、第1結晶質半導体膜24Aの結晶粒の平均粒径が第2結晶質半導体膜24Bの結晶粒の平均粒径よりも小さい状態を維持しながら第1及び第2結晶質半導体膜24Bを溶融固化することで再結晶化する再結晶化工程とを含む。

(もっと読む)

多結晶シリコン薄膜の製造方法

多結晶シリコン薄膜の製造方法は、絶縁基板の上に金属層を形成する金属層形成段階と、前記金属層形成段階で形成された金属層の上にシリコン層を積層する第1シリコン層形成段階と、触媒金属原子が金属層から前記シリコン層に移動してシリサイド層を形成するように熱処理を行う第1熱処理段階と、前記シリサイド層の上に非晶質シリコン層を積層させる第2シリコン層形成段階と、前記シリサイド層の粒子を媒介として、非晶質シリコン層から結晶質シリコンが生成されるように熱処理を行う結晶化段階と、を含む。  (もっと読む)

(もっと読む)

81 - 100 / 636

[ Back to top ]