Fターム[5F152AA06]の内容

Fターム[5F152AA06]に分類される特許

201 - 220 / 636

結晶性半導体膜形成装置、結晶性半導体膜形成方法および結晶性半導体膜形成基板

【課題】ガラス基板上に形成されたアモルファスシリコン膜をレーザ等の光で加熱溶融した後に結晶化させて多結晶シリコン膜を得る際に、ガラス基板背面からレーザを照射するものとするとともに背面からの照射を効率的に行なう。

【解決手段】ガラス基板5は、アモルファスシリコン膜51を下にして配置される。上から加熱用レーザ2が対物用光学装置6を介してガラス基板5に上面側から照射されて、アモルファスシリコン膜51で結像する。また、結像するための焦点合わせのために高さセンサ1でアモルファスシリコン膜51の位置が測定される。測定用レーザは、ガラス基板5の上側から照射され、ガラス基板5の上面と下面で反射する。位置の測定には、共焦点測定方式が用いられ、ガラス基板5の下面で反射する光を用いてアモルファスシリコン膜51の位置が測定され、当該位置に基いて照射される光の焦点が合わされる。

(もっと読む)

レーザビーム照射方法およびレーザビーム照射装置

【課題】

DOEを用い、複数のレーザビーム源から出射したレーザビームを加算して、パワー密度を高めた照射光を形成する。

【解決手段】

レーザビーム照射方法は、第1のレーザビームを、第1の位置で第1の反射ミラーにより第1の方向に平行な方向に反射させ、発散光として進行させる工程と、 第2のレーザビームを、第1の位置の近傍の第2の位置で第2の反射ミラーにより第1の方向に平行な方向に反射させ、発散光として進行させる工程と、第3のレーザビームを、第1の反射ミラーと第2の反射ミラーの間を通って、第1の方向に平行に発散光として進行させる工程と、重なりを持って第1の方向に進行する、第1、第2、第3のレーザビームの合波光を受け、平行ビームにする工程と、平行ビームを回折光学素子に入射させ、回折を生じさせる工程と、を含む。

(もっと読む)

半導体素子の製造方法、アクティブマトリクス基板の製造方法、表示装置の製造方法、及び、レーザー結晶化装置

【課題】縦配置の半導体素子と横配置の半導体素子とのいずれにおいても結晶成長の方向とキャリアの流れる方向とが統一される半導体素子の製造方法を提供する。

【解決手段】長尺ビームの照射及び移動を交互に繰り返して非晶質半導体膜を溶融して結晶性半導体膜を形成する半導体素子の製造方法であって、上記製造方法は、長尺ビームの照射前に非晶質半導体膜をパターニングする工程と、パターニングされた非晶質半導体膜の外縁を含んで長尺ビームを照射する工程とを含み、上記長尺ビームは、移動方向に対して略45°をなす方向に傾けられている半導体素子の製造方法である。

(もっと読む)

表示装置及びその製造方法

【課題】大型基板上に多結晶シリコン(ポリシリコン)TFTを形成するために、基板上に形成した非晶質シリコン(アモルファスシリコン)膜をレーザ光で結晶化するプロセスにおいて、基板全面にわたり均一で大粒径の多結晶シリコンを容易に作成する。

【解決手段】基板上に形成した非晶質シリコン膜の平均膜厚を計測(ステップ201)し、この非晶質シリコン膜にレーザ光を照射(ステップ101)し、この照射で結晶化した多結晶シリコン膜の粒径分布を計測(ステップ102)し、多結晶シリコン膜の2つの点A,Bにおける粒径の測定値(ステップ103〜105)から、適正なレーザ光照射エネルギー密度値を算出(ステップ106〜108)し、次の非晶質シリコン膜の平均膜厚を計測(ステップ110,201)し、この平均膜厚と1つ前の非晶質シリコン膜の平均膜厚とから照射するエネルギー密度値を算出(ステップ203,204)し、このエネルギー密度値をレーザ光照射系にフィードバック(ステップ109)する。

(もっと読む)

半導体結晶薄膜の作製方法および装置

【課題】アモルファスシリコン薄膜を熱吸収層を用いて加熱結晶化するとともに、熱吸収層を汚染なく簡易方法によって除去でき、さらに結晶の欠陥を効率よく低減する。

【解決手段】基板2上に形成されたアモルファス半導体薄膜(a−シリコン膜1)を結晶化させる際に、前記アモルファス半導体薄膜の結晶化させたい箇所の表面にのみ予め熱吸収層3を設け、エネルギー照射することで前記アモルファス半導体薄膜を結晶化し、その後、ドライプロセスにより改質物質(水素など)を添加して、前記熱吸収層3を脆化させて半導体薄膜上から除去するとともに結晶化された前記半導体薄膜(p−シリコン膜1a)の欠陥低減を同時に行う。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】生産性が向上し、特性の良好な半導体装置の製造方法及び半導体製造装置を提供すること。

【解決手段】本発明にかかる半導体装置の製造方法は、絶縁性基板1上に非晶質半導体膜15を成膜する工程と、非晶質半導体膜15を脱水素処理する工程と、脱水素処理された非晶質半導体膜15に保護層5を形成する工程と、保護層5を介して非晶質半導体膜15を多結晶化する工程とを備える。また、非晶質半導体膜15の成膜から保護層5の形成まで、絶縁性基板1を真空中に保持する。

(もっと読む)

多結晶半導体膜の形成方法、薄膜トランジスタ、および薄膜トランジスタの製造方法

【課題】 隣り合う2つのTFTの間に短絡が発生するのを確実に防止するとともに、回路設計の自由度を増大させることができる多結晶半導体膜の形成方法。

【解決手段】 絶縁基板上において第1方向に沿って結晶成長した多結晶半導体膜を形成する本発明の方法では、第1方向に沿って第1の向きに結晶成長した結晶粒(15a)と第1の向きとは逆の第2の向きに結晶成長した結晶粒(15b)とが、第1方向と直交する第2方向に沿って鋸歯状または正弦波状に衝突するように、絶縁基板上における結晶成長を制御する。

(もっと読む)

結晶化方法

【課題】従来技術に従った方法の欠点を取り除く結晶化方法を提供すること。

【解決手段】材料を結晶化させるために、非晶質または多結晶材料の薄層(3)が、基板(1)の上部(2)の表面の少なくとも1つの領域上に堆積される。次いで、金属層(4)が薄層(3)の少なくとも1つの領域上に堆積される。次いで、熱処理(F2)が、薄層(3)の材料の結晶成長を可能にするように行われて、

・液体または過溶融液体状態が達成されるまでの、基板(1)の上部(2)の急速な温度上昇、および、

・基板(1)の上部(2)と薄層(3)の間の界面から薄層(3)と金属層(4)の間の界面への熱伝達、をもたらす。

(もっと読む)

半導体装置

【課題】高いgm(高いオン電流)を発揮し、比較的簡素な構成でSi−MOSFETに匹敵する特性を有する半導体装置を実現する。

【解決手段】非晶質透明基板と、前記非晶質透明基板上に形成された動作半導体薄膜と、前記非晶質透明基板上において、前記動作半導体薄膜の上下にそれぞれ絶縁膜を介して同一の金属材料から形成されてなる上部ゲート電極及び下部ゲート電極とを含み、動作半導体薄膜のチャネル領域が微結晶シリコン半導体からなり、ソース・ドレイン領域が多結晶シリコンからなる半導体装置。

(もっと読む)

多結晶半導体を製造する方法

【課題】多結晶Si層を含む多結晶SiのTFTまたは多結晶Siのデバイスを製造するのに使用される、多結晶Si層を形成する方法を提供する。

【解決手段】多結晶Si薄膜を形成する方法は、(A)基板10を準備すること、(B)基板の表面にアモルファスSi層11を形成すること、(C)少なくとも1枚の金属板12を取り付けて、それにより積層を形成すること、(D)積層に光を照射して、それによりアモルファスSi層から多結晶Si層15を形成すること、(E)金属板を取り除いて多結晶Si層を得ることを含む。急速熱アニール(RTA)プロセスが、加熱時間を短縮するためにステップ(D)の光照射プロセスに適用される。金属板による光の熱への変換がアモルファスシリコン層に対してさらに行われ、急速熱結晶化が実現される。こうして、多結晶Si層が得られる。

(もっと読む)

結晶シリコンアレイ、および薄膜トランジスタの製造方法

【課題】 1つの結晶粒内に複数の薄膜トランジスタを配置することのできるような大粒径の結晶を含む結晶シリコンアレイ。

【解決手段】 非晶質シリコン薄膜を結晶化して得られる結晶シリコンアレイの結晶化単位領域(U)は、7μm角以上の正方形領域を内包する大きさを有する二次元結晶部(21)と、主成長方向(F1)に間隔を隔てた一対の二次元結晶部の間に形成されて主成長方向に沿って0.2μm以上の長さを有する微結晶部(22)と、3.5μm以上の粒長を有する針状結晶部(23)とを含む。二次元結晶部は、1つの結晶核からの成長により形成され、結晶の主成長方向を有する。針状結晶部は、一対の二次元結晶部の間において主成長方向と直交する方向に沿った成長により形成されている。

(もっと読む)

薄膜トランジスタ及び液晶表示装置

【課題】薄膜トランジスタ及び液晶表示装置に関し、駆動回路部の大きさを増大させることなく各薄膜トランジスタの電荷移動度を均一にする。

【解決手段】薄膜トランジスタは、絶縁基板上に結晶粒が成長して形成された多結晶シリコン薄膜からなる半導体パターンが形成されており、この半導体パターンはチャンネル領域とチャンネル領域の両側に位置するソース領域及びドレーン領域とを含み、半導体パターンをゲート絶縁膜が覆い、ゲート絶縁膜上には少なくとも一部が結晶粒の成長方向と交差する方向を有するゲート電極がチャンネル領域に重畳する。

(もっと読む)

半導体装置の製造方法,表示装置の製造方法,半導体装置の製造装置および表示装置

【課題】レーザビームを往復させることによりスループットを高めると共に、往路と復路

との結晶性の差を確実に抑えることができる半導体装置の製造方法を提供する。

【解決手段】基板のレーザビームが照射された既照射領域61と未照射領域62との光学

特性の変化、例えば透過光または反射光の強度の変化を、コントラストすなわち((既照

射領域の光学特性)−(未照射領域の光学特性))/((既照射領域の光学特性)+(未

照射領域の光学特性)と定義する。コントラストを第1方向(往路)と第2方向(復路)

との各々について計測し、第1方向のコントラストと第2方向のコントラストとの差が所

定範囲内に収まるようにレーザビームの照射パワー、または、レーザビームと基板との相

対的な速度を変調する。改質された半導体膜において往路と復路との結晶性の差が確実に

抑えられ、TFT特性差が小さくなり、表示装置の表示むらが抑えられる。

(もっと読む)

半導体薄膜、薄膜トランジスタアレイ基板、及びそれらの製造方法、並びに、半導体薄膜の製造装置

【課題】信頼性向上、歩留まり向上が可能で、かつ品質向上につながる半導体薄膜の製造方法を提供すること。

【解決手段】本発明に係る半導体薄膜の製造方法は、基板上に非晶質の半導体薄膜を形成する工程(step1)と、自然酸化膜を除去する工程(Step2)と、紫外線照射によって生成するオゾン又は/及び酸素ラジカルにより表面酸化処理を行う工程(Step3)と、結晶粒界が略等間隔で、かつ格子状の周期構造を有する多結晶化された半導体薄膜を得るレーザーアニール工程(Step4)とを備え、レーザーアニール工程において、表面酸化処理を行う工程を経ずに、自然酸化膜を除去する工程後、直ちにレーザーアニールを行うことにより多結晶化された半導体薄膜を得る場合のレーザー光の最適エネルギー密度に対して、所定のエネルギー密度だけ低いエネルギー密度にてレーザー光照射を行う。

(もっと読む)

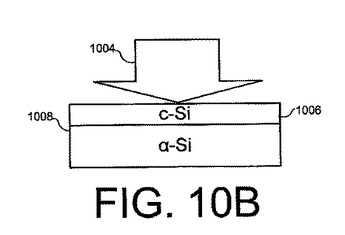

粒子ビーム補助による薄膜材料の改良

基板を処理する方法の様々な例が開示される。特定の実施形態において、この方法は、複数の粒子を含む連続粒子ビームを発生させること、およびこの連続粒子ビームを、非晶相である基板の領域に導入して、領域を非晶相から結晶相に変換することを含み、前記連続粒子ビームは、5×1014個/cm2・秒またはそれを超える電流密度を有するものとすることができる。  (もっと読む)

(もっと読む)

レーザアニール方法

【課題】シリコン結晶化膜を形成するレーザアニール方法において、0.2um程度の粒状結晶からなる多結晶の均一性の向上を可能とする。

【解決手段】シリコン結晶化膜を作製するレーザアニール方法において、非結晶領域(領域A)が平均粒径0.05〜0.2umの粒状結晶で構成される粒状結晶領域(領域P)に相変化され、かつ既に形成されている粒状結晶領域が相変化されないような照射条件で、レーザ光を照射する。

(もっと読む)

半導体装置、およびその作製方法

【課題】ばらつきを抑え、かつ、製造歩留まりの高い半導体装置を作製することを課題とする。

【解決手段】

絶縁表面を有する基板上に、チャネル形成領域が非単結晶半導体層で形成される薄膜トランジスタを有し、前記非単結晶半導体層は、厚さが5nm以上50nm以下であり、一方向に略平行に延びる結晶粒界を含み、該結晶粒界の間隔は10nm以上、500nm以下であることを特徴とする、半導体装置及びその作製方法を提供する。

(もっと読む)

半導体薄膜の製造方法、薄膜トランジスタの製造方法、半導体薄膜、薄膜トランジスタ及び表示装置

【課題】電気特性を高め、かつ電気特性のばらつきを抑制した半導体薄膜の製造方法、薄膜トランジスタの製造方法、半導体薄膜、薄膜トランジスタ及び表示装置を提供する。

【解決手段】基板上に半導体薄膜を製造する方法であって、上記製造方法は、基板上に形成された非晶質珪素膜に対して、該非晶質珪素膜の膜面内の一方位に結晶化エネルギーを付与していくことにより、{101}面が膜面と平行でありかつ〈100〉方位が結晶化エネルギーを付与していく方位と平行である第一結晶粒、及び、{114}面が膜面と平行でありかつ〈122〉方位が結晶化エネルギーを付与していく方位と平行な第二結晶粒で構成された多結晶珪素膜を形成する結晶化工程と、上記多結晶珪素膜に結晶成長エネルギーを付与することにより、第一結晶粒を消失させ、第二結晶粒を大きくする結晶成長工程とを含む半導体薄膜の製造方法である。

(もっと読む)

ポリシリコン膜の形成方法

【課題】微細な結晶粒を有する、リンまたはボロンがドープされたポリシリコンを形成すること。

【解決手段】反応管10内に複数のウエハWを搭載したウエハボート20を搬入し、ウエハWを減圧雰囲気下で加熱しながら、シリコン成膜用ガスと、リンまたはボロンを膜中にドープするためのガスと、ポリシリコン結晶の柱状化を妨げてポリシリコン結晶の微細化を促進する成分を含む粒径調整用ガスとを反応管10内に導入し、ウエハ上にリンまたはボロンがドープされたアモルファスシリコン膜を成膜し、その後、アモルファスシリコン膜を熱処理して、リンまたはボロンがドープされたポリシリコン膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】単結晶シリコン層でのキャリアの蓄積を防止することが可能な半導体装置を提供する。

【解決手段】単結晶シリコン基板11と、単結晶シリコン基板上に部分的に形成された絶縁層12と、単結晶シリコン基板上及び絶縁層上に形成され、過剰な4族元素に基づく欠陥層を含んだ単結晶シリコン層14と、単結晶シリコン層上に形成された第1のゲート絶縁膜16と、第1のゲート絶縁膜上に形成された電荷蓄積層17と、電荷蓄積層上に形成された第2のゲート絶縁膜19と、第2のゲート絶縁膜上に形成された制御ゲート電極22とを含むメモリセル用の複数の第1のゲート構造31とを備える。

(もっと読む)

201 - 220 / 636

[ Back to top ]