Fターム[5F152MM07]の内容

再結晶化技術 (53,633) | 半導体素子等への用途 (2,408) | 電子素子 (1,201) | トランジスタ (962) | バイポーラトランジスタ (105)

Fターム[5F152MM07]に分類される特許

1 - 20 / 105

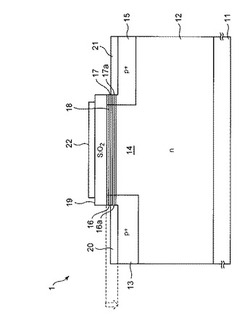

電界効果トランジスタの製造方法および電界効果トランジスタ

【課題】ドーピング密度を増やすことなく、高濃度キャリア走行部を形成でき、高い移動度と低いオン抵抗を実現できる電界効果トランジスタの製造方法および電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタ1は、窒素ドープn型SiCドリフト層12のキャリア走行部14を挟むように形成されたソース13とドレイン15とを備える。ソース13とドレイン15は、エッチングによってキャリア走行部14に隣接して形成された段部16,17を有する。キャリア走行部14は、段部16,17の段差面16A,17Aに紫外光を照射することによって段部16,17から延びるように形成された積層欠陥部18を有する。積層欠陥部18は、3C‐SiCの結晶構造を持ち、量子井戸構造のようにふるまうことからキャリアがここに多数閉じ込められる。

(もっと読む)

窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法

【課題】シリコン基板上に形成した、転位及びクラックの少ない窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法を提供する。

【解決手段】実施形態によれば、シリコン基板と、その上に順次設けられた、下側歪緩和層、中間層、上側歪緩和層及び機能層と、を有する窒化物半導体ウェーハが提供される。中間層は、第1下側層と、第1ドープ層と、第1上側層と、を含む。第1下側層は、下側歪緩和層の上に設けられ下側歪緩和層の格子定数よりも大きい格子定数を有する。第1ドープ層は、第1下側層の上に設けられ第1下側層の格子定数以上の格子定数を有し1×1018cm−3以上1×1021cm−3未満の濃度であり第1下側層よりも高い濃度で不純物を含有する。第1上側層は、第1ドープ層の上に設けられ第1ドープ層の格子定数以上で第1下側層の格子定数よりも大きい格子定数を有する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、ベース基板の上に、接着層、バッファ層および活性層をエピタキシャル成長法により順次形成する層形成工程を有し、接着層形成工程が、第1結晶層を形成する工程と第2結晶層を形成する工程と、を有し、第1結晶層の形成後であって第2結晶層の形成前の第1の段階、および、第2結晶層の形成後であってバッファ層の形成前の第2の段階、からなる群から選択された少なくとも1つの段階において、3族原料ガスの供給を停止するとともに成長室の内部を、アンモニアを含むガスの雰囲気に一定時間だけ維持する雰囲気維持工程を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板を洗浄装置の洗浄室に設置し、前記ベース基板の表面をHF水溶液により洗浄する第1洗浄工程と、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体基板および半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板であって、前記バッファ層が、第1結晶層と第2結晶層が交互に複数積層された積層構造体であり、前記第1結晶層が、AlmGa1−mN、(但し0≦m≦1)で表される結晶からなり、前記第2結晶層が、AlnGa1−nN、(但し0≦n≦1、m>n)で表される結晶からなり、前記第1結晶層の格子緩和度が、前記第2結晶層の格子緩和度より大きい半導体基板を提供する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後に、前記ベース基板の温度を1000℃以上に維持しつつ前記ベース基板の表面をアンモニアガスとキャリアガスとの混合ガスに暴露するアンモニアガス暴露工程と、前記アンモニアガス暴露工程の後に、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板、接着層、バッファ層および活性層を有し、前記ベース基板、前記接着層、前記バッファ層および前記活性層がこの順に位置し、前記ベース基板の前記接着層と接する領域にSiが存在し、前記接着層、前記バッファ層および前記活性層が、窒化物半導体からなる半導体基板の製造方法であって、前記ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、前記ベース基板の温度を1000℃以上1150℃以下に維持しつつ前記ベース基板の表面を水素ガスに暴露する水素ガス暴露工程と、前記水素ガス暴露工程の後、前記ベース基板の上に、前記接着層、前記バッファ層および前記活性層をエピタキシャル成長法により順次形成する層形成工程と、を有する半導体基板の製造方法を提供する。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】4°以下のオフ角を有するSiC基板2と、SiC基板2の主面4に形成され、その表面10に0.5nm以上の高さのステップバンチング9が形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、ステップバンチング9の線密度を40cm−1以下にする。

(もっと読む)

炭化珪素基板の製造方法および炭化珪素半導体装置の製造方法

【課題】炭化珪素基板の表面を保護することができる方法を提供する。

【解決手段】炭化珪素基板80が準備される。2μg/m3以上の二酸化窒素濃度を有する雰囲気に炭化珪素基板80をさらすことによって、炭化珪素基板80上に酸化膜70が形成される。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】チャネル移動度の低下を抑制しつつ閾値電圧を制御する炭化珪素半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の炭化珪素半導体装置の製造方法は、(b)二酸化珪素膜が形成された炭化珪素基板を窒化処理する工程と、(c)窒化処理された炭化珪素基板を水蒸気を含んだ酸素雰囲気で熱処理する工程とを備える。工程(c)は、(c1)窒化処理された炭化珪素基板を投入した熱処理炉の温度を不活性ガス雰囲気中で昇温又は降温する工程を含む。工程(c1)は、窒化処理直後のチャネル移動度をμch、昇温又は降温開始時刻をt=0、熱処理開始時刻をt=t1、熱処理終了時刻をt=t2、熱処理炉からの基板取出時刻をt=t3、ボルツマン定数をk、時刻tにおける熱処理炉の温度をT(K)とした場合に、式(1)により求められる炭化珪素基板中のチャネル移動度の低下率が10%以下となるように昇温速度及び/又は降温速度を決定する。

(もっと読む)

エピタキシャルウエハおよびその製造方法、半導体装置およびその製造方法

【課題】本発明は、結晶欠陥が少なく、キャリア時定数が十分大きい高品質なエピタキシャルウエハの製造方法と、当該エピタキシャルウエハを用いた半導体装置の製造方法の提供を目的とする。

【解決手段】本発明のエピタキシャルウエハの製造方法は、(a)3×1018cm-3以下の不純物濃度を有するSiC基板12上に、1×1014cm-3以上1016cm-3台以下の不純物濃度を有するエピタキシャル層13をエピタキシャル成長により形成する工程と、(b)前記工程(a)により得られた構造のSiC基板12の側から、エピタキシャル層13のうち所定の厚みを残して、SiC基板12の全部とエピタキシャル層13の一部とを連続的に除去する工程とを備える。

(もっと読む)

窒化ガリウム系半導体装置および半導体装置の製造方法

【課題】窒化ガリウム系半導体のドライエッチングに、塩素系ガスを用いたICP−RIEを用いると、誘電結合型プラズマは、温度が高いので、エッチングされた面に凹凸ができ、半導体にダメージを与え、塩素が残留する。

【解決手段】窒化ガリウム系半導体からなる第1の半導体層を形成する第1半導体層形成工程と、第1の半導体層の一部を、臭素系ガスを用いて、マイクロ波プラズマプロセスでドライエッチングして、リセス部を形成するリセス部形成工程と、を備え、窒化ガリウム系半導体装置を製造する半導体装置の製造方法を提供する。

(もっと読む)

SOIウェーハの製造方法

【課題】イオン注入剥法により作製されたテラス部にシリコン酸化膜のないSOIウェーハに、渓谷状の段差を発生させることなくエピタキシャル成長を行い、所望のSOI層厚を有するSOIウェーハを製造できる方法を提供することを目的とする

【解決手段】SOIウェーハのSOI層の外周端が、埋め込み酸化膜の外周端よりも外側に位置した構造となるように、該埋め込み酸化膜の外周部を除去する処理を行い、その後、SOIウェーハに水素を含む還元性雰囲気もしくは塩化水素ガスを含む雰囲気で熱処理を行った後、SOI層の表面にエピタキシャル層を形成するSOIウェーハの製造方法。

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、単結晶炭化珪素からなるSiC基板20を準備する工程と、坩堝70内においてSiC基板20の一方の主面20Bに面するようにベース基板10を配置する工程と、坩堝70内において、ベース基板10を、ベース基板10を構成する炭化珪素の昇華温度以上の温度域に加熱することによりSiC基板20の一方の主面20Bに接触するように炭化珪素からなるベース層10を形成する工程とを備えている。そして、ベース層10を形成する工程では、坩堝70内に、SiC基板20およびベース基板10とは別の、珪素を含む物質からなる珪素発生源91が配置される。

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、単結晶炭化珪素からなるSiC基板20を準備する工程と、坩堝80内においてSiC基板20の一方の主面20Bに面するようにベース基板10を配置する工程と、坩堝80内において、ベース基板10を、ベース基板10を構成する炭化珪素の昇華温度よりも高い温度域に加熱することにより、SiC基板20の一方の主面20Bに接触するように炭化珪素からなるベース層10を形成する工程とを備えている。そして、ベース層10を形成する工程では、坩堝80内に珪素を含有するガスが導入される。

(もっと読む)

炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、炭化珪素からなるベース基板10および単結晶炭化珪素からなるSiC基板20を準備する工程と、ベース基板10の主面10A上に接触するようにSiC基板20を載置して、積層基板を作製する工程と、積層基板を、SiC基板20よりもベース基板10の温度が高くなるように加熱することにより、ベース基板10とSiC基板20とを接合する工程と、SiC基板20が接合されたベース基板10の、SiC基板20とは反対側の主面10B上にエピタキシャル成長層30を形成する工程とを備えている。

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】中間層としてGe結晶を用いる場合の化合物半導体へのGe原子の混入を抑制する。

【解決手段】ベース基板と、ベース基板上に形成された第1結晶層と、第1結晶層を被覆する第2結晶層と、第2結晶層に接して形成された第3結晶層とを備え、第1結晶層が、ベース基板における第1結晶層と接する面と面方位が等しい第1結晶面、及び、第1結晶面と異なる面方位を有する第2結晶面を有し、第2結晶層が、第1結晶面と面方位が等しい第3結晶面、及び、第2結晶面と面方位が等しい第4結晶面を有し、第3結晶層が、第3結晶面及び第4結晶面のそれぞれの少なくとも一部に接しており、第1結晶面に接する領域における第2結晶層の厚みに対する第2結晶面に接する領域における第2結晶層の厚みの比が、第3結晶面に接する領域における第3結晶層の厚みに対する第4結晶面に接する領域における第3結晶層の厚みの比よりも大きい半導体基板を提供する。

(もっと読む)

III族窒化物半導体本体のインシチュドーパント注入及び成長

【課題】半導体材料の構造的及び化学量論的特性を保ったまま、窒化物本体を横方向及び縦方向で空間的に規定された選択ドーピングを達成しうるインシチュドーパント注入及び成長を提供する。

【解決手段】窒化物半導体本体の成長中にインシチュドーパント注入を可能にする方法は、ドーパント注入装置及び成長室を有する複合窒化物室中に、窒化物半導体本体に対する成長環境を確立するステップと、成長室内で窒化物半導体本体を成長させる成長ステップと、ドーパント注入装置を用いて成長室内で窒化物半導体本体にインシチュ状態でドーパント注入を行う注入ステップとを具える。この方法を用いて形成する半導体デバイスは、サポート基板上に形成した第1導電型の窒化物半導体本体と、窒化物半導体本体の成長中にこの窒化物半導体本体のインシチュドーパント注入により形成され、第2導電型を有する少なくとも1つのドープ領域とを具える。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

1 - 20 / 105

[ Back to top ]