Fターム[5F152NP29]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 単一層 (18)

Fターム[5F152NP29]に分類される特許

1 - 18 / 18

半導体装置

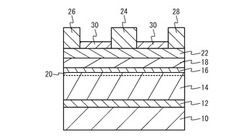

【課題】高周波数動作が可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に設けられたGaN電子走行層14と、GaN電子走行層14上に設けられたAlNスペーサ層16と、AlNスペーサ層16上に設けられたInAlN電子供給層18と、InAlN電子供給層18上に設けられたゲート電極24とゲート電極24を挟むソース電極26およびドレイン電極28と、を備え、AlNスペーサ層16の膜厚が、0.5nm以上1.25nm以下の半導体装置である。

(もっと読む)

半導体装置

【課題】シリコンなどの基板上に形成した高品質な結晶を有する半導体装置を提供する。

【解決手段】実施形態によれば、GaNを含む下地層と、窒化物半導体を含む機能部と、前記下地層と前記機能部との間に設けられ、AlNを含む層を含む中間層と、を備えた半導体装置が提供される。前記下地層のうちの前記中間層とは反対側の第1領域におけるシリコン原子の濃度は、前記下地層のうちの前記中間層の側の第2領域におけるシリコン原子の濃度よりも高く、前記下地層の前記中間層とは反対側の第1面は、複数の凹部を有する。

(もっと読む)

半導体基板及びその製造方法

【課題】単純な単結晶シリコン基板を出発基板として窒化ガリウム膜を形成することができ、反りやクラックが抑制された半導体基板及びその製造方法を提供する。

【解決手段】半導体基板10は、単結晶シリコン基板11と、単結晶シリコン基板11の表面に形成された炭素含有シリコン層12と、炭素含有シリコン層12の表面に形成されたバッファ層13と、バッファ層13の表面に形成された窒化ガリウム膜14とを備えている。炭素含有シリコン層12に含まれる炭素の濃度は1E+18atoms/cm3以上1E+21atoms/cm3以下であり、例えば単結晶シリコン基板11をプロパンガス雰囲気下で熱処理することにより形成される。

(もっと読む)

化合物半導体薄膜のp型への活性化方法

【課題】化合物半導体薄膜のp型への活性化方法を提供する。

【解決手段】バンドギャップより高エネルギーの電磁波を薄膜に照射しながら熱処理を施す。成長時にドーピングされるp型不純物の量は、薄膜の固有抵抗と適正熱処理温度を変え、また電極との接触抵抗を改善する。これにより、MOCVDやHVPEなどの気相エピタキシ法で成長した化合物半導体薄膜の吸収波長の電磁波を照射して化合物半導体薄膜の固有抵抗を低下させたり、付随的に化合物半導体と電極との特性接触抵抗率を低下させる。また、化合物半導体薄膜の成長時、化合物半導体薄膜に注入されたp型不純物の量が増加すると、活性化工程の適正熱処理温度が低くなる。そこで、紫外線の照射なしにp型不純物のドーピング温度を高め、低温での熱処理だけで化合物半導体薄膜の固有抵抗を低下させる。

(もっと読む)

有機薄膜の製造方法

【課題】基板上に大面積の単結晶の有機薄膜を形成することができる有機薄膜の製造方法を提供する。

【解決手段】基板上に第1の有機分子からなる規則的な分子配列を有する第1の有機分子層を形成する工程と、前記第1の有機分子層の上にエピタキシャル成長する第2の有機分子層を形成する工程と、前記第1の有機分子層を昇華、蒸発あるいは溶解して前記第2の有機分子層から除去する工程を有する有機薄膜の製造方法。前記第1の有機分子がアントラセン、前記第2の有機分子がペンタセンであることが好ましい。

(もっと読む)

半導体装置

【課題】素子特性のばらつきが抑制されたMOS型素子を含む半導体装置を提供すること。

【解決手段】基板の半導体領域に埋め込まれた素子分離絶縁膜と、前記素子分離絶縁膜によって素子分離され、上部が前記素子分離絶縁膜の表面よりも上に突出し、前記半導体領域の半導体層と、この半導体層にソース・ドレイン領域、ゲート絶縁膜およびゲート電極が形成され、かつ、前記ゲート電極がチャネル幅方向に平行な面の断面において前記素子分離絶縁膜上に形成されてなるMOS型素子とを具備してなり、前記ゲート電極下の前記半導体層の上面位置が、前記ゲート電極下の前記素子分離絶縁膜の上面位置よりも、20nm以上高いことを特徴とする。

(もっと読む)

半導体デバイス

【課題】低コスト及び簡素な構成で、窒化物化合物半導体層と基板との間の直列抵抗を低減できる半導体デバイスを提供すること。

【解決手段】半導体デバイスは、p型シリコン基板1と、p型シリコン基板1上に設けられ、シリコンに対してp型の不純物として機能する元素を含むバッファ層9と、バッファ層9上に設けられた窒化物化合物半導体層3と、窒化物化合物半導体層3上に設けられた第1の電極4と、p型シリコン基板1下面に設けられた第2の電極8とを有する。

(もっと読む)

AlN系III族窒化物単結晶厚膜の作製方法

【課題】結晶品質に優れ、かつクラックのないAlN系III族窒化物単結晶厚膜を作製する方法を提供する。

【解決手段】エピタキシャル基板上に、HVPE法によってAlN系III族窒化物厚膜を得る場合に、通常の成長条件で厚膜層の形成を行う第1の工程と、その時点で形成されている厚膜層を第1の工程における厚膜層の形成温度T1以上の高温状態T2で保持することを主目的とする第2の工程とを適宜のタイミングで切り替えつつ繰り返し行うようにする。これにより、それぞれの第1の工程において厚膜層に内在する歪を第2の工程で逐次に緩和させつつ厚膜層を形成することができる。厚膜層の形成後に面内方向に作用する引張応力を、あらかじめ緩和させた状態の厚膜層を形成することができるので、厚膜層におけるクラックの発生を抑制することができる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】電界効果トランジスタを構成するp型半導体層内のドーパント不純物量やp型層とゲート絶縁膜間の界面準位密度を制御することにより、チャネルとなるp型半導体層の低抵抗を確保しつつ、コラプス現象を抑制し、更に高温での動作を安定化し、良好な信頼性を確保する。

【解決手段】基板2と、前記基板2の上に形成され、p型のドーパントとともにn型のドーパントがドーピングされた前記基板と格子定数が異なるp型の窒化物系化合物半導体層3と、前記p型の窒化物系化合物半導体層3上に形成された絶縁膜4と、前記p型の窒化物系化合物半導体層3をチャネル層とするために前記p型の窒化物系化合物半導体層3と電気的に接続されたソース電極S及びドレイン電極Dと、前記絶縁膜4上に形成されたゲート電極Gと、を有する電界効果トランジスタ1。

(もっと読む)

窒化物基板の製造方法と窒化物基板及び窒化物系半導体デバイス

【課題】 低欠陥単結晶領域Zの幅zが2000μm〜10000μmの広い窒化物半導体基板を製造すること。

【解決手段】

下地基板Uの上に、幅が20μm〜400μmの被覆部Sを一定ピッチ2020μm〜10300μmで平行等間隔に持つマスクを形成し、反応炉にマスク付き下地基板Uを装入、加熱し、分圧が(1.5+0.0005p)kPa〜(4+0.0005p)kPaであるようなHClと、分圧が(15−0.0009p)〜(26−0.0017p)kPaであるようNH3を供給して反応させマスク付き下地基板Uの上にAlxGayIn1−x−yN結晶(0≦x<1、0<y≦1)を成長させ、被覆部Sに底を、露呈部Eの中間部に頂上を持つ平行のファセット面Fからなる複数の山谷構造を形成し、被覆部Sの直上部分は結晶欠陥集合領域Hに、露呈部Eの上ファセット面F直下は低欠陥単結晶領域Zとなるようにする。

(もっと読む)

III族窒化物結晶の形成方法、積層体、およびエピタキシャル基板

【課題】従来よりも結晶品質の優れたIII族窒化物結晶およびその形成方法を提供する。

【解決手段】所定の基材に第1のIII族窒化物結晶を成長下地層2としてエピタキシャル形成してなる下地基板に対して、1250℃以上の所定の温度で熱処理を行う。これにより、成長下地層2の表面には、島状結晶2Iによる三次元的な微細な凹凸形状が形成される。係る下地基板の上に、結晶層4として、第2のIII族窒化物をエピタキシャル形成する。結晶層4と下地基板3との界面には多数の微細な空隙5を介在することになるが、該空隙5の存在により、下地基板3からの転位の伝搬が抑制されるので、結晶層4の転位密度は低下する。結果的に、良好な結晶品質の結晶層4を得ることが出来る。

(もっと読む)

GaN/GaNの直接接合方法

【課題】たとえ凹凸を有するGaN接合表面同士の直接接合でも可能とする比較的簡便なGaN/GaNの直接接合方法を提供することである。

【解決手段】二つの基板1、5上にそれぞれ成膜したGaN2、6同士を直接接合するGaN/GaN直接接合方法において、予め少なくとも一方の基板1上のGaN2の接合面にアンモニア水8を塗布し、この後GaN接合面同士を重ね合わせ、両基板1、5間に圧縮荷重を印加する。この圧縮荷重印加により接合面に圧縮応力を作用させ、圧縮応力を作用させた状態で不活性ガス雰囲気中で熱処理することで、GaN2、6同士を直接接合する。

(もっと読む)

SOI基板及び該基板の製造方法

【課題】SOI層の厚さのバラツキの無いSOI基板及び該SOI基板の製造方法を提供する。

【解決手段】シリコン基板上にエピタキシャル剥離層を介してALE成長でSOI層を形成し、ボデイウエーハを貼り付けた後、前記エピタキシャル剥離層を溶解除去することによって、全てがALE成長で作成したSOI層を形成し、

SOI層の厚さのバラツキの無いSOI基板とした。

(もっと読む)

窒化物半導体素子の製法

【課題】 高温のアニール処理を長時間に亘って行うことにより発生する窒素空孔の形成という問題を生じさせることなく、アクセプタの活性化を行い、キャリア濃度の高い(低抵抗の)p形の窒化物半導体層を有する窒化物半導体素子の製法を提供する。

【解決手段】 基板1上に窒化物半導体からなる半導体積層部6を形成し、その半導体積層部6の表面側から、λ=h・c/E以下(EはMgとHとの結合を切り離し得るエネルギー)の波長λのレーザ光を照射する。その後に、300〜400℃の熱処理を行う。そして、通常の窒化物半導体LEDの製造工程と同様に透光性導電層7を設け、半導体積層部6の一部をエッチングにより除去して露出するn形層3にn側電極9を、透光性導電層7の表面にp側電極8を形成する。

(もっと読む)

SiC半導体およびその製造方法

【課題】 表面の凹凸および反りが低減され、結晶性に優れた高品質な面方位(111)の3C−SiC単結晶薄膜を備えた半導体、および、Si単結晶基板上に、格子不整合を緩和し、かつ、エッチングを防止して、確実かつ容易に、面方位(111)の3C−SiC単結晶薄膜を形成することができるSiC半導体の製造方法を提供する。

【解決手段】 面方位(110)のSi単結晶基板1上に、有機化合物ガスを用いて、300Torr以下の減圧雰囲気下、780〜950℃で、水素が1019atoms/cm3以上含まれる3C−SiC低温成長層2を気相成長させた後、その上に面方位(111)の3C−SiC単結晶層3を形成することにより、SiC半導体を得る。

(もっと読む)

ゲルマニウム・オン・インシュレータ(GeOI)型ウェーハの製造方法

【課題】薄いゲルマニウム層の電気的品質を改良したゲルマニウム・オン・インシュレータ型ウェーハの製造方法を得る。

【解決手段】ゲルマニウム基板1またはエピタキシャル・ゲルマニウム層を備える基板を設け、ゲルマニウム基板1の一つの主表面3上または主表面3内に誘電体層7を設け、ソース基板をハンドル基板5に取り付けることによりソース・ハンドル複合物を形成し、ソース基板内に前もって設けられ、実質的に主表面に平行な所定分離領域において、基板をソース・ハンドル複合物から取り外すことによりゲルマニウム・オン・インシュレータ・ウェーハを作製する工程を備える。誘電体膜の品質を向上し、同時によりコスト削減効果が高い製造工程を達成するために、ゲルマニウム基板1とハンドル基板5の間に誘電体層7として酸窒化ゲルマニウム層を設ける。

(もっと読む)

半導体装置及び半導体基板

【課題】 Siがドナーとして作用することによるキャリアの蓄積及び表面モフォロジーの悪化による特性劣化のない、半導体装置及び半導体基板を提供する。

【解決手段】 化合物半導体基板1に形成した一つ以上の化合物単結晶膜7を有する半導体装置であって、化合物半導体層基板1表面、この基板1表面と化合物単結晶膜7との界面、化合物単結晶膜7表面の何れかに、Si酸化膜を有し、Si酸化膜が形成される上記表面又は界面のヘイズが10ppm以下である。Si酸化膜は、基板1又は下地膜7の表面に存在するSi及びSi化合物5を、オゾン水で表面処理した後に、第二の又はさらに多数のGaAsエピタキシャル層3及び4を成長させて形成することができる。

(もっと読む)

基体の上に歪み層を製造する方法、及び層構造

【課題】

基体上に歪んだ層を作製する新規の方法及び作製された層構造物の提供。

【解決手段】

この課題は、歪み層(2)を作製する方法において、

− 層(2)を基体(1)の上に配置しそして歪ませ、

− 歪んだ層(2)を構造化し、

− その層(2)を緩和し、

− 歪めるべき層(2)において方向転位を生じさせる

各段階を含むことを特徴とする、上記方法によって解決される。このようにして作製した層構造は三軸的に歪んだ層を有する。  (もっと読む)

(もっと読む)

1 - 18 / 18

[ Back to top ]