Fターム[5H420NA18]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 基準生成部 (1,182) | 基準生成形式 (1,136) | 分圧回路 (690) | コンデンサ (15)

Fターム[5H420NA18]に分類される特許

1 - 15 / 15

集積回路装置及び電子機器

【課題】電圧発生回路の電源電圧が低下した場合でも、その構成を変更することなく、該電圧発生回路が発生した電圧の変動を抑制できる集積回路装置等を提供する。

【解決手段】集積回路装置100は、第1の電圧V1と第2の電圧V2との差を動作電圧として第3の電圧V3を発生し、第3の電圧V3を出力電圧供給線に供給する電圧発生回路120と、動作電圧が低下したとき、所与の期間、出力電圧供給線PLOへの電流の流し込み又は該出力電圧供給線からの電流の引き込みを行う電圧変動抑制回路130とを含む。

(もっと読む)

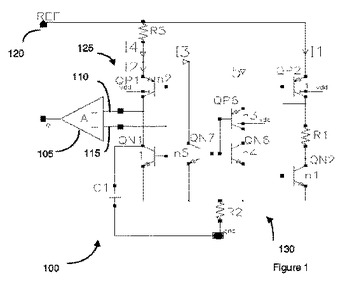

低ドロップアウト線形レギュレータ(LDO)、LDOを提供するための方法、およびLDOを動作させるための方法

【課題】PSRRが改良された低ドロップアウト線形レギュレータを提供する。

【解決手段】LDOは、差動増幅器と調整されたカレントミラーとを結合し、それぞれ差分信号を受信するように構成された2つのノードを有する。調整されたカレントミラーは、差分信号をシングルエンド信号に変換および増幅するように構成される。LDOは、周波数補償用に構成された第1のコンデンサを有し、第1のコンデンサは、第1の段と第2の段との間に結合される。LDOは、第1のカスコード回路の容量性負荷を平衡化するための第2のコンデンサを有し、第2のコンデンサは、第1の段と電源電圧との間に結合される。第1のカスコード回路は、電源電圧の変動によって生じるコンデンサの入出力間の差電圧を抑制するように構成される。LDOは、差動増幅器の電源の変動を抑制するように構成された第2のカスコード回路を有する。

(もっと読む)

定電流発生回路および該定電流発生回路を用いた半導体装置ならびに電子機器

【課題】抵抗のばらつきの影響を受けないで一定の電流を発生することが可能な定電流発生回路およびそれを用いた半導体装置や電子機器を提供すること。

【解決手段】一方の入力端子が第1の基準電圧源VBIに接続された差動増幅回路Ampと、ゲートが差動増幅回路Ampの出力に接続され、ソースが第1の電源電圧に接続され、ドレインがローパスフィルタ(抵抗RF,キャパシタCF)を介して差動増幅回路Ampの他方の入力端子に接続された第1のトランジスタP1と、第1のトランジスタP1のドレインに接続され、クロック信号により充電と放電が交互にかつ相補的に繰り返される第1のキャパシタC1および第2のキャパシタC2と、ソースが第1の電源電圧に接続され、ゲートが差動増幅回路Ampの出力に接続され、ソースから定電流が取り出される第2のトランジスタP2を有する。

(もっと読む)

バイアス電流発生回路

【課題】正電源電圧VDDが急激に低下したときでも、バイアス電流Ioutが遮断されないようにしたバイアス電流発生回路を提供する。

【解決手段】トランジスタMP1,MP2からなる第1のカレントミラー回路、トランジスタMN1,MN2からなる第2のカレントミラー回路、バイアス電流Ioutを決める抵抗R1、スタートアップ用のキャパシタC1を有するバイアス電流発生回路本体1Aと、ノードN3と負電源電圧VSSの端子に接続されたキャパシタC2と、ノードN3と正電源電圧VDDの端子との間に接続されたダイオード接続のトランジスタMP3とから構成した。

(もっと読む)

定電圧発生回路およびレギュレータ回路

【課題】オフセット電圧に影響されずに一定電圧を発生する定電圧発生回路を小さな占有面積で実現する。

【解決手段】第1電位と第2電位とを出力する基準電位発生部Q1,Q2,R1-R3と、第1および第2電位を2個の入力とし、第1動作期間に出力が出力線に接続される第1アンプ部と、第1および第2電位を2個の入力とし、第2動作期間に出力が出力線に接続される第2アンプ部と、ローパスフィルタ11と、を備え、第1と第2動作期間を交互に行い、第1アンプ部は、第2動作期間においてオフセット電圧を記憶し、第1動作期間において記憶したオフセット電圧分を相殺して第1電位と第2電位を等しくする出力を行い、第2アンプ部は、第1動作期間においてオフセット電圧を記憶し、第2動作期間において記憶したオフセット電圧分を相殺して第1電位と第2電位を等しくする出力を行う。

(もっと読む)

基準電圧発生回路

【課題】雑音を低減するローパスフィルタの容量を高速で充電して、高速に出力電圧を整定することが可能な基準電圧発生回路を提供する。

【解決手段】基準となる直流電圧を発生する基準電圧源1と、基準電圧源の出力に接続されたローパスフィルタ2と、基準電圧源の出力が入力端子に接続されローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路10と、基準電圧源の出力が一方の入力端子に接続されローパスフィルタの出力が他方の入力端子に接続されたヒステリシスコンパレータ11とを備える。起動時に基準電圧源の出力とローパスフィルタの出力の電圧差が所定値を超えている期間は、ヒステリシスコンパレータの出力信号により第1電圧バッファ回路の出力インピーダンスが制御される。起動時にローパスフィルタを低インピーダンスで急速に充電することにより、整定の時間を早めることができる。

(もっと読む)

スイッチング電源装置

【目的】過負荷状態が発生して出力電圧Voutが低下しても素早くリカバーし、しかもその後の出力電圧のオーバーシュートを対策することのできるスイッチング電源装置を提供する。

【構成】時刻t0で過負荷が発生すると、出力電圧Voおよびフィードバック信号VFBが減少する。ソフトスタート信号VSOFTもクランプ回路の働きによりVFBに追従して減少する。基準電圧Vref≧ソフトスタート信号VSOFTとなるt1〜t2の期間は、ソフトスタート信号VSOFTとフィードバック信号VFBが比較されて誤差信号Error Signalが生成される。従い、誤差信号を生成するための、フィードバック信号VFBとその比較相手との差分は△V以上に大きくならないから、誤差信号およびスイッチング素子のオンデューティが過大になることを防ぐことができ、これにより出力電圧回復時のオーバーシュートを抑制することができる。

(もっと読む)

階段電圧生成回路

【課題】導体の接続形態に係る回路構成の自由度を高めた階段電圧生成回路を提供する。

【解決手段】N−1個の導体系D1〜D4と、直流電源電位の導体D5と、回路グランド電位の導体D0とを有し、N−1個の導体系からN−1個の端子を取り出し、当該N−1個の端子の各々と出力端子との間と、直流電源電位の導体D5と出力端子との間と、回路グランド電位の導体D0と出力端子との間とをスイッチ素子T0〜T5でそれぞれ接続すると共に、負荷容量CLを出力端子に接続し、回路グランド電位の導体に接続されたスイッチ素子をオンT0にし、次に、N−1個の端子に接続されたN−1個のスイッチ素子T1〜T4をあらかじめ定めた任意の順番で順次オンにし、直流電源に接続されたスイッチ素子T5をオンに制御した後に、逆の順番で各スイッチ素子を順次オンに制御することを繰り返えす階段電圧生成回路。

(もっと読む)

閉路判定装置および配電系統システム

【課題】 同一相の位相差を迅速かつ正確に求め、開閉器の開閉可否を早期に判断することで、配電系統に影響を与える横流を防止しつつ、円滑にループ切替を実施させることを目的としている。

【解決手段】 本発明にかかる代表的な構成は、異なる配電系統それぞれに接続され異なる配電系統間を開閉する開閉器110に併設される閉路判定装置120であって、開閉器における異なる配電系統それぞれの3相線路総ての電圧を連続的に測定する電圧測定部122と、測定された各電圧波形の、ゼロクロス点と基準時刻との相対時間を計数し、相対位相角を導出する相対位相角導出部124と、異なる配電系統間で対応する相同士の相対位相角の差分である位相差を計算する位相差計算部126と、計算された位相差が横流を許容できる所定範囲内であれば、開閉器の閉路を許可する閉路許可部128と、を備えることを特徴とする。

(もっと読む)

定電圧回路、定電圧供給システム、および定電圧供給方法

【課題】 入力電圧から出力電圧への電圧変換経路にローパスフィルタを備える構成により、入力電圧の過渡的な変動が抑制され安定した定電圧を出力することが可能な定電圧回路、定電圧供給システム、および定電圧供給方法を提供すること

【解決手段】 PMOSトランジスタM1のゲート端子に入力される入力電圧信号VINは、定電流源ISによりPMOSトランジスタM1のソース端子を介して流されるバイアス電流I1に応じて、ソース端子においてPMOSトランジスタM1のゲート・ソース間電圧でレベルシフトされた電圧値に変換される。変換された電圧は、容量素子C1を経てソースフォロア回路から出力される。入力電圧信号VINからソースフォロア回路に至る信号経路には、PMOSトランジスタM1のインピーダンスと容量素子C1とによりローパスフィルタが構成される。

(もっと読む)

低ノイズ基準電圧回路

低ノイズ基準電圧回路が記述される。基準回路はバンドギャップ基準要素を使用し、出力に対する高ノイズ及び低ノイズの影響を減らすための、電流シャントとフィルタのうちの少なくとも1つを含む。更なる変更のために曲率矯正要素を含めても良い。  (もっと読む)

(もっと読む)

自己バイアス容量フィードバック段を使用するアナログ電圧の生成

電流ドレインが低減されたアナログ電圧ドレインが、新しい容量分割フィードバックアーキテクチャによって達成される。操作相の間、オペアンプが、出力電圧の容量分割された一部分をモニターし、従って電流シンクまたはソースを駆動し、初期相の間、出力が異なる回路によって正確な値にされる一方で、オペアンプは、直流オフセット効果を取り除くように自己調整自体に接続されている。  (もっと読む)

(もっと読む)

き電線電圧補償装置

【課題】車両突入電流の直流成分により直列コンデンサに発生する直流電圧成分の影響を受けることのないき電線電圧補償装置を提供する。

【解決手段】三相交流電力を単相2座の電力に変換するき電変圧器1と、前記き電変圧器1の2次側のT座とき電線2Tとを結ぶ電路に介挿された直列コンデンサ3Tと、前記き電変圧器1の2次側のM座とき電線2Mとを結ぶ電路に介挿された直列コンデンサ3Mとを備え、前記き電変圧器1のT座および前記直列コンデンサ3Tの共通接続点5Tと、前記き電変圧器1のM座および前記直列コンデンサ3Mの共通接続点5Mとの間に接続され、単相インバータ12T,12M、インバータ用変圧器11T,11Mおよび直流コンデンサ13を有し、無効電力の補償機能および有効電力の三相平衡化機能を有して前記き電線2T、2Mの電圧補償を行う電圧補償装置20を具備した。

(もっと読む)

スイッチングレギュレータ及びこれを備えた電子機器

【課題】本発明は、変換効率の低下を招くことなく、ノイズ環境下での出力精度を向上することが可能なスイッチングレギュレータを提供することを目的とする。

【解決手段】本発明に係るスイッチングレギュレータ20は、センス抵抗Rsと、センス電圧Vsenseに応じたセンス電流Isenseを生成するセンス電流生成回路213と、ランプ波或いは三角波のスロープ電流Islopeを生成するスロープ電流生成回路214と、加算電流(Isense+Islope)に応じたスロープ電圧Vslopeを生成するスロープ電圧生成回路215と、出力誤差に応じた誤差電圧Verrを生成する誤差増幅器ERRと、誤差電圧Verrとスロープ電圧Vslopeを比較してPWM信号を生成するコンパレータCMPと、PWM信号に基づいて出力トランジスタN1のオン/オフ制御を行うスイッチング制御部CTRLと、を有して成る構成としている。

(もっと読む)

自動力率補正器

電流および電圧の各位相の位相角を感知し、電流の位相角を電圧の位相角に自動的に揃える、コンピュータ制御ソリッドステートスイッチング力率補正器。この力率補正は、電力ラインの周波数で更新され、多数の離散的な補正ステップを提供するように設計される。  (もっと読む)

(もっと読む)

1 - 15 / 15

[ Back to top ]