Fターム[5H420NB31]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 出力部 (2,015) | 複数出力 (42)

Fターム[5H420NB31]の下位に属するFターム

正負出力

多出力カレントミラー回路を用いるもの (26)

Fターム[5H420NB31]に分類される特許

1 - 16 / 16

定電流源回路

【課題】動作の信頼性の向上を図る。

【解決手段】定電流源回路は、複数のPMOSトランジスタを含む第1カレントミラー回路11、複数のNMOSトランジスタを含む第2カレントミラー回路12を備え、正の温度特性を有する第1電流を発生する第1電流発生回路10と、前記複数のNMOSトランジスタの閾値電圧に依存し、負の温度特性を有する第1電圧が入力され、前記第1電圧と等しい第2電圧を出力するフィードバック回路21を備え、前記第2電圧に基づいて負の温度特性を有する第2電流を発生する第2電流発生回路20と、前記第1電流と前記第2電流とを加算することで、任意の温度特性を有する定電流を発生する電流合成回路30と、を具備する。

(もっと読む)

定電圧回路、コンパレータおよびそれらを用いた電圧監視回路

【課題】高いPSRRを有する定電圧回路を提供する。

【解決手段】電流源10は、基準電流Irefを生成する。第1トランジスタM1は、その一端が電流源10と接続され、かつそのゲートソース間が接続されたデプレッション型のMOSFETである。第2トランジスタM2は、その一端が第1トランジスタM1の他端と接続され、その他端が固定電圧端子と接続され、かつそのゲートドレイン間が接続されたエンハンスメント型のMOSFETである。第3MOSFETは、その一端が電流源10と接続され、その他端が固定電圧端子と接続され、かつそのゲートが第1トランジスタM1と第2トランジスタM2の接続点N1と接続されたエンハンスメント型のPチャンネルMOSFETである。定電圧回路100は、第3トランジスタM3のゲート電圧およびそのソース電圧の少なくとも一方に応じた電圧を出力する。

(もっと読む)

バンドギャップ回路、低電圧検出回路及びレギュレータ回路

【課題】オペアンプのオフセット電圧の影響を抑えたバンドギャップ電圧と最低動作電圧を抑えたバンドギャップ電圧とを得ることを目的とする。

【解決手段】開示の装置は、第1及び第2のPNPトランジスタ、第2のPNPトランジスタのエミッタに一端が接続された第1の抵抗、第1のPNPトランジスタのエミッタ及び第1の抵抗の他端が入力に接続され、負帰還制御が行われる第1のオペアンプを有する。また、開示の装置は、第1及び第2のPNPトランジスタのエミッタにベースが接続された第3及び第4のPNPトランジスタ、第4のPNPトランジスタのエミッタに一端が接続された第2の抵抗、第3のPNPトランジスタのエミッタ及び第2の抵抗の他端が入力に接続された、負帰還制御が行われる第2のオペアンプを有する。

(もっと読む)

基準電流電圧発生回路

【課題】基準電流電圧発生回路の起動後には、起動回路が基準電流電圧発生回路の動作へ与える影響を軽減することができる基準電流電圧発生回路を提供すること。

【解決手段】本発明にかかる基準電流電圧発生回路は、複数のトランジスタにより自己帰還回路を構成し、基準電流または基準電圧を発生させる基準電流電圧発生回路であって、基準電流電圧回路の非動作時には、電位が第1の電源と実質的に等しく、基準電流電圧発生回路の動作時には、電位が、第1の電源の電圧から第2の電源VDDの電圧の方向に所定値以上変動する節点101と、第2の電源と、の間に接続され、ゲートが第1の電源に接続されているノーマリーオン型トランジスタ21、を備える

(もっと読む)

バイアス回路

【課題】動作中におけるノイズの侵入によって、回路動作が停止しても、起動回路を再度駆動させることなく、また、外部からリセット信号を入力させることなく、回路動作を復帰可能とし、起動回路における消費電流の低減を図る。

【解決手段】一定の電流を外部へ供給する基準電流供給部100と、基準電流供給部100からの電流供給を受け、供給された電流に電流を生成する定電流供給部110と、基準電流供給部100と定電流供給部110の動作開始のための電流を供給する起動用定電流供給部120とを有し、起動用定電流供給部120からの電流が基準電流供給部100の起動用のアイドリング電流として供給されることでノイズの影響を受けること無く、従来に比して起動時間の短縮が可能となっている。

(もっと読む)

基準電圧出力回路

【課題】大量生産しても基準電圧の出力値のばらつきの少ない基準電圧出力回路を提供する。

【解決手段】基準電圧出力回路10は、基準電圧を出力する第1定電圧回路21A、第2定電圧回路21B及び第3定電圧回路21Cと、第1定電圧回路21Aと第2定電圧回路21Bとの出力電圧を比較し、第2定電圧回路21Bと第3定電圧回路21Cとの出力電圧を比較し、第3定電圧回路21Cと第1定電圧回路21Aとの出力電圧を比較する各セレクタ回路22・23及びコンパレータ24と、比較結果の組から各定電圧回路21A〜21Cのうち中央値を有する定電圧回路を選択する制御部13とを備える。

(もっと読む)

電源回路及びそれを用いた内部電源電圧発生方法

【課題】電源電圧が低下しても所定の基準電圧を生成する。

【解決手段】電源回路40には、パワーオン/オフ回路1、BGR回路用電源電圧発生部2、バンドギャップリファレンス回路3、VINT発生回路4、VPP発生回路5、VAA発生回路6、及び1/2VAA発生回路7が設けられる。BGR回路用電源電圧発生部2には、参照電圧発生回路2a及びBGR回路用電源電圧発生回路2bが設けられる。参照電圧発生回路2aは、パワーオン信号Spwonが入力され、参照電圧Vsn1及び制御電圧Vcmbを生成する。参照電圧Vsn1は、外部高電位側電源Vdd電圧が0.8Vから4Vの範囲で、低温から高温領域まで、外部高電位側電源Vdd電圧依存性がなく、略一定な電圧である。BGR回路用電源電圧発生回路2bは、参照電圧Vsn1及び制御電圧Vcmbが入力され、参照電圧Vsn1を昇圧した、例えば2VのBGR回路用電源電圧Vsn2を生成する。

(もっと読む)

半導体記憶装置

【課題】基準電圧発生回路において、基準電圧の切り替え時における基準電圧の変動を抑制する。

【解決手段】基準電圧発生回路において、分圧回路20は、第1の接点において第1の基準電圧を生成し、第2の接点において前記第1の基準電圧より低い第2の基準電圧を生成し、切替回路30は、前記第1または第2の接点のいずれかと第3の接点との接続を切り替えて前記第3の接点において前記第1または前記第2の基準電圧を生成し、ノイズキャンセル回路50は、前記第3の接点に接続されるとともに、前記第3の接点との接続を前記第1の接点から前記第2の接点へ切り替えた際に前記第3の接点から前記第2の接点に向けて流れる電流を低減し、前記第3の接点との接続を前記第2の接点から前記第1の接点へ切り替えた際に前記第1の接点から前記第3の接点に向けて流れる電流を低減する。

(もっと読む)

電力制御装置

【課題】電源制御装置に関し、電源の給電異常状態を判定し、判定結果に基づいて所定の負荷への給電を制限することで電源に与える負担を軽減するとともに、負荷の作動状態の変化から運転者に給電異常を早期に認知させ、電源の交換を促すことができる電力制御装置を提供することを目的とする。

【解決手段】電源と、前記電源より給電される複数の負荷と、前記電源の給電異常を示す所定の状態を判定する給電異常判定手段と、前記給電異常判定手段の判定結果に基づいて、前記複数の負荷のうちの給電制限対象負荷への給電を制限する給電制限手段とを備えることを特徴とする。

(もっと読む)

基準電流生成装置

【課題】回路面積の大幅な増大を防止して絶対温度比例電流を出力する基準電流生成装置を提供。

【解決手段】トランジスタ(T1) 14と、可変電流源であるトランジスタ(T2) 16と、トランジスタ(T3) 18とを電源ライン(Vdd) 12に接続し、トランジスタ14を抵抗素子(Re) 20とダイオード(D1) 22とを直列に介して電源ライン(Vss) 24に接続し、トランジスタ16をダイオード(D2) 26を介して電源ライン(Vss) 24に接続し、トランジスタ16と抵抗素子20との接続点(Va) 28に演算増幅器30の非反転入力端子(+)を接続し、トランジスタ16とダイオード26との接続点(Vb) 32に反転入力端子(-)を接続して、非反転入力端子(+)に電圧Vaを印加し、反転入力端子(-)に電圧Vbを印加する。演算増幅器30の出力44は、トランジスタ14および18のゲートに共通に接続され、トランジスタ18の出力46からゲート電圧に応じたPTAT電流(Iout)が出力される。

(もっと読む)

バンドギャップ回路

【課題】スイッチトキャパシタ型のバンドギャップ回路において、容量の占有面積を増やすことなく、熱電圧に乗じる係数をより細かく設定すること。

【解決手段】第1のスイッチトキャパシタ回路2のオペアンプ回路OP3の入力端子と、第2のスイッチトキャパシタ回路3のオペアンプ回路OP4の出力端子を、結合容量C7により結合する。結合容量C7の容量値は第1のスイッチトキャパシタ回路2のフィードバック容量C6の容量値よりも小さい。各スイッチトキャパシタ回路2,3の各入力容量C5,C8および各フィードバック容量C6,C9と、結合容量C7の各容量値により決まる係数を熱電圧に乗じて得た、絶対温度に比例するPTAT電圧を、電圧発生回路1で発生した、温度の上昇にともなって電圧値が減少する負の温度依存性を有するpn接合の順方向電圧に加算することによって、温度に依存しない基準電圧を発生させる。

(もっと読む)

電流駆動装置および電流駆動方法

【課題】 製造上のばらつきを制御する回路の面積を削減する。

【解決手段】 バイアス電圧生成部102は、入力端子101に与えられた基準電流Irefの電流値に応じた電圧値を有するバイアス電圧Vbiasをゲート線G103に出力する。出力端子105−1〜105−Kは、駆動トランジスタT104−1〜T104−Kを流れる出力電流Iout−(1)〜Iout−(K)を外部へ出力する。また、バイアス電圧生成部102が受ける基準電流Irefの電流値とバイアス電圧生成部102が生成するバイアス電圧の電圧値Vbiasの電圧値との関係は、制御信号CTa−1〜CTa−P,CTb−1〜CTb−Pによって調整される。

(もっと読む)

電圧ダウンコンバータのためのパワーオン管理

オンチップ電圧ダウンコンバータ(79)用のパワーオン管理システム(80)であって、外部(Vcc_EXT)および内部(Vcc_INT)両方の電圧源を監視して、オンチップ回路が正常に動作するための最低レベルに両方の電源がいつ達したかを独立に判断する。パワーオン管理システム(80)の供給する出力信号としては、パワーオンの開始時に内部電源ノードの放電(DISCH_Vcc)を制御する信号と、電圧ダウンコンバータの活性モード(POW_ON=ハイ)を強制する信号と、パワーオンの完了(POW_ON=ロー)時に高速ローカル電圧基準を不活性化する信号とがある。  (もっと読む)

(もっと読む)

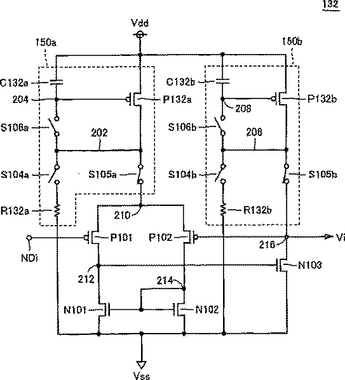

定電流回路、駆動回路および画像表示装置

電圧発生回路114に含まれる第1の増幅回路(132)は、P型TFT素子(P101,P102)およびN型TFT素子(N101,N102)によって構成される差動回路と、定電流回路(150a,150b)と、N型TFT素子(N103)とを含む。定電流回路(150a;150b)は、P型TFT素子(P132a;P132b)と、キャパシタ(C132a;C132b)と、スイッチ(S104a〜S106a;S104b〜S106b)と、抵抗素子(R132a;R132b)とからなる。キャパシタ(C132a;C132b)は、電圧設定時、すなわちダイオード接続されるP型TFT素子(P132a;P132b)に電流が供給されているときのノード(204;208)の電圧を保持する。  (もっと読む)

(もっと読む)

負荷制御装置

【課題】様々な交流及び直流負荷に対して負荷電圧及び負荷の点滅時間を容易に調節することができる負荷制御装置を提供する。

【解決手段】負荷に適合するように変圧帯域幅を調節することが可能な直流負荷変圧器(120)と、オンタイム及びオフタイムの長さの信号を出力し、前記長さを個別的に調節することが可能な主オンオフ調節部(132)と、前記主オンオフ調節部の出力信号と異なる周期を有するオンタイム及びオフタイムの長さの信号を出力し、前記長さを調節することが可能な副オンオフ調節部(133)と、前記直流負荷の初期起動のための信号を出力する起動部(134)と、前記主オンオフ調節部及び副オンオフ調節部の出力信号に応じて前記直流負荷変圧器から供給される電圧が前記直流負荷へ供給されるようにし、前記直流負荷の初期起動時に前記起動部から供給される信号に応じて前記直流負荷へ初期起動電圧が供給されるようにするリレー接点部(140)と、を備えている。

(もっと読む)

定電流回路、記録素子基板及び記録装置

【課題】 温度変化や駆動素子の特性に影響されず、負荷に流れる電流を一定とする。

【解決手段】 負荷101と、負荷に直列に接続された駆動用トランジスタ102と、定電流源103と、PMOS差動対を構成し、それぞれのソースが定電流源103の出力に共通に接続され、それぞれのドレインがカレントミラー回路を構成するNMOSトランジスタ106及び107のドレインにそれぞれ接続されたPMOSトランジスタ104及び105とを設け、駆動用トランジスタ102のドレインの電位を一定とすることにより、負荷101に流れる電流を一定とする。

(もっと読む)

1 - 16 / 16

[ Back to top ]