Fターム[5H730BB57]の内容

DC−DCコンバータ (106,849) | 主変換部の型式 (20,669) | 非共振型 (4,027) | 他励型(発振器を用いるもの) (3,815)

Fターム[5H730BB57]に分類される特許

3,801 - 3,815 / 3,815

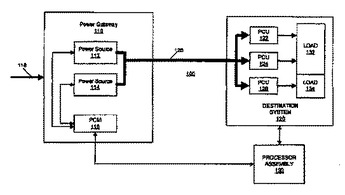

変動負荷用電力変換

1以上の変動負荷(132,134)への電力を効率よく変換する電力変換ユニット(100)と変換方法がここに開示されている。第1の形態を有する電力が1以上の変動負荷に接続された1以上の電力変換ユニット(PCUs)(122,124,126)に供給される。PCUsは、電力を第1の形態から、供給先のシステム(120)で用いるのに適切な他の形態に変換する。前記変動負荷の負荷要求予測の少なくとも一部に基づき、電力消費が減少している間不要なPCUsを停止し、又は、電力消費が増加している間必要なPCUsを作動させて、損失となる電力を最小限にしながら、適切な時間に1以上の負荷に十分な電力を供給するようPCUsの動作を制御する。加えて、負荷要求の一次的な変動予測の少なくとも一部に基づき、電力消費の一時的な増加期間、1以上の変動負荷にエネルギーを追加するために出力電圧を増加し、又は電力消費の一時的な減少期間、出力電圧を減少したりして、負荷要求の一時的な変化に先立ってPCUはその出力電圧を変化させることができる。本発明は、レーダーシステム内で電力を配分するために用いたときに特に有益である。  (もっと読む)

(もっと読む)

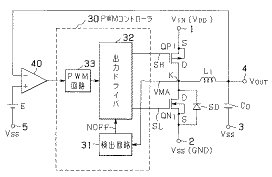

電源回路

【課題】CMOS集積回路を用いた同期整流方式の電源回路などにおいて、電力消費の低減と、部品増や効率低下を伴うことなく負荷変動に対する高速応答が可能な電源回路を提供すること。

【解決手段】PWM信号をゲートに、VIN(=VDD)をソースに接続するPMOS(QP1)のドレインに接続され、VSSをソースに有す、NMOS(QN1)のドレインに接続される中間ノード電圧VMAが、NMOS(QN1)オン時に、アンダーシュートから戻って基準電位VSSレベルを越えたときこれを検出してNMOS(QN1)のゲート電圧をローレベル(オフ)にする。また、NMOS(QN1)オン時に、中間ノード電圧VMAが、アンダーシュートから基準電位VSSレベルに戻ったタイミング(ゼロ点位置)を検出することで、このゼロ点位置検出信号を負荷電流の大小を示す信号としてPWM回路33に帰還してPWM信号のパルス幅を制御し、負荷変化に対応させる。

(もっと読む)

昇圧型スイッチング電源装置

【課題】 昇圧型スイッチング電源において負荷の短絡あるいは過負荷時に生じる損焼を防止する。

【解決手段】 負荷の短絡あるいは過負荷時に、スイッチ素子に定電流機能動作をさせるとともに、PWMコントローラのタイマ・ラッチ機能によって主スイッチング素子のスイッチングを停止する。これによってスイッチング電源は昇圧機能を失い、出力が入力電圧まで低下することによってスイッチ素子の導通も停止され、入出力間を遮断する。正常な動作ではスイッチ素子が導通されて、出力に昇圧電圧が得られる。

(もっと読む)

スイッチング電源装置

【課題】バースト期間と通常動作期間で同じバイアス電流を供給しているので、バースト期間では過剰なバイアス電流を流すことになり、待機時の消費電力を低減することが困難であったという課題を解決する。

【解決手段】トランスの磁束がなくなってから誤差増幅器の出力がある一定値に達するまでのバースト期間は、制御回路に供給するバイアス電流を低減するようにした。消費電力、特に待機時の消費電力が少なくなり、かつ従来の制御回路にゲートとバイアス回路を追加するだけで構成することができる。

(もっと読む)

昇圧電位発生回路及び制御方法

【課題】 半導体メモリにおいて、外部電源電圧が低下しても、半導体メモリ内部では、高速動作を可能にすると共に、小型化をも可能にする昇圧電位発生回路を提供する。

【解決手段】 容量MOSトランジスタとトランスファMOSトランジスタとを備え、メモリセルを含むDRAMに使用される昇圧電位発生回路において、容量MOSトランジスタのゲート絶縁膜を、メモリセルを構成するMOSトランジスタのゲート絶縁膜の膜厚よりも薄い膜厚にすることにより、小面積で大容量の昇圧電位発生回路を実現する。この場合、トランスファMOSトランジスタのゲート絶縁膜の厚さを容量MOSトランジスタのゲート絶縁膜の厚さを同等以上に厚くすることが好ましい。

(もっと読む)

電源回路

【課題】 過大電流が外部から流入しても、素子が破損するのを防止すること。

【解決手段】 トランスTの二次側に、前記FET2および3とチョークコイルLとコンデンサCとの他、フォトカプラPC1,PC2と、トランジスタTr1,Tr2とを有し、トランスTの一次側の主スイッチ1が故障したとき、外部電源Eから過電流が流入しても、これらフォトカプラPC1,PC2とトランジスタTr1,Tr2とによってFET2,FET3の双方がオンするのを防止できるように構成されている。

(もっと読む)

電源回路および電子装置

【課題】本発明の目的は、電源部を大きくすることなく、例えば、モータ等の駆動装置を確実に駆動させることができる電源回路および電子装置を提供する。

【解決手段】本発明の電源回路46は、モータ等の駆動装置に電力を供給する手段であり、電源部40と、DC/DCコンバータ42と、調整回路44とで構成されている。DC/DCコンバータ42は、帰還電圧VFBに基づいて出力電圧V2が所定値となるように制御し、電源部40から入力される電圧(入力電圧V1)を昇圧して、モータへ出力し、そのモータを駆動させる昇圧型のDC/DCコンバータである。調整回路44は、DC/DCコンバータの帰還電圧VFBを調整することにより、DC/DCコンバータ42を、DC/DCコンバータとして機能する「作動状態」と、DC/DCコンバータとして機能しない「非作動状態」とに切り換える。

(もっと読む)

カレントモードDC/DCコンバータ

【課題】 負荷電流の急変時においても出力電圧が大きく変動しないカレントモードDC/DCコンバータを提供する。

【解決手段】 負荷電流Ioが急変すると、フィードフォワード回路41は負荷電流Ioの変化分を検出し、その変化分をコイル電流I2の検出信号に加算する。カレントモード制御回路51は、コイル電流I2の検出信号に負荷電流Ioの変化分を加えた値と、エラーアンプA1からの誤差信号とを比較し、その比較結果に基づきスイッチング素子Q1のスイッチングを制御する。これにより、これにより、負荷電流Ioの急変にコイル電流I2が速やかに変化し、出力電圧Voの変動分は小さくなる。

(もっと読む)

スイッチング電源回路及び電子機器

【課題】 電子機器の極小負荷モード時に、時間の計時やリモコンからの信号を受信、解析する等、本体回路のマイコンの機能の一部又は全部を肩代わりすることができるスイッチング電源回路及び電子機器を提供することである。

【解決手段】 電子機器に装備することができると共に、交流電源をPWM方式により発振させるレギュレータ回路と、この発振させた電圧を整流して単一又は複数の所定の出力電圧を生成する同期整流回路と、レギュレータ回路のPWM制御及び同期整流回路の整流を制御することができる電源制御手段とを備えた電源回路であって、電源制御手段は、電子機器が極小負荷モードに移行した際に、当該電子機器を制御する機器制御手段が行う機能の一部又は全部を肩代わりする。

(もっと読む)

チャージポンプ回路

【課題】高効率で大出力電流のチャージポンプ回路を提供する。

【解決手段】前段2つの電荷転送用MOSトランジスタM1、M2をNチャネル型で構成し、後段2つの電荷転送用MOSトランジスタM3、M4をPチャネル型で構成する。また、中間電位の出力を可能にした反転レベルシフト回路S1とS2、非反転レベルシフト回路S3とS4を設けた。これらの構成により、高効率で大出力電流のチャージポンプ回路を実現できると共に電荷転送用トランジスタM1〜M4のゲート・ソース間電圧Vgs(トランジスタがオン状態の時)を2Vddに揃えることができる。

(もっと読む)

DC/DCコンバータ

【課題】乾電池1本乃至2本程度の低い電圧レベルで動作可能なMOSトランジスタによるDC/DCコンバータを提供することを目的とする。

【解決策】電池からの電力を受けて所定の電圧まで昇圧した電圧の電力を発生して負荷に供給するDC/DCコンバータにおいて、負荷に対して直列あるいは並列に挿入され電池の電源供給ラインに対してスイッチングを行う、寄生バイポーラトランジスタが出力電極側において並列に形成されたMOSトランジスタと、負荷側に出力する電力の一部を受けてこのMOSトランジスタのスイッチングの期間を負荷側の電圧に応じてこの電圧が所定の一定値になるように制御する制御回路と、電池からの電力を受け、制御回路がMOSトランジスタをON/OFFさせることができる所定電圧値より負荷の電圧が低いときに、寄生バイポーラトランジスタをスイッチングさせて負荷側に昇圧電圧を発生させる起動回路とを備えるものである。

(もっと読む)

同期整流方式のスイッチング電源における高周波ノイズ低減方法

【課題】 同期整流方式のスイッチング電源における高周波ノイズを減少させる。

【解決手段】 整流用半導体スイッチ8の信号部に接続した信号部を有する半導体スイッチ6と、還流用半導体スイッチ9の信号部に接続した信号部を有する半導体スイッチ7を設け、同期整流用の半導体スイッチ8と9がターンオフするよりも速く半導体スイッチ6と7をターンオンさせ、同期整流用半導体スイッチ8と9が同時にオンとならないようにした。

(もっと読む)

半導体集積回路装置

【課題】 電源電圧が低下しても安定してワード線電位に用いられる昇圧電圧を供給する。

【解決手段】 第2昇圧回路16は、第1昇圧回路15が生成するワード線電位となる昇圧電源VPPよりも高いレベルの昇圧電圧VPP+αを生成し、静電容量素子17に電荷が蓄積される。電源電圧VCCの低下によって昇圧電圧VPPがしきい値よりも低くとなると、制御信号出力部18から制御信号Cがスイッチング部19に出力され、静電容量素子17に蓄積されていた電荷が電源電圧VPPとして補給される。電源電圧VPPがしきい値よりも高くなると制御信号Cが停止され、スイッチング部19がOFFとなる。昇圧電圧補償制御部SHCがこれらの制御を繰り返すことにより、電源電圧VCCが変動しても昇圧電圧VPPを安定して供給することができる。

(もっと読む)

スイッチング電源回路およびスイッチング電源用デバイス

【課題】 軽負荷時のスイッチング損失をより低減することのできるスイッチング電源回路を提供する。

【解決手段】 定常負荷のときには、出力検出回路20からのフィードバックによって接続点10の電圧はしきい値よりも高く、また接続点7の電圧はしきい値よりも低くなるため、発振周波数休止期間回路11は動作せず発振回路13は三角波を連続して出力する。一方、軽負荷になると、出力検出回路20からのフィードバックによって接続点10の電圧はしきい値よりも低く、また接続点7の電圧はしきい値よりも高くなるため、発振周波数休止期間回路11が動作して、発振回路13は発振の休止期間が設けられた三角波を出力する。これに伴いスイッチング素子Q1は一定期間遮断された状態で休止するようなスイッチング動作を行う。

(もっと読む)

DC−DCコンバータ

【課題】内蔵する単相全波整流回路の高周波電圧バイパス用のスナバ回路の小型化及び寿命延長が可能なDC−DCコンバータを提供すること。

【解決手段】トランス60の二次コイルの両端は整流素子8,8を通じて直流出力端子に接続され、二次コイルを構成する一対の部分コイル61,62の直列接続端6aが一対の直流出力端子の他方に接続されるとともにベースプレートに電気的に接続されて接地端となる。トランス6の二次コイルの両端に接続されるスナバ回路7を一対のCRフィルタ71,72で構成し、かつ、両CRフィルタ71,72の直列接続端をなす導体6aをその直下のベースプレートの主面に介在導体を通じて接する。このようにすれば、単相全波整流用のトランスの二次コイルの一対の部分コイル61,62をそれぞれCRフィルタ71,72でバイパス接続する回路構成となるので、スナバ回路7の高周波電圧バイパス効果を低下することなく、スナバ回路7の発熱を両CRフィルタ71,72の直列接続端からベースプレートへ介在導体を通じて良好に放熱できる。

(もっと読む)

3,801 - 3,815 / 3,815

[ Back to top ]