Fターム[5H740BA16]の内容

電力変換一般 (12,896) | 主回路スイッチング素子 (1,744) | 補助スイッチング素子を持つもの (17)

Fターム[5H740BA16]に分類される特許

1 - 17 / 17

電力変換装置及びその制御方法

【課題】回路の寄生インダクタンスとスイッチング素子の接合容量による高周波振動を抑制しつつ、スイッチング素子の損失の低減が可能な電力変換装置を提供する。

【解決手段】制御スイッチング素子4とダンピング抵抗3の並列接続で構成した振動制御部を電力変換回路の入力電源1と主スイッチング素子7の間に設置し、制御スイッチング素子4と主スイッチング素子7の間にはRon(S2)<E(Rg)x fsw /(D x I2)の関係を有しており、主スイッチング素子7がターンオフし、主スイッチング素子7の電流がゼロになった後に、制御スイッチング素子4をオフし、回路の寄生インダクタンス2と主スイッチング素子の接合容量間で発生する高周波振動をダンピング抵抗3で抑える。

(もっと読む)

共振型コンバータ装置

【課題】共振回路の損失とコストとを低減し且つ小型化できる共振型コンバータ装置。

【解決手段】直流リンクの正極側と負極側とに接続され、コンデンサC5とコンデンサC6との第1直列回路と、第1直列回路の両端に接続されスイッチQ1とスイッチQ2との直列回路と、Q1に並列に接続されたコンデンサC1と、Q2に並列に接続されたコンデンサC2と、第1直列回路の両端に接続されスイッチQ3とスイッチQ4との直列回路と、商用電力系統と、Q1とQ2との接続点及びQ3とQ4との接続点とに接続されたLC回路15と、C5とC6との接続点とQ1とQ2との接続点との間に接続されスイッチQ5,Q6と共振用リアクトルL3との直列回路と、Q1とQ2とをPWM制御すると共にQ3とQ4とを交互に180度期間オンさせ、Q1及びQ2がオフ期間にQ5,Q6をオンさせC1とC2とL3との共振動作によりゼロ電圧スイッチングを行う制御回路13とを備える。

(もっと読む)

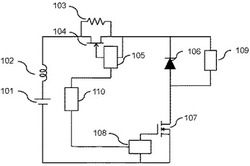

逆耐圧を有するIGBTの過電流保護回路

【課題】逆耐圧を有するIGBTの短絡保護回路として、ゲート駆動回路とIGBTのコレクタとの間にダイオードを接続して、過電流時コレクタ電圧が上昇した時、ゲート遮断する方式では、駆動回路に逆電圧がかかり破壊される。

【解決手段】ゲート駆動回路とIGBTのコレクタとの間にダイオードと抵抗の直列回路を接続し、さらにゲート信号遮断用トランジスタのエミッタと制御端子に接続した定電圧ダイオードのカソードとの間にダイオードを設ける。

(もっと読む)

車両の電源供給装置及び電源供給方法

【課題】自動車用半導体ヒューズの低消費電流化を図ると共に通電電流が非常に小さい場合のスイッチングを可能とする車両の電源供給装置及び電源供給方法を提供する。

【解決手段】電源と負荷との間に半導体リレーが配置された車両の電源供給装置において、第1の半導体リレー11と、第2の半導体リレー12と、第1の半導体リレー駆動用の昇圧器114を有しかつ第1の半導体リレー及び第2の半導体リレーを制御する制御部100と、を備え、車両の定常状態においては昇圧器を介して第1の半導体リレーを駆動して負荷に電力を供給すると共に、車両の特定の状態を検出した場合に第1の半導体リレーの駆動に変えて第2の半導体リレーを駆動させるようになっている。

(もっと読む)

半導体装置

【課題】半導体集積回路への電源供給がなくても、負荷駆動システムにおける負荷開放状態が検出できる半導体装置を提供する。

【解決手段】半導体装置10は、負荷装置4をスイッチング制御するためのパワー半導体素子1、および負荷装置4の異常を検出する半導体集積回路2を備え、さらにパワー半導体素子1の出力端子電圧を抵抗分圧するプルダウン用の分圧回路20、分圧回路20を構成するプルダウン用抵抗14,15から電源供給を受けて負荷装置4の開放検出を行うMOSFET16、および半導体集積回路2から出力される異常信号によってオン、あるいはオフ動作するMOSFET17が内蔵されている。また、負荷装置4の開放状態の検出結果を外部に出力する状態出力端子18を備えている。

(もっと読む)

電源制御装置及びこれを備えた電子機器

【課題】装置仕様と異なる高電圧の電力が画像形成装置に供給された場合でも、電源装置に過電圧が印加されることを簡単かつ確実に防止する。

【解決手段】画像形成装置1に設けられたPLC部(電源制御装置)7が、電力線34を介して他の装置との通信を行うPLC通信・電源制御部42と、電力線と電源部(電源装置)15との間に介在し、電源部に電力線から供給される電力のオンオフを切り替えるサブ電源スイッチ43とを備え、PLC通信・電源制御部は、電圧検出部の検出結果に基づきサブ電源スイッチの動作を制御し、電圧検出部で検出された電圧が画像形成装置の仕様電圧と異なる場合、サブ電源スイッチをオフ状態のままとして電源部に電力を供給しないようにする。

(もっと読む)

スイッチング素子駆動回路

【課題】チップサイズを小さくすると共に、製造コストが嵩むことのないスイッチング素子駆動回路を提供する。

【解決手段】電力変換回路のスイッチング素子を流れる電流を電圧値として検出する電流検出回路40と、該電流検出回路40で検出した電圧値と第1の基準電圧Vb1とを比較して過電流状態を検出したときに過電流検出信号を出力して前記駆動回路の前記スイッチング素子の制御端子に対するソース電流の供給を停止させる過電流状態制御部50と、前記電流検出回路40で検出した電圧値と第2の基準電圧Vb2とが入力され、出力が前記駆動回路の出力側に供給されると共に、前記過電流状態制御部50から過電流検出信号が出力されたときに動作状態となる演算増幅器61を有し、該演算増幅器61が動作状態となったときに前記駆動回路23の出力電圧を前記第2の基準電圧に合わせて安定化する出力電圧制御部60とを備えた。

(もっと読む)

サイリスタのゲートドライブ回路

【課題】瞬低装置に備えられたサイリスタのゲートドライブ回路においては、通常運転時における信頼性をさらに向上させることが要求される。

【解決手段】瞬低装置に備えられたサイリスタS1,S2を制御するサイリスタのゲートドライブ回路に、1次側が制御用電源3に接続され、2次側が前記サイリスタS1,S2と並列に接続されたフォトカプラPC1,PC2を設ける。前記サイリスタS1,S2の制御方法としては、前記サイリスタS1,S2をオン状態とする場合、前記フォトカプラPC1,PC2をオフにし、商用電源1から出力された電流をサイリスタS1,S2のゲートに印加する。一方、前記サイリスタS1,S2をオフとする場合、前記フォトカプラPC1,PC2をオンにし、商用電源1から出力された電流をサイリスタのゲートに印加させないようにする。

(もっと読む)

スイッチング電源回路

【課題】軽負荷時においてもスイッチング素子を駆動する回路への電力供給を安定して行うことができる低廉なブートストラップ型スイッチング電源回路を提供する。

【解決手段】スイッチング素子1と、スイッチング素子1のソースに一端が接続されるブートストラップ用コンデンサC1を有するブートストラップ回路と、前記ブートストラップ回路から出力されるブートストラップ電圧VBを利用してスイッチング素子のゲートに供給する駆動信号を生成するドライブ回路4と、スイッチング素子1のソースとグランドとの間に設けられる電圧制御用DMOS5と、電圧制御用DMOS5を流れる電流を制限する電流制限部(電圧検出用DMOS6、電圧検出用NMOS7、電圧検出用抵抗8、コンパレータ11、DMOSドライバ9)とを備えるスイッチング電源回路。

(もっと読む)

ラインフィルタ用チョーク、ラインフィルタおよびラインフィルタを有する電気装置

【課題】定格動作において可能な限り損失出力が小さく、不均衡で非対称な減衰を発生させ、これにより給電網インピーダンスが関与する共振と、これに関連する過電圧とを回避する回路装置の実現。

【解決手段】ラインフィルタ用チョークは、1次巻線(1a、1b、1c)及び2次巻線1dを有し、1次巻線(1a、1b、1c)は、チョークと1次側回路2と接続する為のものであり、又2次巻線1dは2次側回路4を有し、1次巻線(1a、1b、1c)及び2次巻線1dは1つの巻線コア3に配置されて、2次側回路4には減衰部材(5a、5b、5c)が含まれ、これら減衰部材(5a、5b、5c)は、チョークを用いて1次側回路2において減衰を行う形式のチョークにおいて、減衰部材(5a、5b、5c)には、1次側回路特性量に応じて前記減衰を行う手段が含まれて、1次側回路特性量は、例えば、1次側回路の電圧又は電流又は周波数であるチョークの構成。

(もっと読む)

出力回路短絡保護回路

【課題】本発明は、出力回路に接続された短絡検出回路を用いて短絡検出を行い、従来の不要な電圧降下を防止することを目的とする。

【解決手段】本発明による出力回路短絡保護回路は、駆動制御回路(15)へ出力駆動信号(6)が入力されると、短絡検出用駆動回路(11)が駆動され、短絡検出回路(14)からの検出信号(14a)により出力回路(4)の短絡有無を検出した後に出力駆動回路(10)を駆動させる構成である。

(もっと読む)

双方向スイッチの保護回路

【課題】高耐圧の素子を使用せずに過電圧からの保護を可能にした低コストの保護回路を提供する。

【解決手段】双方向スイッチ1を過電圧から保護する保護回路において、順方向に直列接続された第1,第2のダイオード2,3の直列接続点を双方向スイッチ1の一端に接続し、かつ、順方向に直列接続された第3,第4のダイオード4,5の直列接続点を双方向スイッチ1の他端に接続すると共に、第1のダイオード2と第3のダイオード4とを逆方向に直列接続し、かつ、第2のダイオード3と第4のダイオード5とを逆方向に直列接続し、第1,第2のダイオード2,3の直列回路に並列に第1のコンデンサ7を接続すると共に、第3,第4のダイオード4,5の直列回路に並列に第2のコンデンサ6を接続する。

(もっと読む)

絶縁ゲート型半導体素子のゲート回路

【課題】 負側電源の故障が発生しても、絶縁ゲート型半導体素子が誤オン動作しないような安全な絶縁ゲート型半導体素子のゲート回路を得る。

【解決手段】 正側電源2Aと負側電源2Bで動作し、絶縁ゲート型半導体素子3のゲート駆動を行うFET12A及びFET12Bから成るトーテムポール回路と、ゲート制御IC11と、ゲート制御ICの出力とFET12Aのゲート間に設けたツェナーダイオード15A及び抵抗14Aから成る直列回路と、ゲート制御ICの出力とFET12Bのゲート間に設けたツェナーダイオード15B及び抵抗14Bから成る直列回路とで構成し、ツェナーダイオード15Aの降伏電圧は、正側電源の電圧からFET12Aのゲートしきい値電圧を減算した値より大きく、ツェナーダイオード15Bの降伏電圧は、負側電源の電圧からFET12Bのゲートしきい値電圧を減算した値より小さく選定する。

(もっと読む)

電力用半導体スイッチモジュール

【課題】単一の回路構成により電流形インバータやマトリクスコンバータ等の各種電力変換装置への適用を可能にして汎用性、経済性を高めた電力用半導体スイッチモジュールを提供する。

【解決手段】逆耐圧性電力用半導体スイッチを複数備えた電力用半導体スイッチモジュールにおいて、自己消弧形半導体スイッチ素子11(12)とダイオード21(22)とを直列接続して逆耐圧性電力用半導体スイッチ61〜66を構成し、これらを各2個直列接続してなる直列回路の両端、及び、この直列回路内の逆耐圧性電力用半導体スイッチ同士の直列接続点を、外部接続用の端子A〜F,G〜Iにそれぞれ接続してモジュール100Aを構成する。

(もっと読む)

電力供給制御装置及び半導体装置

【課題】電力供給制御装置において、異常を精度高く検出しうる構成を提供する。

【解決手段】 電力供給制御装置10は、パワーMOSFET15と、パワーMOSFET15の電流量に応じたセンス電流が流れるセンスMOSFET16と、センス電流と閾値電流とに基づいて、パワーMOSFET15に流れる電流の異常検出を行う異常検出回路13とがワンチップ化されて半導体スイッチ素子11が構成されている。半導体スイッチ素子11の外部には、パワーMOSFET15のソース端子に接続され、他端が、半導体スイッチ素子11の外部端子P4と接続され、一端の接続点の電圧レベルVsに応じた電流を、外部端子P4を通して流す外付け抵抗12が設けられている。異常検出回路13は、外部端子P4に接続されると共に、外部端子P4を通して流れる電流に応じた閾値電流Ia、Ibと、センス電流とを比較することに基づき異常信号SC,OCを出力する。

(もっと読む)

スナバ装置

【課題】 比較的安価な回路構成で、第1および第2端子間に過電圧がかからないようにすることが可能なスナバ装置を提供する。

【解決手段】 スナバ装置は、IGBT1のコレクタ−エミッタ間に並列接続されるIGBT2と、IGBT2のコレクタ−エミッタ間電圧に相関する電圧を検知する電圧検知回路3と、電圧検知回路3の検知結果に基づいてIGBT2のゲート電圧を制御して、IGBT1のコレクタ−エミッタ間電圧を制御する電圧制御回路4とを備えている。IGBT1のターンオフ時に、IGBT1のコレクタ−エミッタ間電圧が所定電圧を超えたか否かを電圧検知回路3で検知し、所定電圧を超えた場合には、IGBT1に並列接続されたIGBT2に主電流の一部を迂回させるようにしたため、ターンオフ時にIGBT1のコレクタ−エミッタ間電圧が所定電圧以上にならなくなる。

(もっと読む)

半導体スイッチ回路

【課題】 電力変換装置のスイッチング手段または整流手段として用いられる半導体スイッチ回路の発生損失を低減する。

【解決手段】 逆並列接続される外付けダイオードまたは内蔵ダイオードを還流ダイオードとするSiCを素材とする静電誘導トランジスタを主スイッチ素子に並列に接続し、オン・オフ制御のタイミングを主スイッチ素子に同期させる。

(もっと読む)

1 - 17 / 17

[ Back to top ]