Fターム[5H740MM05]の内容

電力変換一般 (12,896) | 保護 (1,231) | 電圧に関する検出、保護 (513) | 逆電圧保護 (32)

Fターム[5H740MM05]に分類される特許

1 - 20 / 32

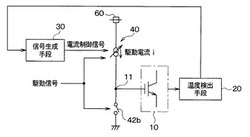

半導体スイッチング素子駆動装置

【課題】半導体スイッチング素子の温度変化によるサージ電圧の発生および変動を抑制すると共にスイッチング損失を低下させることができる半導体スイッチング素子駆動装置を提供する。

【解決手段】各切替スイッチ42a、42bが駆動信号に従ってオン/オフすることにより、駆動手段40が半導体スイッチング素子10の制御端子11に駆動電流を供給する。一方、温度検出手段20によって半導体スイッチング素子10の素子温度または半導体スイッチング素子10の動作環境温度を検出する。そして、駆動手段40は、温度検出手段20によって検出された素子温度または動作環境温度に従って制御端子11に印加する駆動電流の大きさを変更する。これにより、半導体スイッチング素子10の温度変化によるサージ電圧の発生および変動が抑制され、スイッチング損失が低下する。

(もっと読む)

ゲート回路

【課題】本発明は、パワー素子の過電流を速やかに抑制しつつ、di/dtを小さくしてパワー素子をオフすることができるゲート回路を提供することを目的とする。

【解決手段】本発明に係るゲート回路は、パワー素子の過電流発生と同時にパワー素子のゲート電圧の一部を抵抗素子に負担させる過電流抑制手段を有する。さらに、パワー素子の過電流を抑制した後は、抵抗値の高い抵抗素子を用いてパワー素子をゆっくりオフするオフ動作遅延手段を有する。

(もっと読む)

半導体スイッチ

【課題】 主素子の逆並列ダイオードの逆回復特性を改善することができ、構成素子の耐電圧化を図ることができる半導体スイッチを提供する。

【解決手段】 半導体スイッチ7は、スイッチング素子1及び逆並列ダイオード2を有した主素子3と、逆電圧印加回路6と、を備えている。逆電圧印加回路6は、補助電源12と、高速還流ダイオード4と、補助素子5と、コンデンサ13と、を有している。高速還流ダイオード4は、多直列に接続された複数のダイオード15で形成されている。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

スイッチング回路、ハーフブリッジ回路および三相インバータ回路

【課題】リカバリサージ電圧の発生を抑制することにより素子破壊を防ぐ、スイッチング回路、ハーフブリッジ回路および三相インバータ回路提供すること。

【解決手段】回路開閉端子と制御信号用端子とボディダイオードとを有する第1および第2のスイッチング素子が逆直列に接続された直列回路と、直列回路に第1のスイッチング素子のボディダイオードと同じ導通方向で並列に接続された外付けダイオードと、第1のスイッチング素子に流れる電流方向を検出する電流検出回路と、電流検出回路で検出した電流方向が第1のスイッチング素子のボディダイオードに対して順方向に流れる場合には第1および第2のスイッチング素子を閉制御し、電流検出回路で検出した電流方向が第1のスイッチング素子のボディダイオードに対して逆方向に流れる場合には第1および第2のスイッチング素子をゲート信号に基づいて開閉制御する制御手段とを備える。

(もっと読む)

誘導性負荷駆動装置

【課題】電源回路における回路素子の破壊を防止することが可能な誘導性負荷駆動装置を提供する。

【解決手段】誘導性負荷駆動装置の構成として、電源回路の出力端子と誘導性負荷の一端との間に介挿された第1のスイッチング素子と、前記誘導性負荷の他端とアースとの間に介挿された第2のスイッチング素子と、前記第1及び第2のスイッチング素子の両方がオフの時に前記誘導性負荷の他端から出力される逆起電流を前記電源回路の出力端子に回生させる逆起電流回生回路と、前記電源回路の出力電圧が予め設定された閾値以上となった場合に、前記第2のスイッチング素子をオンにする回路素子保護回路と、を備えた構成を採用する。

(もっと読む)

半導体スイッチ、制御装置、電力変換装置及び半導体装置

【課題】異常停止時においても主素子の逆並列ダイオードを通流させることで、還流ダイオードにおける発熱を抑え、還流ダイオードの冷却が容易にした電力変換装置を提供する。

【解決手段】実施形態の半導体スイッチ制御装置は、各相のアーム毎に、主素子3の負極と補助素子5の負極とを接続して主素子の正極を正極端子7とし、補助素子の正極を負極端子8とし、正極端子と負極端子との間に負極端子から正極端子に向かう方向が順方向となるように還流ダイオード4を並列接続した半導体スイッチに対して、主素子と補助素子とをそれぞれ個別にON/OFF制御する。

(もっと読む)

電源逆接続保護回路

【課題】外部直流電源の逆接続や負サージの印加を認識し、確実に電子制御装置に過電流が発生することを防止できる電源逆接続保護回路を提供する。

【解決手段】外部直流電源の高電位側端子2と低電位側端子3とに接続される整流器12が備えられる。この整流器12の高電位側ノード13及び低電位側ノード14は逆接続保護制御回路11に接続される。外部直流電源の逆接続状態でも、整流器12は高電位側ノード13に高電位を発生し、低電位側ノード14に低電位を発生する。従って、逆接続保護制御回路11の比較器15は、電源端子3とグランド端子5への外部直流電源の逆接続状態を判定し、逆接続保護素子駆動回路16は逆接続保護素子10を確実にオフ動作させる。その結果、グランド端子5から電源端子3への過電流は確実に防止される。

(もっと読む)

電圧駆動型半導体素子のゲート駆動装置

【課題】還流ダイオードが小電流で逆回復する時のサ−ジ電圧や振動電圧を抑制するために、対向アームのIGBTのゲートオン抵抗を大きくする方法があるが、定常時の損失が大きくなる課題がある。

【解決手段】ターンオフ時におけるゲート閾値電圧を検出し、この電圧値が所定値に対して高いか低いかを判定し、次のターンオン時のゲートオン抵抗、オン用ゲート電源電圧などのゲート駆動条件を切替える。従って、還流ダイオードの順方向電流が小さい時だけ、ゲート条件を切替えるので、定常時の損失は大きくならない。

(もっと読む)

誘導性負荷の駆動装置

【課題】逆起電圧を吸収させるに際して所望の還元電流特性を得つつ、過度な発熱が生じるのを防止できるような誘導性負荷の駆動装置を提供する。

【解決手段】第1のスイッチング素子28と、第2のスイッチング素子30と、外部供給電源12に接続される電路44を有すると共に、第1のスイッチング素子がオフ、第2のスイッチング素子がオンされるとき、誘導性負荷の逆起電圧によって生じる逆起電流をアースに還流させる還流回路18と、第1、第2のスイッチング素子28,30がオフされるとき、逆起電圧を外部供給電源12に吸収させると共に、逆起電圧を吸収する逆起電圧吸収回路20と、逆起電圧吸収回路20に介挿されると共に、逆起電圧吸収回路20に吸収される逆起電圧の電圧量を切り換える切換手段52を備えるように構成する。

(もっと読む)

電源回路

【課題】過電流検出用抵抗の電源側と過電流制御回路とが遮断された場合にも、過電流保護を可能とする電源回路を提供すること。

【解決手段】負荷に対する過電流を検出した場合に、電源の供給を遮断する電源回路において、前記負荷に対する過電流を検出し、前記負荷と過電流検出用抵抗との間に設けられたスイッチ素子のオン/オフを制御する過電流制御回路と、前記過電流検出用抵抗の電源側の端子と前記過電流制御回路との遮断を検出する検出回路とを有し、前記検出回路は、前記遮断を検出したとき、前記スイッチ素子をオフとする。

(もっと読む)

電力供給制御回路

【課題】ターンオフ時に出力端子に発生する逆起電圧に対して、電源の逆接続回路の影響を受けずに過電圧保護回路が正常に動作する電力供給制御回路を提供することである。

【解決手段】第1電源ライン101と出力端子106との間に接続される出力トランジスタ109と、出力端子と第2電源ライン102との間に接続される負荷112と、出力トランジスタ109の制御端子と第1電源ライン101との間に接続され負荷からの逆起電圧に対して導通状態となるスイッチトランジスタ110を含んで構成される過電圧保護回路と、電源が電源ラインに逆方向に接続された場合は出力トランジスタの制御端子に対して電気通路を形成し、一方、正常に接続された場合はその電気通路を負荷からの逆起電圧に対しても遮断状態とする電源逆接続保護回路(114、115、121、122)を備えて構成される。

(もっと読む)

電力供給制御回路

【課題】負荷サージ電圧に対する出力トランジスタ保護のために設けた過電圧保護回路が、電源の逆接続時に誤動作してしまい、電源逆接続保護回路を設けたにもかかわらず出力トランジスタを非導通にしてしまうことを防止した電力供給制御回路を提供することにある。

【解決手段】第1電源ライン101と出力端子106との間に接続される出力トランジスタ109と、出力端子と第2電源ライン102との間に接続される負荷112と、出力トランジスタ109の制御端子と第1電源ライン101との間に接続され負荷からの逆起電圧に対して導通状態となるスイッチトランジスタ110を含んで構成される過電圧保護回路と、電源が電源ラインに逆方向に接続された場合は出力トランジスタの制御端子に対して電気通路を形成する電源逆接続保護回路とを備え、さらに、スイッチトランジスタ110の与える基準電圧として、電源が正常に接続された場合は第2電源ラインの電圧とし、電源が逆に接続された場合は第1電源ラインの電圧とする基準電圧制御回路131を設けた

(もっと読む)

スイッチング装置

【課題】抵抗素子と容量素子との並列回路が半導体スイッチング素子のコレクタ−ゲート間に設けられている構成において、容量素子が過充電されないように放電経路を確保することができる、スイッチング装置の提供を目的とする。

【解決手段】半導体スイッチング素子Q1のスイッチング装置であって、半導体スイッチング素子Q1のコレクタ−ゲート間に設けられ、並列接続された抵抗素子R1と容量素子C1とを有する並列回路と、前記並列回路と前記コレクタとの間に設けられ、前記コレクタ側の向きに自身に印加される電圧が第1の基準値を超えると前記並列回路側の向きに電流を流すツェナーダイオードZ1,Z2と、前記並列回路と前記コレクタとの間に設けられ、前記並列回路側の向きに自身に印加される電圧が第2の基準値を超えると前記コレクタ側の向きに電流を流すツェナーダイオードZ3とを備えることを特徴とする、スイッチング装置。

(もっと読む)

インダクタ負荷ドライブ回路の逆起電力吸収回路

【課題】 実装面積が小さいサージ吸収保護回路の提供。

【解決手段】 インダクタ負荷(RL)を駆動するバイポーラトランジスタ(TR)のサージ吸収保護回路(100)において、前記インダクタ負荷はバイポーラトランジスタのコレクタ(C)に接続され、前記バイポーラトランジスタに対して双方向ツェナーダイオード(ZD)と第一抵抗(RB)を導線(104)により並列に設け、前記バイポーラトランジスタのエミッタ(E)により導線(103)をアース(GND)し、前記第一抵抗(RB)の他端側は導線(105)により導線(103)に接続し、双方向ツェナーダイオードと第一抵抗間の導線(104)にバイポーラトランジスタのベース(B)に接続する導線(106)を分岐させ、この導線(106)の他端に第二抵抗(R2)を設けた構造のインダクタ負荷ドライブ回路の逆起電力吸収回路。

(もっと読む)

インダクタ負荷ドライブ回路の逆起電力吸収回路

【課題】実装面積が小さいサージ吸収保護回路の提供。

【解決手段】インダクタ負荷RLは導線101に接続され、他端は導線102により電界効果トランジスタFETのドレインDに接続され、電界効果トランジスタに対して双方向ツェナーダイオードZDと第一抵抗RGSを導線104により並列に設け、電界効果トランジスタのソースSより導線103をアースし、第一抵抗RGSの他端側は導線105により前記導線103に接続し、双方向ツェナーダイオードと第一抵抗RGS間の導線104に電界効果トランジスタのゲートGに接続する導線106を分岐させ、この導線106の他端に第二抵抗R2を設けたインダクタ負荷ドライブ回路の逆起電力吸収回路100。

(もっと読む)

電力変換装置のゲート抵抗配置構造

【課題】スイッチングパワーデバイスのオンオフ時におけるサージ電圧からのスイッチングパワーデバイスの保護と、スイッチング損失の低減との両立を図ることができる電力変換装置のゲート抵抗配置構造を提供する。

【解決手段】電力変換装置の使用開始からの経過時間に応じて大きな温度上昇が生じるスイッチングパワーモジュール1と同じ基板15の実装面にこれと隣接して、あるいは、スイッチングパワーモジュール1と反対側の基板15の面にこれと対向して、ゲート抵抗3を実装、配置する。ゲート抵抗3には、スイッチングパワーモジュール1がいかなる温度であってもサージ電圧がスイッチングパワーモジュール1の耐電圧値以内に収まるような、温度変化に対する抵抗値変化の特性を有するものを使用する。望ましくは、サージ電圧に対してスイッチングパワーモジュール1の耐電圧値が過剰なマージンを持つことにならないような特性のゲート抵抗3を用いる。

(もっと読む)

サイリスタ用ゲート駆動装置

【課題】サイリスタ素子がターンオフ時に故障しないようにする。

【解決手段】サイリスタ素子2の制御電極3のゲート電圧を正電位にする順バイアス電圧手段5と、負電位にする逆バイアス電圧手段6とを具備したサイリスタ用ゲート駆動装置において、サイリスタ素子の主電極に流れる陽極電流又は陰極電流の電流値を監視する電流監視手段10と、この電流監視手段で検出された電流値が入力され、この入力された電流のサイリスタ素子がターンオフ開始直前の電流値が、サイリスタ素子のオン電流最大定格値に対してどのくらいの割合であるかを演算する電流演算手段11と、この電流演算手段の出力値に対応して、サイリスタ素子の制御電極に印加するゲート電圧の逆バイアス定常値を制御する逆バイアス定常値制御手段12とを備えている。

(もっと読む)

スナバ回路

【課題】簡単な回路でありながら電圧抑制効果が高く、電力損失が少ないだけでなくスナバエネルギーの回生先となる直流電圧源が存在しない回路部分にも適用可能なスナバ回路を提供する。

【解決手段】保護対象の半導体素子と並列に接続されて、過電圧から該半導体素子を保護するスナバ回路であって、このスナバ回路は、所定電圧の直流電圧源と、その両端に印加される電圧が高くなるとその静電容量が減少する一方、印加される電圧が低くなると静電容量が増加する可変容量コンデンサとが直列に接続された直列回路を備える。

(もっと読む)

保護回路及び電子装置

【課題】過電圧及び逆電圧に対する保護を行う。

【解決手段】保護回路1は、エミッタが入力側端子と接続されるトランジスタ2と、ゲートがトランジスタ2のコレクタと接続される一方でドレインが前記入力側端子に接続されるFET素子Q1と、ゲートがトランジスタ2のコレクタと接続される一方でドレインが出力側端子に接続されるFET素子Q2と、トランジスタ2のベースと接続されると共に前記出力側端子の電圧の分圧と基準電圧とを比較する誤差検出部3とを備える。前記出力側端子の電圧の分圧が前記基準電圧よりも高い場合には誤差検出部3から供給された電流によるトランジスタ2のコレクタ電流の増加に起因するゲート電圧の上昇に基づきFET素子Q1はドレイン電圧を低減させる。一方、前記入力側端子と前記出力側端子との間に逆電圧が印加された場合にはFET素子Q1,Q2は非導通状態となる。

(もっと読む)

1 - 20 / 32

[ Back to top ]