Fターム[5J001BB03]の内容

Fターム[5J001BB03]に分類される特許

1 - 20 / 48

パルス幅延長回路および方法

半導体記憶装置

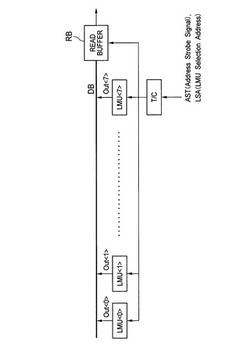

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

PWM出力装置及びモータ駆動装置

【課題】PWM出力幅を細かい単位で正確に制御する。

【解決手段】正相と逆相のPWM信号に対するデッドタイム挿入処理を以下のように行う。PWM信号の出力幅が所定のデッドタイム期間よりも大きく設定された基準期間よりも小さい場合はクリア信号を出力し、大きい場合はセット信号を出力する。セット信号が出力された場合は、PWM信号を補正PWM信号として出力する。クリア信号が出力された場合は、正相のPWM信号をインアクティブとする補正を行って補正PWM信号として出力する。デッドタイム挿入ブロックは補正PWM信号に対して、正相と逆相の信号が同時にオンすることを防ぐようにデッドタイムを挿入する。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

動作クロック生成装置、動作回路、及び、画像形成装置

【課題】少なくとも動作クロックの立ち上がりまたは立ち下がりのタイミングが所望のスペクトラム拡散クロックの周波数である動作クロックを生成する動作クロック生成装置、並びに、その動作クロック生成装置を用いた動作回路及び画像形成装置の提供。

【解決手段】基準クロックを計数したカウンタ値の増加に応じて、その基準クロックの立ち上がりタイミングを(A)に示す遅延量tr0〜tr23で遅延補正し、立ち下がりタイミングを(B)に示す遅延量tf0〜tf23で遅延補正した動作クロックを出力する。カウンタ値が1つ増加する間の遅延量trの各増減幅が、EMIを十分に抑制可能な所望の第1スペクトラム拡散クロックにおいて各クロックの立ち上がりタイミングが取る各周波数にそれぞれ相当する値となるように、遅延量tr0〜tr23を設定している。遅延量tf0〜tf23も、所望の第2スペクトラム拡散クロックに応じて設定している。

(もっと読む)

パルス幅制御回路及び半導体メモリ

【課題】トランジスタのプロセス依存と配線幅のばらつきとに応じて適切なパルス幅に制御することが可能なパルス幅制御回路及び半導体メモリを提供すること。

【解決手段】配線による遅延とインバータによる遅延とを比較する比較回路と、インバータ段数によりパルス幅を調整するパルス幅調整回路と、を備える。パルス幅調整回路は、比較回路の比較結果に基づいて、インバータによる遅延が配線による遅延よりも小さくなった場合に、インバータ段数を多くし、パルス幅を増加させる。

(もっと読む)

メモリインタフェース回路

【課題】マスクタイミングを制御する回路規模を小さい構成で実現すること。

【解決手段】ドライブ制御コードに応じてドライブ特性が変化する第1素子と、I/Oバッファの特性と比例関係にあるドライブ特性の第2素子とを比較し、両素子の特性が一致するか否かを示す調整用モニタ信号を出力するドライブ調整用バッファ20と、調整用モニタ信号に応じて、I/Oバッファの特性と比例関係にあるドライブ制御コードを出力するドライブ能力制御回路14と、システムクロックに応じて、システムクロックの1クロックに相当する遅延値に対応する遅延制御コードを出力する遅延制御回路13と、ドライブ制御コードと遅延制御コードとに基づいて遅延データを計算する遅延計算回路16と、遅延データに基づいて、リード時のデータストローブ信号のマスクタイミングを制御するマスク制御回路17と、を備える。

(もっと読む)

クロックデューティ補正回路

【課題】出力されるクロック信号が発振することなく、デューティが一定になるようにクロック信号を補正することが可能なクロックデューティ補正回路を提供する。

【解決手段】クロックデューティ補正回路100は、クロック信号発生部から出力されたクロック信号が入力され、当該クロック信号の波形の立ち上がりに合わせて波形が立ち上がり、信号の周期が一定となるワンショットパルス信号を生成するワンショットパルス信号生成部110と、ワンショットパルス信号生成部110の出力信号を反転するインバータ113と、インバータ113の出力信号を遅延させる第1遅延回路114と、インバータ113の出力信号と、第1遅延回路114の出力信号との論理積を演算し、出力されるクロック信号のデューティを一定にする論理積回路116とを備える。

(もっと読む)

集積回路のメモリインターフェースのためのデューティサイクル補正器回路

集積回路(IC)内のデューティサイクルの歪みを補正するための回路および方法が、開示される。ICは、クロック信号を受信するように連結されるスプリッタ回路を含む。クロック信号は、2つの異なるクロック信号に分割される。クロック信号のうちの1つは、他方の反転したバージョンである。遅延回路は、クロック信号の各々に連結される。遅延回路の各々は、対応するクロック信号の遅延したバージョンを発生させる。補正器回路は、クロック信号の遅延したバージョンの両方を受信するように連結される。補正器回路は、補正されたデューティサイクルを有するクロック出力信号を発生させる。  (もっと読む)

(もっと読む)

パルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置

【課題】 駆動中の論理ゲートを減らして消費電力を少なくし、クロックが通る論理ゲート数を減らしてクロック遅延を短くしたパルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置を提供する。

【解決手段】 パルスエッジ選択回路が、複数のクロックから1つのクロックを選択して通過させる入力段と、前記1つのクロックをエッジ検出回路に出力する出力段とを有し、クロックの立ち下がりエッジを検出して、第1のクロックの立ち下がりエッジで立ち上がり、第2のクロックの立ち下がりエッジで立ち下がるパルスを生成するエッジ検出回路の場合に、前記出力段は、複数の入力端を有する複数のNORゲート及び複数の入力端を有する複数のNANDゲートを交互に組み合わせて接続されており、前記第1及び第2のクロックを出力する出力ゲートにはNORゲートが使用される。立ち上がりエッジでパルスを生成する場合、出力ゲートにはNANDゲートが使用される。

(もっと読む)

パルス幅変調回路及びそれを用いたスイッチングアンプ

【課題】 温度係数によって直流バイアス電流Icおよび放電電流Idの電流値が変動する場合であっても、入力信号に正確に対応するパルス幅変調信号を出力する。

【解決手段】 電流生成回路14は、定電流I1を生成する定電流回路31と、定電流I1の1/2の電流値である電流I2と交流電圧esを電流に変換した電流Δiとを加算した電流I2+Δiを生成する差動回路32と、定電流I1を電圧Vb2に変換する電流電圧変換手段33と、電流電圧変換手段33から供給された電圧Vb2を電流に変換し、放電電流Idを生成する電圧電流変換手段34と、電流I2+Δiを電圧Vb1に変換する電流電圧変換手段35と、電流電圧変換手段35から供給された電圧Vb1を電流に変換し、充電電流Ic+Δiを生成する電圧電流変換手段36とを備える。

(もっと読む)

予め定められたデューティサイクル信号発生器

予め定められたデューティサイクルを有する信号を発生させる技術である。例示的な実施形態では、第1のカウンタは、発振器信号のサイクルの第1の数をカウントするように構成されており、第2のカウンタは、発振器信号のサイクルの第2の数をカウントするように構成されており、第2の数は第1の数よりも大きい。第2のカウンタの出力は、第1および第2のカウンタをリセットするために使用されるが、第1および第2のカウンタの出力は、さらに、予め定められたデューティサイクルを有する信号を発生させるトグルラッチを駆動する。さらなる態様は、第2の数に対する奇数値と偶数値とを対応する技術を含む。 (もっと読む)

信号伝送装置及び信号伝送方法

【課題】簡易な回路構成で信号のパルス幅やデューティ比を一定に保つことができるよう

にする。

【解決手段】エッジ抽出回路1は、入力パルス信号Dinの立ち上がりエッジ及び立ち下り

エッジを抽出し、抽出した立ち上がりエッジ及び立ち下りエッジを正パルス信号又は負パ

ルス信号のいずれかに統一したパルス信号n2を生成する。これにより、信号伝送回路2

における入力パルス信号Dinの立ち上がりの遅延と立ち下りの遅延による変動を入力パル

ス信号Dinの立ち上がり又は立ち下りで同じ条件にできる。従って、信号伝送回路2にお

ける入力パルス信号Dinの立ち上がりと立ち下がりにおける伝播遅延時間差が生じない。

信号伝送回路2は、エッジ抽出回路1により生成されたパルス信号n2を伝送する。波形

再生回路3は、信号伝送回路2により伝送されたパルス信号n2から波形を再生して出力

パルス信号Doutを得る。

(もっと読む)

遅延回路

【課題】遅延時間が電源電圧に依存せず、入力信号がローからハイになる時とハイからローになる時との遅延時間が等しい遅延回路を提供する。

【解決手段】容量17の電圧(内部電圧Va)が接地電圧VSSから定電流インバータ19の反転閾値電圧(NMOS16の閾値電圧Vtn)よりも高い電圧になるまでの時間が遅延時間になるので、遅延時間は接地電圧VSSを基準にして決まる。また、内部遅延回路20でも同様である。入力信号Vinがハイになると、遅延回路は内部遅延回路10による遅延時間を使用し、入力信号Vinがローになると、遅延回路は内部遅延回路20による遅延時間を使用し、これらの内部遅延回路10及び内部遅延回路20は同一である。

(もっと読む)

遅延制御方法および遅延装置

【課題】遅延装置の回路規模を抑制する。

【解決手段】DLL回路120は、遅延素子122に入力された基準クロックが遅延素子122により1周期分遅延されるように遅延素子122を制御する第1の制御信号CTR1を生成する。遅延素子140は、遅延素子122と同一の構成を有し、外部からのストローブ信号S1を、第2の制御信号CTR2に応じた遅延量の分だけ遅延させる。ストローブ遅延制御回路130は、第1の制御信号CTR1と、遅延素子140による遅延量の期待値とから、遅延素子140に出力する第2の制御信号CTR2を生成する。クロック供給回路110は、遅延素子140に入力されるストローブ信号S1の周波数より高い周波数を有する基準クロックをDLL回路に供する。

(もっと読む)

遅延回路

【課題】 定電流源10が出力する定電流をFET11、12で構成されるカレントミラー回路に入力し、このカレントミラー回路の出力でコンデンサ14を放電して、このコンデンサの電圧と基準電圧Vthをコンパレータ15で比較して信号を遅延させる構成の遅延回路では、定電流源10とカレントミラー回路間の配線13にノイズが重畳するとカレントミラー回路の出力電流が変化し、遅延時間が変動してしまうという課題を解決する。

【解決手段】 FET11、12のゲート間にスイッチ30を挿入し、FET12のゲート電圧を保持するコンデンサ31をFET12のゲートに接続した。遅延発生時にスイッチ30をオフにし、FET12のゲート電圧をコンデンサ31から供給する。配線13にノイズが重畳してもカレントミラー回路の出力電流Ibは変化しないので、遅延時間がばらつくことがなくなる。

(もっと読む)

低電力非同期カウンタ及び方法

【解決手段】低電力非同期カウンタの設計技術。典型的な実施形態では、複数のフリップフロップのクロック入力及び信号出力が、非同期カウント構造を実現するように直列に連結される。複数のフリップフロップの信号出力は、参照信号の順次遅延されたバージョンによってサンプリングされる。更に、参照信号の順次遅延されたバージョンを生成する設計方法が開示される。典型的な実施形態では、非同期カウント技術は、デジタル位相ロックループ(DPLL)の高速カウンタに使用され得る。 (もっと読む)

DLL回路及びその制御方法

【課題】クロックのパルス幅が狭い場合、及び広い場合において、合成回路の誤動作を回避し、動作周波数の高速化に対応可能とするDLLの提供。

【解決手段】外部クロック(CK)の第1遷移(Rise)に対応して互いに異なる遅延時間の信号を出力し、CKの第2の遷移(Fall)に対応して互いに異なる遅延時間の信号を出力する第1の可変遅延回路20と、第1の可変遅延回路からの信号をそれぞれ受ける第2の可変遅延回路10R、10Fからの出力信号を合成して出力する第1の合成回路30とを備え、第2の可変遅延回路は第1の可変遅延回路からの信号からワンショットパルスを生成するワンショットパルス生成回路と、リセット端子を備えるラッチ回路と、ラッチ回路のセット出力の遷移エッジを受け、所定の比率で合成した信号を出力する第2の合成回路と、を備え、第2の合成回路の出力がラッチ回路のリセット端子に入力される。

(もっと読む)

遅延回路

【課題】リセット動作に要する時間を短縮でき、リセット動作時に発生する雑音を抑制し、高速な繰り返しの入力信号に対応でき、高集積化、低消費電力化できるランプ波形発生方式の遅延回路を提供する。

【解決手段】ランプ波形を発生する遅延発生容量と、一端が第1の初期電圧源に接続され他端が遅延発生容量の他端に接続の第1のスイッチと、一端が第2の初期電圧源に接続され他端が遅延発生容量の他端に接続の第2のスイッチと、一端がチャージ電流源に接続され他端が遅延発生容量の他端に接続の第3のスイッチと、一端がディスチャージ電流源に接続され他端が遅延発生容量の他端に接続の第4のスイッチと、第1のコンパレータと、入力に第1のコンパレータの出力が接続される第1のワンショットと、第2のコンパレータと、入力に第2のコンパレータの出力が接続される第2のワンショットと、遅延出力信号を出力する論理和ゲートとを備える。

(もっと読む)

PWM制御装置及びパルス波形制御方法

【課題】従来のPWM制御装置では、パルス幅変調信号の周期を一定に保ちながら高い分解能でデューティー比を制御できない問題があった。

【解決手段】本発明のPWM制御装置は、基準クロック信号REFCをカウントして第1のカウント値CNT1を出力する第1のカウンタ40と、第1のカウント値CNT1に基づき前縁制御信号FCNTLを出力する前縁制御信号生成部41と、調整用クロック信号ADJCを生成する調整用クロック生成部30bと、第1のカウント値CNT1に基づき調整用クロック信号ADJCの出力開始を指示する第2のカウンタ制御部20と、第2のカウント値CNT2を出力する第2のカウンタ50と、第2のカウント値CNT2に基づき後縁制御信号ECNTLを出力する後縁制御信号生成部51と、前縁制御信号FCNTL及び前記後縁制御信号ECNTLを合成してパルス幅変調信号を生成するPWMパルス生成部60と、を有する。

(もっと読む)

1 - 20 / 48

[ Back to top ]