Fターム[5J001BB05]の内容

Fターム[5J001BB05]に分類される特許

1 - 20 / 152

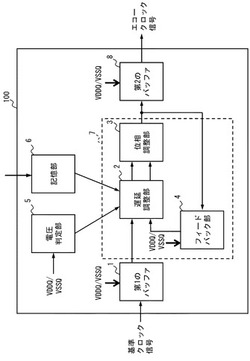

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

タイミング調整回路

【課題】本発明は、モジュール、パッケージ、回路の何れかの間で引き渡される複数の信号に、これらの信号の引き渡しに供される伝搬路の遅延時間の差やその遅延時間の偏差に適した形態でタイミングの調整を施すタイミング調整回路に関し、伝搬路の配置、経路および特性と、環境条件および経年とに対して柔軟に適応可能とすることを目的とする。

【解決手段】第一の伝搬路を介して与えられるパルス信号に順次遅延を与え、複数Nの遅延信号を生成する遅延手段と、前記第一の伝搬路と異なる第二の伝搬路を介して与えられる信号に同期して前記複数Nの遅延信号の瞬時値をラッチングし、前記複数Nの遅延信号の瞬時値の時系列上における前縁または後縁を識別する変化点識別手段と、前記複数Nの遅延信号の内、前記前縁もしくは後縁または前記前縁もしくは後縁に最も近い時点に前記時系列上で対応する遅延信号を選択する選択手段とを備える。

(もっと読む)

半導体装置及びデータ処理システム

【課題】外部電圧VDDの変動に伴うレイテンシカウンタのラッチマージンの低下を抑制する。

【解決手段】半導体装置は、外部クロック信号に基づいて生成される内部クロック信号LCLKOEFTと、外部から供給されるリードコマンドに応じて生成される内部リードコマンドMDRDTとを受け、内部リードコマンドDRCを生成するレイテンシカウンタ55を備え、レイテンシカウンタ55は、出力ゲート信号COT0〜COT7のそれぞれを遅延させることにより入力ゲート信号CIT0〜CIT7を生成する遅延回路部200を有し、遅延回路部200は、外部電圧VDDで動作する遅延素子と、内部電圧VPERIで動作する遅延素子とを含む。

(もっと読む)

遅延ロックループ回路及びロックアップ方法

【課題】レイアウト面積の増加を抑えつつロックアップ時間の高速化を実現する。

【解決手段】本発明に係る遅延ロックループ回路1は、遅延ライン3と、初期遅延モニタリング部4と、位相比較部5と、遅延制御部6と、ファイン遅延部7とを備え、初期遅延モニタリング部4は、基準クロックと複数の単位遅延部のうちの一部の単位遅延部が出力する単位遅延クロックとの位相を比較する複数の位相比較用フリップフロップを備え、これら位相比較用フリップフロップの数を単位として当該比較を段階的に繰り返すことにより、全範囲について初期遅延モニタリングを行うものである。

(もっと読む)

遅延回路およびシステム

【課題】 遅延段の数を切り換えるときの遅延時間の増加量および減少量を一定にすることで、高い精度を有する遅延回路を形成する。

【解決手段】 遅延回路は、直列に接続された複数の遅延段、検出回路および調整回路を有する。各遅延段は、前段からの信号を反転して後段に伝達する第1遅延素子と、後段からの信号を反転して前段に伝達し、または前段からの信号を反転した遅延信号を反転して前段に伝達する第2遅延素子とを含む。検出回路は、奇数段目および偶数段目の遅延段において、前段からの信号を受けてから遅延信号を経て第2遅延素子から信号が出力されるまでの伝搬遅延時間をそれぞれ検出する。調整回路は、検出回路の検出結果に基づいて、奇数段目および偶数段目の遅延段の伝搬遅延時間を互いに等しくする。

(もっと読む)

サンプリングクロック生成回路、画像読取装置及び電子機器

【課題】アパーチャディレイをより小さくするアパーチャディレイ調整機能を有するサンプリングクロック生成回路を提供する。

【解決手段】SSCG11からの出力クロック信号に対して所定の遅延量だけ遅延してサンプリングクロック信号を発生してサンプリングホールド回路に供給する、遅延回路21,22及びクロック発生器23からなるサンプリングクロック生成手段と、SSCG11の出力クロック信号に基づいて生成されたCCD駆動クロック信号と、上記サンプリングクロック信号とを位相比較して位相比較結果を出力する遅延型フリップフロップ24と、上記位相比較結果に基づいて、上記駆動クロック信号と上記サンプリングクロック信号との位相差が実質的にゼロとなるように上記サンプリングクロック生成手段の遅延量を制御する制御ロジック回路20とを備えた。

(もっと読む)

半導体集積回路

【課題】 原振クロック信号を通過させる場合の遅延時間と分周クロックを生成する場合の遅延時間を等しくするために、遅延時間の算出や遅延回路の調整を行う必要がない半導体集積回路を提供する。

【解決手段】 外部制御信号SEの論理値に基づいて、クロック信号CLKと外部入力信号SDの何れか一方を選択して内部入力信号S0とし、クロック信号CLKの立ち下がりで内部入力信号S0をラッチして第1内部出力信号S1を生成し、クロック信号CLKの立ち上がりで内部入力信号S0をラッチして第2内部出力信号S2を生成し、クロック信号CLKまたはクロック信号CLKの遅延信号を内部制御信号S3とし、内部制御信号S3の論理値に基づいて、第1内部出力信号S1または第2内部出力信号S2の何れか一方を選択出力し、選択された一方の内部出力信号は、当該選択期間中は信号レベルが変化しない。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

TDC装置とTDCのキャリブレーション方法

【課題】遅延素子の遅延時間のばらつきに対してTDCの変換特性を一定とし線形性を実現可能なTDCの提供。

【解決手段】第1の信号DATAを順次遅延させる複数段の遅延素子111〜11Nを有するディレイライン10と、第2の信号CLKに応答して複数段の遅延素子の出力をサンプルする複数のフリップフロップ121〜12Nと、相隣るフリップフロップの出力結果が切り替わるエッジ位置を、第1の信号の第2の信号に対する位相差として検出するエッジ検出器13と、を備え、エッジ位置の検出結果に基づき、バイアス制御用の制御コードICNTを生成するキャリブレーション制御回路15と、制御コードに対応する複数段の遅延素子に対して供給するバイアス発生回路14を備え、第1の信号の周波数範囲に対応した段数の遅延素子に、第1の信号のエッジが位置するように遅延素子111〜11Nの遅延時間の校正を行う。

(もっと読む)

内部クロック周波数制御回路及びこれを利用する半導体装置

【課題】半導体装置の外部から入力されるコマンド(命令)及びアドレスのセットアップ/ホールドマージンを増加させることができる内部クロック周波数制御回路及びこれを利用する半導体装置を提供する。

【解決手段】本発明は、モードレジスタセット制御信号を受信してモードレジスタセット信号を出力するモードレジスタセットと、モードレジスタセット信号がイネーブルされて外部クロックと同一の周波数のデータ処理用クロックの予め設定された周期が経過するとイネーブル信号を生成する遅延部と、イネーブル信号がイネーブルされると外部から入力される同期命令をデコーディングして分周開始信号を生成する分周命令デコーダと、分周開始信号に応答して外部クロックと同一の周波数の選択クロックを出力するか、または、外部クロックより周波数が低いクロックを選択クロックとして出力する分周選択部とを含む。

(もっと読む)

半導体装置

【課題】再開トリガ信号を生成できないことによってリードデータの出力タイミングと外部クロック信号の同期が外れてしまうことを防止する。

【解決手段】DLL回路100には、当該DLL回路100を初期起動させるリセット信号RESETと、内部クロック信号LCLKの内部クロック信号ICLKに対する遅延量の制御を当該DLL回路100に再開させる再開トリガ信号RESTARTとが入力され、DLL回路100は、リセット信号RESET又は再開トリガ信号RESTARTが活性化されたことに応じて遅延量の制御を開始し、リセット信RESET号が活性化された後再開トリガ信号RESTARTが活性化される前には、当該DLL回路100のロック後にも遅延量の制御を継続し、再開トリガ信号RESTARTが活性化された後には、当該DLL回路100のロックに応じて遅延量の制御を停止する。

(もっと読む)

パルス幅制御回路及び半導体メモリ

【課題】トランジスタのプロセス依存と配線幅のばらつきとに応じて適切なパルス幅に制御することが可能なパルス幅制御回路及び半導体メモリを提供すること。

【解決手段】配線による遅延とインバータによる遅延とを比較する比較回路と、インバータ段数によりパルス幅を調整するパルス幅調整回路と、を備える。パルス幅調整回路は、比較回路の比較結果に基づいて、インバータによる遅延が配線による遅延よりも小さくなった場合に、インバータ段数を多くし、パルス幅を増加させる。

(もっと読む)

可変遅延回路、記録装置、遅延量校正方法

【課題】ディレイラインについての遅延量校正のために校正用ディレイラインを不要とし、また校正のバラツキをなくす。

【解決手段】入力信号(エッジパルス)を遅延させるディレイラインに対し、例えば9T区間などの校正期間に、例えば1T時間分などの単位遅延量を設定する。そして入力信号にテストパルスを重畳させ、また該テストパルスに対して単位遅延量を持つ比較用パルスを発生させる。そして比較用パルスと、ディレイラインを経て単位遅延量が与えられたテストパルスとの位相比較を行い、単位遅延量に相当する単位遅延制御値を判定する。この判定した単位遅延制御値を校正結果の単位遅延制御値として、以後のディレイラインの遅延量の設定に用いる。

(もっと読む)

半導体装置

【課題】電源ノイズの影響を受けにくい高精度な可変遅延回路を有する半導体装置を提供する。

【解決手段】其々が直列に接続された差動型の複数の第1の遅延素子、複数の第1の遅延素子間に其々設けられた複数の第1の接点、及び第1の選択信号を受けて複数の第1の接点のうち選択された第1の接点に対応する第1の遅延信号を出力する第1の出力回路、を備えた第1の遅延部並びに、第1の遅延信号を受け、其々が直列に接続されたシングルエンド型の複数の第2の遅延素子、第2の遅延素子間に其々設けられた複数の第2の接点、及び第2の選択信号を受けて複数の第2の接点のうち選択された第2の接点に対応する第2の遅延信号を出力する第2の出力回路、を備えた第2の遅延部を含む遅延回路と、第1及び第2の選択信号を其々出力する制御回路と、を備える。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路の外部に接続される半導体チップのプロセス状態を検出して、マスク解除信号に対する制御信号のセットアップ時間またはホールド時間のマージンを大きくする。

【解決手段】 モニタモード中に、通常より低い参照電位を受信回路に供給して伝送信号の論理レベルを判定することで、半導体集積回路の外部に接続される半導体チップのプロセス状態を検出する。検出したプロセス状態に応じて可変遅延回路を制御し、内部同期信号および外部同期信号の少なくともいずれかの遅延時間を調整する。これにより、内部同期信号に応じて生成されるマスク解除信号に対する半導体チップからの制御信号のセットアップ時間またはホールド時間を、半導体チップのプロセス状態に拘わらず一定にできる。

(もっと読む)

クロックデューティ補正回路

【課題】出力されるクロック信号が発振することなく、デューティが一定になるようにクロック信号を補正することが可能なクロックデューティ補正回路を提供する。

【解決手段】クロックデューティ補正回路100は、クロック信号発生部から出力されたクロック信号が入力され、当該クロック信号の波形の立ち上がりに合わせて波形が立ち上がり、信号の周期が一定となるワンショットパルス信号を生成するワンショットパルス信号生成部110と、ワンショットパルス信号生成部110の出力信号を反転するインバータ113と、インバータ113の出力信号を遅延させる第1遅延回路114と、インバータ113の出力信号と、第1遅延回路114の出力信号との論理積を演算し、出力されるクロック信号のデューティを一定にする論理積回路116とを備える。

(もっと読む)

発振異常検出回路

【課題】発振回路の発振周波数の異常を検出することができる発振異常検出回路を提供することである。

【解決手段】クロック信号CLKを、直列接続された複数の遅延素子20〜25を用いて遅延させる遅延部2と、遅延素子20〜25の出力信号であるクロック信号CLK0〜CLK5から、全体遅延時間tda内における、クロック信号CLKの変化を示す発振信号パターンD0〜D5を取得する信号パターン取得部3と、期待信号パターンE0〜E5を予め記憶する期待値記憶部4と、発振信号パターンD0〜D5と期待信号パターンE0〜E5とを比較する比較部5と、比較部5による比較結果が一致しない場合、発振回路100に発振異常が生じていると判定する異常判定部6とを備えた。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

1 - 20 / 152

[ Back to top ]