Fターム[5J001BB11]の内容

Fターム[5J001BB11]に分類される特許

1 - 20 / 71

パルス幅調整回路および方法

パルス幅延長回路および方法

セル・ライブラリから選択された信号スキュー調整セルを備えた集積回路

【課題】 少なくとも1つのデジタル論理セルおよび少なくとも1つのスキュー調整セルを有するデジタル回路機構を備えた集積回路を提供すること。

【解決手段】 スキュー調整セルは、集積回路のデジタル回路機構における信号のスキューを所望の量に調整するように構成される。デジタル論理セルおよびスキュー調整セルはセル・ライブラリから選択される。

(もっと読む)

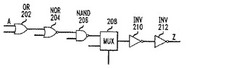

可変遅延回路

【課題】1段ごとの遅延時間変化の誤差が小さい高精度の可変遅延回路の実現。

【解決手段】直列に接続された複数個の遅延ユニット20-0,20-iを有し、各遅延ユニットは、第1から第3論理ゲートを有し、第1論理ゲートG1は、前段の出力が後段の一方の入力になるように直列に接続され、他方の入力には、折り返し位置を指示する第1制御データCTN0,CTNiが入力され、第2論理ゲートG2は、一方の入力が第1論理ゲートの入力に接続され、他方の入力には折り返し位置を指示する第2制御データCT0,CTiが入力され、第3論理ゲートSGは、後段の出力が前段の一方の入力になるように直列に接続され、他方の入力には第2論理ゲートの出力が入力され、第3論理ゲートにおいて、一方の入力M1から出力Zまでの経路の遅延時間と、他方の入力M2から前出力Zまでの経路の遅延時間は、等しい可変遅延回路。

(もっと読む)

クロックデューティ補正回路

【課題】出力されるクロック信号が発振することなく、デューティが一定になるようにクロック信号を補正することが可能なクロックデューティ補正回路を提供する。

【解決手段】クロックデューティ補正回路100は、クロック信号が入力され、入力されたクロック信号の波形の立ち上がりに合わせて波形が立ち上がりパルス幅が一定の幅であるワンショットパルス信号を生成するワンショットパルス信号生成部110と、ワンショットパルス信号生成部110の出力が一方の入力側に入力される否定論理和回路120と、否定論理和回路120の出力信号を遅延させる第1遅延回路130を有し、第1遅延回路130により遅延された否定論理和回路120の出力を否定論理和回路120の他方の入力側にフィードバックする帰還回路140と、否定論理和回路120の出力信号が入力される第2ローパスフィルタ150と、を備える。

(もっと読む)

信号整形装置

【課題】高いクロック周波数に対応した高速動作が可能であると共に、高い精度でデューティ比を調節できる信号整形装置を提供すること。

【解決手段】所定パルス幅のパルス信号を生成するパルス信号生成部11と、パルス信号のデューティ比を制御するデューティ比調節部12と、を有する信号整形装置であり、パルス信号生成部11は、クロック信号が入力されるフリップフロップ回路101と、フリップフロップ回路101の出力信号を遅延させて当該遅延量に応じたパルス幅を有する単相のパルス信号を出力する遅延回路102と、を備え、デューティ比調節部12は、遅延回路102から出力される単相のパルス信号を互いに極性が反転した第1パルス信号と第2パルス信号からなる差動パルス信号に変換し、第1パルス信号の平均電圧と第2パルス信号の平均電圧との差に基づいて、パルス信号が目標のデューティ比になるように遅延回路102の遅延量を制御する。

(もっと読む)

遅延回路

【課題】温度や電圧の変動によって遅延回路に生じる遅延時間をキャンセルする。

【解決手段】Nチャンネル型の第1トランジスタ及びPチャンネル型の第2トランジスタが直列接続されてなる複数のインバータINVo,INVeが交互に接続された遅延回路であって、電源配線VDDとインバータINVeの入力ノードinとの間に接続されたPチャンネル型の第3トランジスタを備える。本発明によれば、温度や電圧などの変動が生じた場合であっても、第3トランジスタの存在により、複数のインバータにそれぞれ含まれる第2トランジスタの特性変動が相殺される。これにより、温度や電圧などの変動が生じた場合、遅延回路全体の遅延量変動は、第1トランジスタの特性変動によるものとみなすことが可能となる。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

パルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置

【課題】 駆動中の論理ゲートを減らして消費電力を少なくし、クロックが通る論理ゲート数を減らしてクロック遅延を短くしたパルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置を提供する。

【解決手段】 パルスエッジ選択回路が、複数のクロックから1つのクロックを選択して通過させる入力段と、前記1つのクロックをエッジ検出回路に出力する出力段とを有し、クロックの立ち下がりエッジを検出して、第1のクロックの立ち下がりエッジで立ち上がり、第2のクロックの立ち下がりエッジで立ち下がるパルスを生成するエッジ検出回路の場合に、前記出力段は、複数の入力端を有する複数のNORゲート及び複数の入力端を有する複数のNANDゲートを交互に組み合わせて接続されており、前記第1及び第2のクロックを出力する出力ゲートにはNORゲートが使用される。立ち上がりエッジでパルスを生成する場合、出力ゲートにはNANDゲートが使用される。

(もっと読む)

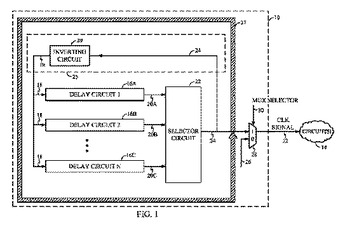

適応クロック発生器、システムおよび方法

機能回路のための、性能マージンを回避し、あるいは小さくするためのクロック信号を生成するために使用することができる適応クロック発生器、システムおよび関連する方法が開示される。特定の実施形態では、クロック発生器は、機能回路内の選択された遅延経路に関連する遅延回路に提供された遅延経路に従って、自律的に、かつ、適合的にクロック信号を生成する。クロック発生器には、入力信号を受け取るように適合され、かつ、出力信号を生成するために、受け取った入力信号を機能回路の遅延経路に関連する量だけ遅延させるように適合された遅延回路が含まれている。遅延回路には、上記出力信号に応答する帰還回路が結合されており、この帰還回路は、遅延回路に発振ループ構成で戻すための入力信号を生成するように適合されている。入力信号を使用して機能回路にクロック信号を提供することができる。  (もっと読む)

(もっと読む)

半導体装置、および該半導体装置における遅延回路の遅延コード自動設定方法

【課題】入力されるデータ信号のセットアップ及びホールド時間を調整する遅延回路における最適な遅延時間(遅延コード)を、半導体装置の実際の動作条件下において自動的に設定する。

【解決手段】パッド11から、ターゲットとなるデータ信号ADD/CMDを遅延回路13に入力し、遅延回路13の遅延コードCODET<2:0>を変えて、遅延回路から出力される遅延信号の遅延時間を変化させる。そして、この遅延された信号をラッチ回路14によりラッチし、遅延された信号PA0DBとラッチされたデータ信号PA2Bとの一致または不一致を判定し、一致すると判定した場合に、この判定結果に基いて遅延コードCODET<2:0>を決定し、決定後の遅延コードにより遅延回路13を動作させる。

(もっと読む)

遅延回路及び遅延回路を備えた半導体記憶装置

【課題】トランジスタ特性のバラツキに応じて遅延回路の遅延特性を設定することを特徴とする。

【解決手段】定電流源12と、ゲートとドレインが結合され、定電流源の電流が流れるMOSトランジスタ14とを含み、MOSトランジスタ14のゲートのノードからバイアス電圧を出力するバイアス回路部10と、インバータ26と、電流通路がインバータの入力ノードと基準電位ノードとの間に直列に挿入され、バイアス電圧がゲートに供給されるMOSトランジスタ21及び入力信号INがゲートに供給されるMOSトランジスタ22と、インバータの入力ノードと基準電位のノードとの間に挿入された容量25と、電流通路が電源電位ノードとインバータの入力ノードとの間に挿入され、入力信号がゲートに供給されるMOSトランジスタ23とを含み、インバータの出力ノードから信号を出力する遅延部20とを具備している。

(もっと読む)

半導体集積回路

【課題】論理ゲートを構成するトランジスタの特性劣化を抑制する。

【解決手段】半導体集積回路70には、マルチプレクサ1、信号発生回路2、制御回路3、m個のインバータINV1乃至m列、n個の2入力NOR回路NOR1乃至n、縦続接続されるn個の2シフトレジスタSR1乃至nが設けられる。制御回路3は、クロック信号が供給される通常動作ときにディセーブル状態の制御信号Sctを生成し、クロック信号が供給されない通常動作以外のときにイネーブル状態の制御信号Sctを生成する。マルチプレクサ1は、クロック信号Sclkと信号発生器2から出力される低周波信号Ssgが入力され、制御信号Sctがディセーブル状態の時インバータINV1乃至m列にクロック信号Sclkを供給し、制御信号Sctがイネーブル状態の時インバータINV1乃至m列に低周波信号Ssgを供給する。

(もっと読む)

位相補償用クロック同期回路

【課題】短時間で精度よく位相調整を行うことが可能な位相補償用クロック同期回路を提供する。

【解決手段】DLLは、入力レシーバ1と、遅延チェーン回路2と、遅延複製器4と、位相比較器5と、リセットパルス発生器6と、粗調整期間発生器7と、分周器8と、単位可変カウンタ9と、を備えている。まず単位可変カウンタ9の増減単位を17または1(平均で16)として粗調整を行って粗くロックさせた後に、単位可変カウンタ9の増減単位を1として微調整を行って細かくロックさせるため、短い期間で確実にクロックINTCKXとクロックEXTCKXの位相を合わせることができる。

(もっと読む)

遅延ロックループのための初期化回路

【課題】遅延ロックループのための起動回路を提供する。

【解決手段】遅延ロックループにおける初期化回路は、電源投入または他のリセットの後、クロック端縁が適切な動作のために適切な順序で位相検出器によって受取られることを確実にし、遅延ロックループのリセット後、初期化回路は、遅延線における遅延を増加(または減少)させるように位相検出器をイネーブルするより先に基準クロックの少なくとも1つの端縁が受取られることを確実にし、フィードバッククロックの少なくとも1つの端縁が受取られた後、初期化回路は位相検出器をイネーブルして、遅延線における遅延を減少(または増加)させる。

(もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

半導体集積回路

【課題】主電源とバックアップ電源とを切り換える切換回路を内蔵しないリアルタイムクロック用の半導体集積回路において、バックアップモードにおける消費電力を低減する。

【解決手段】この半導体集積回路は、外部の主電源による第1の電源電圧又は外部のバックアップ電源による第2の電源電圧が選択的に供給されて動作する半導体集積回路であって、第1又は第2の電源電圧に基づいて第3の電源電圧を生成する定電圧回路と、第3の電源電圧が供給されて原振クロック信号を生成する発振回路と、原振クロック信号を分周し、分周されたクロック信号に基づいて計時情報を管理するロジック回路と、第1の電源電圧が供給されているか否かを表す信号に従って、第1の電源電圧が供給されていないときに、定電圧回路から出力される第3の電源電圧の値又は定電圧回路の動作期間を減少させる制御回路とを具備する。

(もっと読む)

DLL回路及びその制御方法

【課題】冗長な回路、配線を不要とし、回路規模の増大を回避し、デューティを変更可能とするDLLを提供する。

【解決手段】外部信号の第1遷移(Rise)を可変に遅延させる第1可変遅延回路(10R)と、外部信号の第2遷移(Fall)を可変に遅延する第2可変遅延回路(10F)と、第1可変遅延回路(10R)の出力信号と第2可変遅延回路(10F)の出力信号とを合成する合成回路(13)と、合成回路(13)の出力信号のデューティの変更と検出を行うデューティ変更検出回路(21)と、デューティ変更検出回路(21)のデューティ検出結果(DCC)に従って第1可変遅延回路(10R)又は第2可変遅延回路(10F)の遅延を可変させる遅延制御回路(15R、15F)と、を備える。

(もっと読む)

デューティ可変回路

【課題】低電力、小面積で実現するデューティ可変回路を提供する。

【解決手段】それぞれ一対の相補型のトランジスタを有する第1のCMOSインバータ回路と、第2のCMOSインバータ回路と、前記第1のCMOSインバータ回路と第2のCMOSインバータ回路の間に直列接続され、ゲートがグランドに接続されたPMOSトランジスタと、前記第2のCMOSインバータ回路に接続された第3のインバータ回路と、前記第2のCMOSインバータ回路への電源及びグランドの供給がそれぞれ制御できる第1及び第2のスイッチを有する。前記第3のインバータ回路の出力信号を用いて前記第1、第2のスイッチの開閉を切り替えることによって、前記第2のCMOSインバータ回路の入力信号の論理が遷移する際の前記第2のCMOSインバータ回路の貫通電流を低減する。

(もっと読む)

クロックシフト用遅延ライン回路

【課題】クロックの周波数が高周波の場合でも、遅延時間の変更時に、出力されるクロックにグリッチを発生させることがないクロックシフト用遅延ライン回路を提供する。

【解決手段】直列に接続されたインバータ−マルチプレクサ型の複数の遅延セルが、所定数の遅延セルを含む複数の遅延ブロックに分割され、折り返し場所の遅延セルを切り替えて、クロックを、折り返し場所の遅延セルに対応する時間遅延する遅延ライン部と、クロックの折り返し場所の遅延セルが、どの遅延ブロックに含まれているのかを検出する第1の検出部と、各々の遅延ブロックから出力される遅延信号およびクロックに応じて、クロックが、どの遅延ブロックまで伝搬しているのかを検出する第2の検出部と、第1および第2の検出部により検出された遅延ブロックが一致するか否かを検出する第3の検出部とを備えている。遅延ライン回路では、第3の検出部により一致が検出された場合に折り返し場所の遅延セルを切り替える。

(もっと読む)

1 - 20 / 71

[ Back to top ]