Fターム[5J001BB22]の内容

Fターム[5J001BB22]に分類される特許

1 - 14 / 14

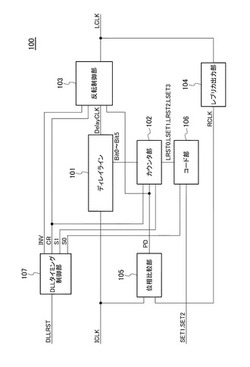

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

可変遅延回路、記録装置、遅延量校正方法

【課題】ディレイラインについての遅延量校正のために校正用ディレイラインを不要とし、また校正のバラツキをなくす。

【解決手段】入力信号(エッジパルス)を遅延させるディレイラインに対し、例えば9T区間などの校正期間に、例えば1T時間分などの単位遅延量を設定する。そして入力信号にテストパルスを重畳させ、また該テストパルスに対して単位遅延量を持つ比較用パルスを発生させる。そして比較用パルスと、ディレイラインを経て単位遅延量が与えられたテストパルスとの位相比較を行い、単位遅延量に相当する単位遅延制御値を判定する。この判定した単位遅延制御値を校正結果の単位遅延制御値として、以後のディレイラインの遅延量の設定に用いる。

(もっと読む)

半導体装置及び遅延量調整方法

【課題】クロック信号の位相を遅延させる遅延回路とその遅延量を調整する回路とを備えた半導体装置において遅延量がクロック信号の周期的なジッタの影響を受けないようにする半導体装置及び遅延量調整方法を提供する。

【解決手段】第1のクロック信号を遅延させた第2のクロック信号を出力する可変遅延回路と、可変遅延回路における遅延量を制御する制御信号を出力する遅延量調整回路と、遅延量調整回路が制御信号を更新するタイミングを決定するタイミング信号を出力するタイミング信号発生回路と、を備えた半導体装置であって、タイミング信号発生回路は連続してタイミング信号を出力するものであって、互いに隣接するタイミング信号の間隔の内、少なくとも2つの間隔が互いに異なる。

(もっと読む)

半導体装置

【課題】装置の使用中にタイミングマージンを最適化可能な半導体装置を提供する。

【解決手段】入力クロック信号の位相の遅延角度と遅延素子の段数との関係を示す遅延素子段数信号を出力するマスタDLL回路101と、遅延素子段数信号に基づいて、位相制御信号を生成する位相制御回路102と、位相制御信号に基づいて、クロック信号の位相を所定角度分シフトさせたクロック信号を出力するスレーブDLL回路103と、スレーブDLL回路から出力されたクロック信号に同期したデータ信号を生成するデータ信号生成回路111と、遅延素子段数信号、又はマスタDLL回路のロックアップ時間を示すロックアップ時間信号に基づいて、データ信号のスルーレートを制御するための制御信号を生成するスルーレート制御回路121と、スルーレート制御信号に基づいて、データ信号のスルーレートを制御するデータ信号出力回路112とを備える。

(もっと読む)

チャネル間遅延補正回路及びそれに用いるチャネル間遅延補正方法

【課題】 BER特性等の性能を向上させることが可能なチャネル間遅延補正回路を提供する。

【解決手段】 チャネル間遅延補正回路は、各々異なる第1及び第2の入力信号をアナログ/ディジタル変換する第1及び第2の変換回路(A/D変換器8,9)と、第1及び第2の変換回路各々の出力をそれぞれ遅延する第1及び第2の遅延回路(固定遅延回路10、可変遅延回路11)と、第1及び第2の遅延回路各々の出力を基に第1及び第2の入力信号のチャネル間の遅延時間に相当する遅延時間誤差を出力する演算回路(乗算器13)と、演算回路の演算結果を基に第1及び第2の遅延回路の一方に対して遅延時間差がなくなるように遅延量を制御する制御回路(ループフィルタ12)とを有する。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置の製造ばらつきや経年劣化に起因するクロックスキューを補正することができる半導体装置を提供する。

【解決手段】スキュー検出部6は、スキューを検出するための少なくとも1個のクリティカルパス7又はレーシングパス7を含む。クロック調整部5は、スキュー検出部6により検出されたスキューに基づいて、ディレイの設定値を設定する。クロックセル4は、ディレイの設定値に応じて、第1のクロックのディレイを調整して、第2のクロックとして出力する。

(もっと読む)

フリップフロップ回路

【課題】不感帯が少なく高速安定動作が可能なフリップフロップ回路を提供すること。

【解決手段】本発明は、データ信号Dと、立ち上がり遅延クロック信号CKdとを入力し、データ信号Dの立ち下がりと立ち上がり遅延クロック信号CKdの立ち下がりとによって内部ノードNCの信号を立ち上げる第1のラッチ回路L1と、内部ノードNCの信号とクロック信号CKとを入力し、内部ノードNCの信号が立ち上がっている状態でクロック信号CKが立ち下がるタイミングにより内部ノードXの信号を立ち下げる第2のラッチ回路L2と、内部ノードXの信号とクロック信号CKとを入力し、クロック信号CKが立ち上がっている状態でのデータ信号Dを保持する出力信号を生成するための第3のラッチ回路L3と、内部ノードNCの信号を立ち上がり遅延クロック信号CKdによってプルダウンさせるプルダウン回路PDとを備えるフリップフロップ回路である。

(もっと読む)

PLL回路及びPLL回路を構成する可変ディレイラインの制御方法

【課題】 任意の幅で重なり合う発振レンジの設定を行い、PLL回路でのジッタの発生を抑制する。

【解決手段】 デジタルPLL回路10の発振制御回路2には、カウンタ制御回路11、第1のアップダウンカウンタ12、及び第2のアップダウンカウンタ13が設けられ、カウンタ制御回路11は、制御信号Scmが、ある値M=Xである状態からM=X+1である状態に変化するときに、制御信号Scnが段階的にアップカウントせずに、例えばスキップしてアップカウントが可能となる制御信号Smupと、制御信号Scmが、ある値M=X+1である状態からM=Xである状態に変化するときに、制御信号Scnが段階的にダウンカウントせずに、例えばスキップしてダウンカウントが可能となる制御信号Smdnとを入力する。このため、可変ディレイラインから出力されるディレイ信号は製造バラツキ、温度、及び電源電圧などの変動によらず任意の幅で重なり合う。

(もっと読む)

半導体装置

【課題】受信したクロックと入力信号の間に位相ずれがあっても、位相ずれをなくした状態で入力信号を取り込める半導体装置の実現。

【解決手段】受信したクロックに基づいて内部クロックを発生するクロック発生回路451と、入力信号を受ける入力バッファ回路452と、内部クロックに同期して入力信号を取り込んで出力する入力回路458とを備える半導体装置において、入力回路は、入力バッファ回路の出力を遅延させ、遅延量が選択可能なディレイ回路460と、内部クロックに同期して入力バッファ回路の出力を取り込む入力回路462と、入力回路の出力信号値を判定することにより、入力バッファ回路の出力の内部クロックに対する位相を判定する位相判定回路465と、位相判定回路の判定結果に基づいて、入力バッファ回路の出力が内部クロックに対して所定の位相になるようにディレイ回路の遅延量を制御するディレイ制御回路461とを備える。

(もっと読む)

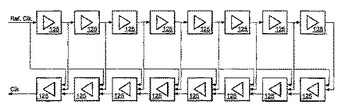

マルチプレクサ機能と補間機能とが埋め込まれた電圧制御遅延線(VCDL)

電圧制御遅延線(VCDL)である。VCDL(120)は1つ以上のセル(125)を含む。この1つ以上のセルの各々は2つ以上の入力(Va、VaX、Vb、VbX)と出力(Vout、VoutX)とを含む。この1つ以上のセルの各々は、補間機能ならびにマルチプレクサ機能に加えて、遅延をもたらすように構成されている。VCDLは、遅延ロックループ(DLL)にて遅延をもたらすように使用される。  (もっと読む)

(もっと読む)

デジタル制御型位相合成回路システム

【課題】 ジッタ耐性を強化し、かつロックレンジを拡大するデジタル制御型位相合成回路システムを得る。

【解決手段】 位相の異なる2つのクロックと制御信号が入力され、制御信号による重み付けに基づいて、これらのクロックの中間の位相をもつ出力クロックを合成する位相合成回路と、出力クロックの位相と基準クロックの位相とを比較するバイナリ型位相比較回路と、バイナリ型位相比較回路による比較結果に基づいて第1のカウント値をカウントアップ又はカウントダウンし、第1のカウント値の最上位ビットの値を出力し、第1のカウント値にキャリー又はボローが発生した場合にクロックパルスを出力する第1のアップダウンカウンタと、クロックパルスを動作クロックとし、第1のカウント値の最上位ビットに基づいて第2のカウント値をカウントアップ又はカウントダウンし、第2のカウント値を制御信号として出力する第2のアップダウンカウンタとを有する。

(もっと読む)

半導体装置の遅延調節回路、及び遅延調節方法

【課題】動作条件の変化による遅延時間を検出し、この遅延時間を一定範囲内に入るように調節可能な遅延調節回路が開示される。

【解決手段】遅延調節回路は、遅延検出回路、第1パルス発生器、カウンタ制御回路、及びnビットカウンタを備える。遅延検出回路は、出力信号に応答して入力信号を第1時間遅延させ、入力信号と遅延した入力信号とを互いに比較し、第1信号を発生させる。第1パルス発生器は、入力信号に応答して第2信号を発生させる。カウンタ制御回路は、第1信号と第2信号とに応答してカウントアップ信号とカウントダウン信号とを発生させる。nビットカウンタは、カウントアップ信号とカウントダウン信号に応答して第1時間を2n(nは自然数)区間に分けるためのデジタル出力信号を発生させる。従って、遅延調節回路は、半導体製造工程、温度、電圧などの条件が変化しても遅延時間を一定範囲内に入るように調節することができる。

(もっと読む)

クロックツリーの動的な平衡方法

【課題】 より多い電流を発生して、クロックがより遅くなるある沈みの時間遅延を補償することができるクロックツリーの動的な平衡方法を提供する。

【解決手段】クロックツリー回路において、制御可能なバッファを前記クロックツリー回路の特定なレベルに差込み、且つ何れか二つの位相の異なるクロックを接収する制御器を提供し、前記制御器の出力バスC[x:0]により制御可能なバッファにおけるPMOS/NMOSの排列を制御する。

(もっと読む)

1 - 14 / 14

[ Back to top ]