Fターム[5J022BA08]の内容

アナログ←→デジタル変換 (13,545) | 目的、効果 (2,366) | 利得制御化 (152)

Fターム[5J022BA08]の下位に属するFターム

圧縮、伸長、非線形化(μ、A則) (41)

Fターム[5J022BA08]に分類される特許

1 - 20 / 111

レベル調整装置、およびレベル調整のためのプログラム

【課題】ユーザに負担をかけることなく、容易にアナログ音響信号の音質劣化を抑制することが可能なレベル調整装置を提供すること。

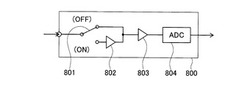

【解決手段】入力ポートはアナログ入力ブロック800を有し、アナログ入力ブロック800は、迂回スイッチ801、固定ゲインにて信号レベルの減衰を行うパッド802、可変ゲインにて信号レベルを増幅又は減衰して調整するアンプ803を備える。迂回スイッチ801はパッド802とアンプ803により信号レベルが調整されるパッドオン状態とアンプ803のみで信号レベルが調整されるパッドオフ状態を切り替えられる。信号レベルの調整の後に、パッドオン状態で、かつパッドのオン・オフの何れの状態でもゲインの調整が可能な重複範囲ROVの範囲内である入力ポートを抽出し、該当する入力ポートのアナログ入力ブロック800に対して、パッドオフ状態への切り替え調整処理を行う。

(もっと読む)

デジタル受信機及びそれを用いた光通信システム

【課題】受信信号の品質に応じて、AD変換器の識別レベルを適切に調整することにより、その実効的な分解能を向上させ、もって、高分解能と高速化の要求に応え得るデジタル受信機を提供する。

【解決手段】デジタル受信機は、識別レベル制御信号に応じて識別レベルを設定し、設定された識別レベルに基づいて入力アナログ信号をデジタル信号に変換するAD変換器102と、設定値に基づき識別レベル制御信号を生成し、AD変換器へ出力する識別レベル調整回路104と、設定値に基づきAD変換器の伝達関数に関する情報である伝達関数補正制御信号を生成する信号品質モニタ部108と、伝達関数補正制御信号に基づいて、AD変換器の伝達関数と初期伝達関数とのずれを相殺するようにデジタル信号を信号処理する伝達関数補正回路106とを備える。

(もっと読む)

アナログデジタル変換装置及び信号処理システム

【課題】アナログデジタル変換装置のサイズを縮小し、且つ、インタリーブ間のミスマッチに起因する誤差の補正に必要な処理量を低減する。

【解決手段】本発明の実施形態のアナログデジタル変換装置は、アナログ入力信号をデジタル出力信号に変換する。アナログデジタル変換装置は、アナログデジタル変換ユニット12と、疑似エイリアス信号生成部114と、利得制御部116と、エイリアス信号補正部118と、を備える。アナログデジタル変換ユニット12は、アナログ入力信号を、複数のデジタル信号に変換する。疑似エイリアス信号生成部114は、複数のデジタル信号を合成した合成信号に含まれるエイリアス信号成分を模擬する疑似エイリアス信号を生成する。利得制御部116は、疑似エイリアス信号を用いて、デジタル出力信号の利得を制御する利得制御信号を生成する。エイリアス信号補正部118は、利得制御信号を用いて、エイリアス信号成分を補正する。

(もっと読む)

データ処理装置、データ処理システム及び電力量計

【課題】増幅回路を用いてAD変換の分解能を拡大するAD変換技術において増幅回路のゲインに対する校正精度を向上させる。

【解決手段】目的ゲイン2n(nは正の整数)に対する前記増幅回路の実際のゲインを実測ゲインとして計測するゲインキャリブレーション処理を行い、アナログ信号を増幅回路で増幅してからAD変換回路で変換してビット拡張された変換データを取得する拡張AD変換処理において、前記増幅回路で増幅してから前記AD変換回路で変換して得られるデータに前記実測ゲインに対する前記目的ゲイン2nの比に応じた操作を施すことによってゲインに起因する誤差を相殺する。前記ゲインキャリブレーション処理では、デジタル的に既知の校正データに応ずる校正信号を目的ゲイン2n倍した信号のAD変換結果に対して、上記校正データをN倍した信号を増幅せずにAD変換して当該変換結果の1/Nの値を用いて、前記実測ゲインを求める。

(もっと読む)

半導体集積回路装置

【課題】レベル変換回路のレイアウト面積の縮小を図る。

【解決手段】半導体集積回路装置(10)は、レベル変換回路(14)と、D/A変換回路(12)とを備える。このとき、パラレル形式のデジタル信号をシリアル形式に変換して上記レベル変換回路に供給するためのパラレル・シリアル変換回路(15)と、上記レベル変換回路の出力をパラレル形式のデジタル信号に変換して上記D/A変換回路に供給するためのシリアル・パラレル変換回路(13)とを設ける。上記レベル変換回路は、シリアル形式のデジタル信号に対応するレベル変換機能を備えていれば良く、パラレル形式のデジタル信号に対応させる場合に比べて、レベル変換回路のレイアウト面積を縮小することができる。

(もっと読む)

アナログデジタル変換器および信号処理システム

【課題】低電力動作、高速動作が可能で、しかも小型化が容易で、出力段の増幅器のゲインを精度良く制御することが可能なAD変換器および信号処理システムを提供する。

【解決手段】入力した2つのアナログ信号との関係に応じた値のデジタルデータを生成し、2つのアナログ残差信号を第1の増幅器および第2の増幅器で、制御されるゲインをもって増幅して出力する複数のAD変換ステージと、第1の増幅器および第2の増幅器の出力信号のモニター結果に応じて第1の増幅器および第2の増幅器のゲインを制御するゲイン制御部と、を有し、第1の増幅器および第2の増幅器は、オープンループの増幅器により形成され、ゲイン制御部は、少なくとも1つのAD変換ステージにおける第1の増幅器および第2の増幅器の出力信号の振幅情報を取り出し、ステージから出力されるアナログ信号の振幅が、設定される設定振幅に収束するようにゲイン制御を行う。

(もっと読む)

アナログデジタル変換器

【課題】広い範囲のアナログ信号を高精度でデジタル信号に変換するためには前段に可変ゲインアンプが必要であるが、このため高価なアナログ部品が必要であった。本発明は簡単な構成でゲインを可変できるアナログデジタル変換器を提供することを目的にする。

【解決手段】アナログ信号とフィードバック信号の差分信号を積分し、この積分信号をそのレベルに対応するデューティ比を有する信号に変換して、この信号のデューティ比をゲイン設定器で(1/ゲイン)に変換した信号をデューティ/レベル変換してフィードバック信号を生成するようにした。高価なアナログ部品を使用しなくてもよい。

(もっと読む)

光伝送装置およびアナログ−デジタル変換装置

【課題】ADCを適切に補正することができる。

【解決手段】変換部1は、光信号を電気信号に変換する。増幅器2は、変換部1によって変換された電気信号を増幅する。ADC3a〜3nは、増幅器2で増幅された電気信号を時分割でアナログ−デジタル変換する。制御部4は、複数のADC3a〜3nの補正を行う際、複数のADC3a〜3nの出力の合計振幅または平均振幅が所定値以上となるように、増幅器2の増幅率を制御する。

(もっと読む)

デジタルアナログ変換装置およびその制御方法

【課題】処理負荷の増大を抑制しつつ、アナログ信号の出力レベルの精度を向上させる。

【解決手段】本発明のデジタルアナログ変換装置は、Nビットのデジタル信号をアナログ信号に変換して出力するDAコンバータと、所定のサンプリング周期で入力されるM(M>N)ビットのデジタル信号に示される第1の値を、Nビットのデジタル信号で示される範囲内の第2の値となるように所定比で縮小して出力するスケール変換部と、第2の値をNビットのデジタル信号で示される第3の値に変換して出力するビット長変換部と、所定のサンプリング周期内で、第2の値と第3の値との誤差を示す第4の値を入力値とする所定の演算を複数回行い、演算結果が0である場合には第3の値を、演算結果が正である場合には、第3の値から1を減算した第5の値を、演算結果が負である場合には、第3の値に1を加算した第6の値を、DAコンバータに出力する出力値決定部と、を有する。

(もっと読む)

A/Dコンバータ

【課題】アナログ入力信号の信号レベルに応じてFSR電圧を変化させることにより、D/Aコンバータの基準電圧を切り替える基準電圧発生回路の有無に関係なく、電圧変動の小さなアナログ入力信号に対する分解能を充分に向上させることができるA/Dコンバータを提供すること。

【解決手段】A/Dコンバータは、複数のアナログ入力信号のうちのいずれか1つを選択して出力する選択部の出力を第1比較基準電圧と比較する比較部と、前記複数のアナログ入力信号のうちのいずれか1つのアナログ入力信号の電圧変動範囲に応じた第2比較基準電圧を出力するD/Aコンバータと、前記選択部で選択されたアナログ入力信号の電圧変動範囲に応じて、前記D/Aコンバータが出力する第2比較基準電圧を前記第1比較基準電圧に切り替えて前記比較部に出力する切替部とを含む。

(もっと読む)

音声処理装置

【課題】大きなヘッドルームを設定したアナログ信号をデジタル処理回路で増幅したときのS/N特性を向上する。

【解決手段】音声処理系統11〜1nは、アナログ増幅回路21〜2n、AD変換回路31〜3n、デジタル処理回路41〜4nを有する。第1の音声処理系統11に入力されたアナログ信号は、分配スイッチ62を介して第1と第2の音声処理系統のアナログ増幅回路21、22に分配される。分配されたアナログ信号は、26dBに設定されたヘッドルームに基づいてアナログ増幅回路21、22で増幅され、AD変換回路31、32で−26dBFSのデジタル信号に変換される。これらのデジタル信号は、切換スイッチ71、72を介して、デジタル信号の加算・処理回路40に入力される。これらのデジタル信号は、デジタル信号の加算・処理回路40において加算、増幅され、一般的基準の出力レベルである−20dBFSのデジタル信号として出力される。

(もっと読む)

AD変換器及びAD変換回路の電圧制御方法

【課題】AD変換の際のアナログ入力振幅の収束時間を短縮させつつ、AD変換回路が想定する量子化分解能を最大限に活用することが可能なAD変換器を提供する。

【解決手段】アナログ信号からデジタル信号に変換するAD変換回路へ、アナログ信号の入力の振幅を可変させて出力するAGC回路と、AGC回路が出力するアナログ信号の出力範囲と、既定の電圧の範囲と比較して、該比較の結果に基づいてAGC回路が出力するアナログ信号の出力範囲を制御する第1検波部と、を備える、AD変換器が提供される。これにより、AD変換の際のアナログ入力振幅の収束時間を短縮させつつ、AD変換回路が想定する量子化分解能を最大限に活用することが可能なAD変換器を提供することができる。

(もっと読む)

音声伝送システム

【課題】多数段の音声処理装置を経由しても信号の劣化が少ない音声伝送システムを提供する。

【解決手段】ルーター1に、(1)入力されたアナログ音声信号をデジタル信号に変換するAD変換装置2、(2) デジタル音声信号に種々の処理を加える複数の音声処理装置3、(3) 処理されたデジタル信号を任意のアナログ音声信号に変換して出力するDA変換装置4を接続する。ルーター1に、他の音声処理システム10に接続される外部端子と、本システムを構成する各機器を制御するコンソール11を接続する。各装置2,3,4とルーター間で授受する信号を、32Bit浮動小数点フォーマットとする。

(もっと読む)

入力セレクタおよび信号処理回路

【課題】さまざまな入力形式の信号に柔軟に適応可能な汎用性の高い入力セレクタを提供する。

【解決手段】第1抵抗R1〜第4抵抗R4は、それぞれの第1端子が対応する入力ポートPi1〜Pi4に接続される。第1スイッチSW1〜第4スイッチSW4はそれぞれ、対応する抵抗と第1演算増幅器10の反転入力端子の間に設けられる。第5スイッチSW5、第6スイッチSW6はそれぞれ、対応する抵抗と、第2演算増幅器12の反転入力端子の間に設けられる。第5抵抗R5および第7スイッチSW7は第1演算増幅器10の出力端子と第2演算増幅器12の反転入力端子の間に直列に設けられる。第6抵抗R6は第1演算増幅器10の出力端子と反転入力端子の間に設けられ、第7抵抗R7は第2演算増幅器12の出力端子と反転入力端子の間に設けられる。

(もっと読む)

パイプライン型A/Dコンバータ

【課題】熱雑音および演算増幅器に要求されるオープンループゲインを大きくさせることなく、入力レンジおよびディジタル出力信号のビット数を大きくすることのできるパイプライン型A/Dコンバータを提供する。

【解決手段】サンプルホールド用のコンデンサの個数MをN分割し、さらに基準電圧をN倍することで、基準電圧を加減算するために用いることが出来るコンデンサの数を増加させて入力レンジを広げ、ディジタル出力信号のビット数を大きくする。この場合、全てのコンデンサでアナログ信号をサンプルするため、コンデンサを分割する前後で熱雑音を劣化させない。さらに、アナログ信号を増幅するための帰還素子として用いるコンデンサと、残りのコンデンサとの比はコンデンサを分割する前後で変わらないため、演算増幅器128に要求されるオープンループゲインを増加させない。

(もっと読む)

A/D変換装置

【課題】装置構成に要する費用が嵩んだり、装置が大型化することを防止し、変換周期を短縮する。

【解決手段】A/D変換装置10の記憶部12は、アナログ信号が入力される複数のチャンネルCH1,…,CHn毎に対応付けられた複数の基準電圧Vrefを予め記憶する。電圧選択部13は、記憶部12に記憶された複数の基準電圧Vrefの何れか1つを選択して基準電圧出力部14から出力させ、全チャンネルCH1,…,CHnのA/D変換が完了する毎に基準電圧Vrefの選択を変更して、全て基準電圧Vrefを順次出力させる。A/D変換器15は、全ての基準電圧Vrefと全チャンネルCH1,…,CHnとの組み合わせ毎のデジタル信号のうち、予め記憶部12に記憶された基準電圧Vrefと各チャンネルとの対応付けに等しい組み合わせのデジタル信号を出力する。

(もっと読む)

結合されたディジタル対アナログコンバータおよび信号フィルタ

【課題】簡易構成で低コストであり、設計が容易な広帯域のローパスフィルタを提供する。

【解決手段】ディジタル信号を処理する電子回路は、各々がディジタル信号の遅延されたレプリカを生成する、複数のディジタル遅延回路と、各々が、ディジタル信号、または遅延回路の1つからの遅延されたレプリカを、アナログ信号へ変換する、複数のディジタル対アナログコンバータと、各々がディジタル対アナログコンバータからのアナログ信号を利得係数によって調節する、かつ各々が出力をもつ、複数のアナログ利得回路と、アナログ利得回路の出力を加算するアナログ加算器とを含むことができる。

(もっと読む)

DA変換装置

【課題】シングルスロープ積分型AD変換用の参照信号の傾きを高精度に制御できるDA変換装置を提供する。

【解決手段】参照信号を得る第1DA変換部302に対して、第2DA変換部304で得られたDA出力電流Igainに基づいてゲイン制御を加える。電流源セル部350内の各電流源セル353,355は、DA出力電流Igainに応じたバイアス電圧Vbaisでその動作電流が規定される。第1DA変換部302において、下位ビット制御部330は、分周動作を行ない1/2^k分周クロックを使用して重付け電流値の下位電流源セル533を選択する。上位ビット制御部340は、下位ビット制御部330の分周動作で生成される所定分周クロックをシフトクロックとして使用してシフトレジスタ部342内の各シフトレジスタのシフト出力を順次Hにし、このシフト出力を使用して同一重付け電流の上位電流源セル355を順次選択する。

(もっと読む)

並列補間型A/D変換器及びディジタル等化装置

【課題】分解能を上げることによる回路面積及び消費電力の増大を抑えた並列補間型A/D変換器を提供する。

【解決手段】m+1個(mは正の整数)の参照電圧VR1〜VRm+1(ただし、VR1<VR2・・・<VRm<VRm+1)を生成する参照電圧生成回路111と、参照電圧VR1〜VRm+1の各々と入力信号電圧との電圧差を増幅するm+1個の差動増幅器A1〜Am+1を有する差動増幅器列112と、各差動増幅器からそれぞれ生成される出力電圧セットを受け取る複数個の比較回路を含む動作回路113とを設ける。ここで、より重要な情報を含むアナログ信号成分を精度良く変換できるよう特定の範囲では回路ばらつき耐性を高め、重要でない情報成分を変換する範囲は回路ばらつき耐性を低くするように、参照電圧をVRk(kは2≦k≦m+1の整数)とするとき、参照電圧VRkのk値に応じて比較回路の個数を異ならせる。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22と判定クロック端子23とリセット端子24と温度補償クロック端子25と2値化出力端子26と遅れ出力端子28とピークホールド回路30とボトムホールド回路40と2値化判定回路120と入力信号検出回路130と停止判定回路140を備えている。2値化回路10では、停止判定信号が入力信号の停止期間を検出し、この停止期間にピークホールド回路30とボトムホールド回路40が、各々の記憶値を入力信号に追従して変化させる。これによって、停止期間に、入力信号がピークホールド回路30とボトムホールド回路40の記憶値から算出される閾値を越えて変化することが抑制され、停止期間に2値化出力が反転することが抑制される。

(もっと読む)

1 - 20 / 111

[ Back to top ]