Fターム[5J022CD02]の内容

アナログ←→デジタル変換 (13,545) | 変換処理系 (818) | 符号変換及び補正処理(試験パターン) (783) | メモリ (270)

Fターム[5J022CD02]に分類される特許

1 - 20 / 270

アナログデジタル変換装置

DACの直線歪補正回路

デジタル−アナログ変換器及びそのような変換器を用いた神経形態学的回路

AD変換器、光電変換装置、および撮像システム

【課題】 並列型AD変換器におけるカウンター回路の動作を精度良く制御する。

【解決手段】 第1クロック信号を計数してカウント信号を出力するカウンター回路と、第1クロック信号に基づいて、第2クロック信号を生成する第2クロック信号生成部と、カウント開始信号を前記第2クロック信号に同期して出力するクロック同期化部と、を有し、カウンター回路は、第2クロックに同期したカウント開始信号に応じて計数を行う。

(もっと読む)

ランプ信号出力回路、アナログデジタル変換回路、撮像装置、ランプ信号出力回路の駆動方法

【課題】 ADCにおいて、ランプ信号の電位の時間に依存した変化の開始に先立って、ランプ信号のランプ開始電位をシフトする形態が知られている。このランプ信号の電位をシフトする方法として、従来は積分アンプの入出力端子間に設けられた積分容量に電流を印加して充放電させていた。従って、ランプ信号のランプ開始電位をシフトするのに積分容量を充放電する期間を要していた。

【解決手段】 ランプ信号のランプ開始電位をシフトさせる電圧供給部を有することを特徴とするランプ信号出力回路である。

(もっと読む)

アナログデジタル変換回路、撮像装置、アナログデジタル変換回路の検査方法

【課題】 カウンタが複数のメモリに共通してカウント信号を供給する列ADCにおいて、カウンタからメモリへカウント信号を伝送する信号経路の不良によって生じる、メモリに供給されるカウント信号の遅延を好適に検出することを目的とする。

【解決手段】 カウント信号の信号値が変化したタイミングに応じて、カウント信号をメモリに保持させるラッチ信号をメモリに供給するテストラッチ信号供給部を有するアナログデジタル変換回路である。

(もっと読む)

温度情報出力装置の温度情報出力方法

【課題】温度情報出力装置の面積を増やさなくとも動作可能な温度範囲を増やすことができる、温度情報出力装置の温度情報出力方法を提供する。

【解決手段】温度を感知し、当該温度に対応する第1の電圧VTEMPを出力するステップと、第1の電圧VTEMPと第2の電圧DACOUTとを比較するステップと、この比較結果に基づいて、デジタルコードDIGITAL_CODEを加減するステップと、デジタルコードDIGITAL_CODEによって変化する第2の電圧DACOUTを生成するステップとを含み、デジタルコードDIGITAL_CODEによって変化する第2の電圧DACOUTの変化幅が温度区間別に異なる。

(もっと読む)

アナログユニット

【課題】コストアップを抑制しつつ、温度ドリフトに対する出力値を補正することが可能なアナログユニットを提供する。

【解決手段】入力値を出力値に変換する変換回路12と、前記変換回路の温度が初期状態から定常状態に至る間の2つの時点における前記入力値と出力値との関係を示す設定値を記憶する記憶部14と、前記記憶部に記憶された設定値に基づいて、前記変換回路の出力値を校正する校正部13とを備え、時間経過に基づいて設定値を補間する。

(もっと読む)

データ処理装置、データ処理システム及び電力量計

【課題】増幅回路を用いてAD変換の分解能を拡大するAD変換技術において増幅回路のゲインに対する校正精度を向上させる。

【解決手段】目的ゲイン2n(nは正の整数)に対する前記増幅回路の実際のゲインを実測ゲインとして計測するゲインキャリブレーション処理を行い、アナログ信号を増幅回路で増幅してからAD変換回路で変換してビット拡張された変換データを取得する拡張AD変換処理において、前記増幅回路で増幅してから前記AD変換回路で変換して得られるデータに前記実測ゲインに対する前記目的ゲイン2nの比に応じた操作を施すことによってゲインに起因する誤差を相殺する。前記ゲインキャリブレーション処理では、デジタル的に既知の校正データに応ずる校正信号を目的ゲイン2n倍した信号のAD変換結果に対して、上記校正データをN倍した信号を増幅せずにAD変換して当該変換結果の1/Nの値を用いて、前記実測ゲインを求める。

(もっと読む)

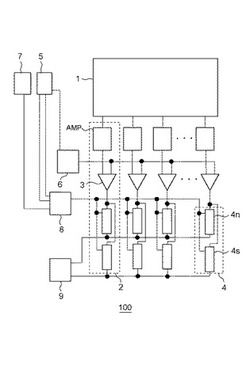

アナログデジタル変換回路、アナログデジタル変換回路の検査方法、撮像装置、撮像装置を有する撮像システム、撮像装置の検査方法

【課題】複数のメモリ間でのショート故障の有無を検査できる構成を有するADCおよびその検査方法、ADCを有する撮像装置、撮像装置を有する撮像システムを提供する。

【解決手段】複数のメモリと複数の比較器とを含んで構成される回路部を複数有し、アナログ信号をデジタル信号に変換するアナログデジタル変換回路であって、複数の回路部の一部に含まれるメモリと複数の回路部の別の一部に含まれるメモリとで異なるデジタル信号を保持するようにテスト信号を供給するテスト信号供給部と、出力比較部と、転送部を有することを特徴とするアナログデジタル変換回路である。

(もっと読む)

ADコンバータ

【課題】高精度で小型のADコンバータを提供する。

【解決手段】このADコンバータは、アナログ電圧VinをNビットのデジタルコードDCに変換するものであり、メモリブロックMB1〜MB(2N−1)を備える。各メモリブロックMB(2n−1)は、(2n−1)個のMRAM用のメモリセル1を含む。メモリセル1の記憶データを「0」にリセットした後に、アナログ電圧Vinに比例するアナログ電流Iinを、各メモリブロックMB(2n−1)の(2n−1)本のビット線BLに分流させる。メモリブロックMB1〜MB(2N−1)のメモリセル1の記憶データを読み出してデジタルコードDCを生成する。したがって、ラダー抵抗は不要である。

(もっと読む)

A/Dコンバータ、マイコン、故障判定方法

【課題】AD変換中にアナログ入力の値が変動したことをより高精度に判別可能なA/Dコンバータを提供すること。

【解決手段】アナログ入力の下限値と上限値が登録された判定テーブル28と、アナログ入力と、アナログ値に変換された基準値を比較する比較手段24と、前記比較手段がアナログ入力の方が基準値より大きいと判定するとより大きい基準値に変更し、アナログ入力の方が基準値より小さいと判定するとより小さい基準値に変更する基準値変更手段26と、比較結果及び基準値を取得し、アナログ入力の方が基準値より小さい場合は前記判定テーブルの前記上限値に基準値を設定し、アナログ入力の方が基準値より大きい場合は前記判定テーブルの前記下限値に基準値を設定するテーブル更新手段27と、アナログ入力が前記下限値と前記上限値の範囲に入るか否かを判定する異常判定手段29と、有する。

(もっと読む)

半導体テスト装置および半導体装置の製造方法

【課題】半導体装置のテスト用電源電圧として、複雑なパターンの電源波形を短時間で、高精度に生成する。

【解決手段】マルチプレクサ16から出力された電圧変化値ΔVは加算器17により電圧設定値保持部19に格納された電圧値が加算される。この加算結果は電圧設定値保持部19に格納される。加算回路20は加算器17の加算結果に、電圧初期値格納部18の初期値データを加算する。この加算結果は、補正器21が補正情報に基づいて補正する。制御回路26は比較器24の比較結果に基づいて補正器21のデジタルデータが上限/下限電圧になったかを判定し、到達していない場合、補正器21の信号を時間情報格納部25のデータ転送時間間隔ΔTに基づいて出力する。D/A変換器12は、その信号をアナログ信号に変換し、デバイス供給電源アナログ回路13に増幅されて電源電圧VCCとして出力される。

(もっと読む)

フィールド機器管理システム

【課題】フィールド機器の状態を監視するに際して、フィールド機器が接続されているアナログ通信路を通じた通信の状態を確認できるようにする。

【解決手段】機器監視ユニット15は、(1)フィールド機器10におけるアナログ通信路へのアナログ出力値についてのデジタル設定値と、(2)入出力ユニット11におけるAD変換器1153のデジタル値、及び、(3)入出力ユニット11のメモリ14に記憶されたデジタル設定値の一方との組を、それぞれデジタル通信路16を通じて取得し、取得した各値に基づいて、アナログ通信路を通じた通信の状態をチェックする。

(もっと読む)

データ収集装置、データ収集方法および計測装置

【課題】センサからの計測信号を高速かつ正確にA/D変換を行うことができるデータ収集装置およびデータ収集方法、およびデータ収集装置を組み込んだ計測装置を提供する。

【解決手段】データ収集装置は、計測センサにおいて第1クロック信号に基づいて計測条件が順次周期的に切り替わることで得られる、前記計測条件に対応する計測信号が連なった一連の計測信号の入力を受け、第2クロック信号のタイミングでA/D変換を行い順次レジスタに重ね書きして一時記憶するA/D変換ユニットと、前記第1クロック信号に基づいて生成されるサンプリングパルスのタイミングで、レジスタに一時記憶した計測信号を読み出し、前記サンプリングパルスのパルス発生回数に応じて定まる格納位置に記憶するメモリと、を有する。計測装置は、例えば、計測センサとして用いるレーダと、上記データ収集装置とを含むレーダ装置である。

(もっと読む)

アナログ信号の入力装置及びその入力診断方法

【課題】多チャンネルのアナログ信号の診断処理を高速に実行するアナログ信号の入力装置及びその入力診断方法を提供する。

【解決手段】アナログ信号の入力装置10は、外部入力したアナログ信号A及び発生させた基準電圧Eのうちいずれかを出力するマルチプレクサ23と、マルチプレクサ23が出力した信号をデジタル変換するA/D変換部25と、マルチプレクサ23及びA/D変換部25が設けられている複数のチャンネル12と、各々のチャンネル12においてデジタル変換された複数の基準電圧Fから最悪値Fbadを抽出する信号抽出部13と、複数のチャンネル12及び信号抽出部13が設けられているセグメント11と、複数のセグメント11の各々から出力される複数の最悪値Fbadを閾値Gと対比して各々のセグメント11を単位にアナログ信号Aの入力診断をする診断部14と、を備えている。

(もっと読む)

A/Dコンバータの試験装置および試験方法

【課題】A/Dコンバータの試験時間の短縮にある。

【解決手段】Nビット(Nは自然数)のA/Dコンバータ1を試験する試験装置2が提供される。電圧生成部10は、A/Dコンバータ1に対して、2N階調のアナログ電圧VINを出力する。キャプチャユニット20は、各階調におけるA/Dコンバータ1の出力コードDOUTをキャプチャする。信号処理部30は、各階調においてキャプチャされた出力コードDOUTを対応する期待値コードEXPと比較し、比較結果に応じて各階調のアナログ電圧VINの値を補正し、電圧生成部10に補正後のアナログ電圧VINを出力させる。

(もっと読む)

パラレルデータ出力制御回路及び半導体装置

【課題】常に信頼性の高いパラレルデータ出力制御が行えるをパラレルデータ出力制御回路を得る。

【解決手段】CPU12はバッファ13からのリクエストRQに応答して内蔵RAM11よりデジタルデータをバッファ13に出力する。バッファ13は複数段構成のFIFOを有し、FIFOの各段は1単位(10ビット)のデジタルデータを格納可能であり、バッファ13全体としてFIFOの構成段数単位分のデジタルデータを格納することができる。レジスタ14は出力制御クロックCK15に同期して、バッファ13内部に格納したデジタルデータを1単位ごとに取り込む。レジスタ14に格納されたデジタルデータがD/A変換用データDataとしてパラレルDAC2に出力される。WR信号出力タイマ17は出力制御クロックCK15に同期して“L”の1ショットパルスを有する書き込み制御信号WRを生成する。

(もっと読む)

A/D変換器、A/D変換方法

【課題】簡易な構成で且つ低消費電力(低発熱)なA/D変換器の実現。

【解決手段】入力アナログ信号を抵抗を用いて複数レベル(n種のレベル)に分割し、分割したそれぞれのアナログ信号に基づき各磁気メモリ素子に書込動作が行われるようにする。これによりn種の各レベルごとに符号「0」又は「1」の判定を行うことができ、これら各レベルごとの判定結果に基づいてnビットの量子化データを得ることができる。つまり量子化ビット数=nによる並列型A/D変換を実現できる。或いは、入力アナログ信号を抵抗により複数レベルに分割する代わりに、各磁気メモリ素子としてそれぞれその反転電流値が異なるものを設けることによっても、上記と同様の結果を得ることができる。並列型A/D変換器の実現にあたり従来のようにオペアンプを備える必要はなくなり、結果、簡易な構成で且つ低消費電力・低発熱のA/D変換器を実現できる。

(もっと読む)

高分解能デジタル・アナログ変換装置及び方法

【課題】安価でありながら、高分解能のアナログ信号を出力可能であるとともに、低精度変換処理と高精度変換処理との両変換処理が選択可能な高分解能デジタル・アナログ変換装置を実現する。

【解決手段】DAC306は上位ビット用のDACと下位ビット用のDACとを有し、予め定めたデジタルデータが供給され、このデジタルデータから得られるアナログデータの理論値と、実際のDAC306から出力されたアナログデータとが比較され、補正データが作成されてメモリ301に格納される。メモリ301に格納された補正データを用いてDAC306からの出力データが補正される。補正方法は、高精度であるがキャリブレーションに長時間必要な全ビット方式と、全ビット方式より精度は劣るが短時間でキャリブレーションが可能な直線近似方式とがあり、必要に応じていずれかの補正方式が選択可能である。

(もっと読む)

1 - 20 / 270

[ Back to top ]