Fターム[5J022CF10]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 信号検出トランスジューサ (238)

Fターム[5J022CF10]に分類される特許

41 - 60 / 238

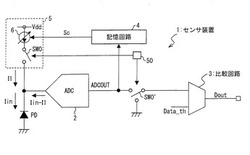

センサ装置及び電子機器

【課題】外光である太陽光等の周囲光による誤動作が生じないセンサ装置及び電子機器を提供する。

【解決手段】センサ装置1において、ADC2は、電流Iinと電流I1との差の電流を求める減算による電流Iin−I1に応じたデジタル値ADCOUTであって、閾値Data_thよりも大きい第2データを、比較回路3の一方の入力に出力する。

(もっと読む)

光伝送装置およびアナログ−デジタル変換装置

【課題】ADCを適切に補正することができる。

【解決手段】変換部1は、光信号を電気信号に変換する。増幅器2は、変換部1によって変換された電気信号を増幅する。ADC3a〜3nは、増幅器2で増幅された電気信号を時分割でアナログ−デジタル変換する。制御部4は、複数のADC3a〜3nの補正を行う際、複数のADC3a〜3nの出力の合計振幅または平均振幅が所定値以上となるように、増幅器2の増幅率を制御する。

(もっと読む)

AD変換方法及びAD変換回路

【課題】CPUが介在することなく複数種類のアナログ信号を所望の順番でAD変換し、所定時間内で複数種類のアナログ信号をAD変換する場合に最も効率的な結果が得られるよう用途に応じた設定を可能とするAD変換回路を提供することを目的とする。

【解決手段】シーケンス情報に対応して信号選択情報と時間情報を記憶した保持部と、一致信号の供給によりカウントを行う順番カウンタと、クロックの供給によりカウントを行う期間カウンタと、順番カウンタのカウント値で保持部のシーケンス情報を参照して得られる時間情報と期間カウンタのカウント値が一致したとき一致信号を生成する比較器と、複数種類のアナログ信号のうち、順番カウンタのカウント値で保持部のシーケンス情報を参照して得られる信号選択情報に対応する1種類のアナログ信号を選択する選択部と、選択部で選択された1種類のアナログ信号をAD変換するAD変換器とを有する。

(もっと読む)

半導体装置

【課題】比較的高速処理の必要な入力信号の処理の遅延を従来よりも低減する。

【解決手段】半導体装置100において、変換部2は、第1のチャネルCH0〜CH2および第2のチャネルCH3〜CH5を有し、選択中のチャネルに入力された信号をA/D変換する。第1のチャネルに入力される信号は、第2のチャネルに入力される信号よりも高速の処理が必要とされる。変換部2は、中央処理装置1などからスキャン変換指令を受けた場合に、複数の入力チャネルCH0〜CH5を所定の選択順で順次選択して連続的にA/D変換を行なう。この場合、変換部2は、第1のチャネルCH0〜CH2に入力された信号のA/D変換が完了した後でありかつ全入力チャネルの入力信号のA/D変換が完了する前に、A/D変換の完了を周辺回路IP0に通知する。

(もっと読む)

パルス走行位置検出回路、A/D変換回路および固体撮像素子

【課題】高精度でパルス信号の走行位置を検出することができ、狭小な場所にも配置することができるパルス走行位置検出回路、これを用いたA/D変換回路、およびこのA/D変換回路を用いた固体撮像素子を提供する。

【解決手段】印加された電源または該電源に応じた電流源に応じた遅延時間でパルス信号を遅延させる複数の遅延素子を具備した同一の構成の遅延回路が、少なくとも1つのフィードフォワード回路が形成されるように、直列の円環状に複数段連結されたパルス走行回路と、複数の遅延回路のそれぞれから出力される出力信号を検出して保持した情報を走行位置の情報として出力するラッチ回路とを備え、それぞれの遅延回路は、第1の遅延素子と、構造が異なる第2の遅延素子とを具備し、少なくとも1つの遅延回路内にパルス信号の走行を開始させる起動信号を入力し、他の遅延回路内に、少なくともパルス信号が走行している間は所定の固定電圧を入力する。

(もっと読む)

半導体装置および固体撮像装置

【課題】画素情報の読出し速度を向上させることが可能な半導体装置および固体撮像装置を提供する。

【解決手段】カラムADCは、PGA22と、縦列接続された2つの巡回型ADCとを含む。PGA22は、画素の黒レベルおよび信号レベルの差分を増幅した信号にVrefを加算した電位をPGA画素情報として出力する。第1ADC24_1は、Vrefを参照電位としてサンプリングして保持するとともに、PGA画素情報を信号電位としてサンプリングして保持し、これらの差分信号であるi行の画素情報に応じてデジタル値の中の上位ビットを生成すると、(i+1)行の画素情報のサンプリングを開始する。第2ADC24_2は、第1ADC24_1が(i+1)行の画素情報をサンプリングして保持するのと並行して、第1ADC24_1によって生成された上位ビットに応じて該デジタル値の中の下位ビットを生成する。

(もっと読む)

A/D変換装置、A/D変換方法および固体撮像装置

【課題】遅延素子の伝搬遅延時間の立ち上がりと立ち下がりとの特性に影響されることなく、リニアリティ精度を向上したデジタル出力値を得ることができるA/D変換装置、A/D変換方法および固体撮像装置を提供する。

【解決手段】アナログ入力信号の大きさに応じてパルス信号を遅延させて伝播する遅延ユニットを円環状にn(n:自然数、1≦n)個連結したn段のパルス遅延回路と、遅延ユニットの出力信号に基づいて所定のサンプリング時間内の周回数および遅延ユニットの位置を取得するパルス位置取得回路と、サンプリング時間が終了したときの周回数と遅延ユニットの位置とに応じたデジタル信号を生成するパルス位置数値化回路と、デジタル信号に基づいてパルス信号を伝播させるサンプリング時間を変更し、該変更したサンプリング時間での周回数に基づいて、アナログ入力信号の大きさに応じたデジタル出力値を生成するサンプリング制御回路と、を備える。

(もっと読む)

AD変換システム

【課題】ダイナミックレンジと分解能を両立させつつ高速なAD変換ができるAD変換システムを提供することを課題とする。

【解決手段】アナログ信号をデジタル信号に変換するAD変換システム1であって、アナログ入力信号をAD変換器15の複数のチャネル(Ch1,Ch2,Ch3)別に複数の電圧範囲に分割する分割手段13,14と、分割手段13,14で分割された異なる電圧範囲毎のアナログ入力信号をAD変換器15の各チャネルでそれぞれAD変換する分割AD変換手段15(Ch1,Ch2,Ch3)と、分割AD変換手段15でAD変換された異なる電圧範囲毎のデジタル信号を合成する合成手段16とを備えることを特徴とする。

(もっと読む)

AD変換方法およびAD変換装置

【課題】AD変換装置を同一チップ上に搭載した固体撮像装置において、回路規模、消費電力、消費電流、インタフェース用配線数、ノイズなどの問題を解消する。

【解決手段】電圧比較部252とカウンタ部254とを有するカラムAD回路25を垂直信号線19ごとに設ける。電圧比較部252は、行制御線15ごとに垂直信号線19を経由し入力される画素信号と参照電圧RAMPとを比較し、リセット成分や信号成分の各大きさに対応した時間軸方向に大きさを持つパルス信号を生成する。カウンタ部254は、電圧比較部252の比較完了までパルス信号の幅をクロックCK0でカウントし、比較完了時点のカウント値を保持する。通信・タイミング制御部20は、1回目は電圧比較部252でリセット成分を比較処理しカウンタ部254がダウンカウントする一方、2回目は電圧比較部252で信号成分を比較処理しカウンタ部254がアップカウントするように制御する。

(もっと読む)

アナログデジタル変換装置

【課題】デジタル回路とアナログ回路とを、単一電源電圧かつ低消費電力で混載することを可能にする。

【解決手段】A/D変換部32は、電源端子と接地端子との間に接続され、入力電圧に応じてハイレベルの出力またはローレベルの出力を生成するデジタル信号生成部32aと、接地端子とデジタル信号生成部32aとの間における電位差としてのオフセット電圧Vofsを発生するオフセット電圧発生部32bとを有する。ここで、オフセット電圧発生部32bは、デジタル信号生成部32aに印加される電源電圧を低減すべく、オフセット電圧Vofsを発生する。

(もっと読む)

A/D変換回路及び固体撮像装置

【課題】小型化を実現したA/D変換回路及び固体撮像装置を提供する。

【解決手段】遅延回路42の複数の遅延素子の各々の第1のパルス入力端子は複数の遅延素子の対応する1つのパルス出力端子に接続される。また、複数の遅延素子は、第1のパルス入力端子に入力されたパルス出力信号を、アナログ信号入力端子に入力されたアナログ信号に応じて遅延させてパルス出力端子から出力し、複数の遅延素子のいずれか1つは外部からパルス信号が入力される。状態変化検出回路47は、複数の遅延素子のうちの連続する2つからのパルス出力信号を順に比較し、2つのパルス出力信号の間で状態が異なるときに状態変化検出信号を出力する。エンコード信号ラッチ回路48は、状態変化検出信号が入力された場合に、状態変化検出回路47にパルス出力信号を出力した遅延素子に応じた状態を有するエンコード信号をラッチする。

(もっと読む)

固体撮像装置

【課題】AD変換の分解能を変更する際に、変更が必要なパルスのみの変更を、より簡単な構成で行うことができるようにする。

【解決手段】AD変換の分解能のモードが9ビットモードである場合には、デコーダ102は、Hカウンタ104のみを動作させる。AD変換の分解能のモードが10ビットモードまたは12ビットモードである場合には、デコーダ102は、Hカウンタ104のカウント値がレジスタ101に記憶されている開始カウント値となったときに、Hカウンタ104のカウント動作を停止させるとともに、アイドルカウンタ106のカウントを開始させ、アイドルカウンタ106のカウント値がレジスタ101に記憶されたカウント数となったときにHカウンタ104のカウントを再開させる。本発明は、例えば、カラムAD変換方式を採用したイメージセンサに適用できる。

(もっと読む)

ハイブリッド・アナログ/デジタル変換器、イメージセンサおよび複数のデジタル信号を提供するための方法

【課題】パワーおよびエリア比により良い変換率を有するアナログ/デジタル変換器を提供する。

【解決手段】ハイブリッド・アナログ/デジタル変換器100は、複数の変換回路101a〜101nを含む。それぞれの変換回路は、逐次近似変換の結果として、デジタル信号103a〜103nの第1の数のビットを得るために逐次近似変換を実行することによって、さらに、デジタル信号の第2の数のビットを得るために共通可変基準電圧105に基づいて傾斜変換をその後に実行することによって、アナログ入力信号104a〜104nに基づいてデジタル信号を提供するように構成され、第2の数のビットは、アナログ入力信号および逐次近似変換の結果間の残差に対応する。ハイブリッド・アナログ/デジタル変換器は、複数の変換回路のそれぞれの変換回路に共通可変基準電圧を提供するように構成される共通可変基準電圧プロバイダ102をさらに含む。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスのチャネル信号が第1、第2信号で構成される場合に第1、第2信号の差分に対応する信号の精度の高いA/D変換を実現する集積回路装置等の提供。

【解決手段】集積回路装置は、センサーデバイスからの第1信号SG1が第1期間において入力され、第1信号SG1とペアーとなってセンサーデバイスのチャネル信号を構成する第2信号SG2が第2期間において入力され、第1信号SG1と第2信号SG2の差分に対応する信号を出力する増幅回路と、増幅回路の出力信号についてのA/D変換を行うA/D変換器を含む。増幅回路は、増幅回路が有する演算増幅器のオフセット電圧をキャンセルするスイッチドキャパシター回路により構成される。

(もっと読む)

比較回路及び信号変換装置

【課題】アナログデジタル変換の分解能を向上させる比較回路及び信号変換装置を提供する。

【解決手段】比較回路22は、コンパレータ22aが、第1の入力端子に接続される第1の電圧源により、第1の入力端子に印加される電圧と、第2の入力端子に入力される入力信号の電圧とを比較する。コンデンサ22bが、第1の入力端子に一方の端子が接続され、第1の電圧源側に他方の端子が接続される。スイッチ22cが、第1の入力端子への基準電圧源22の接続を選択的に遮断する。スイッチ22dが、コンデンサ22bの他方の端子への第1の電圧源の接続を選択的に遮断する。基準電圧源22fが、コンデンサ22bの他方の端子に接続される。スイッチ22eが、基準電圧源22fによりコンデンサ22bの他方の端子に印加される電圧を選択的に遮断する。

(もっと読む)

アナログ−デジタル変換回路、照度センサ、近接センサ、測距センサ、携帯電話、およびデジタルカメラ

【課題】微小なアナログ入力電流を高い精度で検出することが出来るアナログ−デジタル変換回路を提供する。

【解決手段】アナログ−デジタル変換回路1は、アナログ入力電流Iinをデジタル変換してデジタル値ADCOUTを得るADC2(アナログ−デジタル変換部)を備えるアナログ−デジタル変換回路であって、所定期間毎に得られた所定個数のデジタル値ADCOUTを記憶するレジスタユニットと、レジスタユニットが記憶しているデジタル値ADCOUTを全て加算することによって加算値ADD[N]を算出する加算器と、加算値ADD[N]と所定の閾値とを比較するとともに、当該比較の結果に従ってデジタル出力信号DOUTを出力する比較回路5とを備える。

(もっと読む)

A/D変換装置、固体撮像装置および電子情報機器

【課題】上記線状ノイズを低減すると共に高速変換動作を行う。

【解決手段】ゼロ電圧に対応するA/D変換値を記憶する第1変換出力ラッチ8と、シグナル電圧とリセット電圧の差分電圧に対応するA/D変換値を記憶する第2変換出力ラッチ7とを有し、第2変換出力と第1変換出力の減算を行うことでオフセット電圧を解消する。オフセット電圧はゼロ付近の小さな値であるため、アナログランプ電圧の変化量は第1変換動作の方が第2変換動作よりも小さくでき、その結果、全体に要する動作時間に対する第1変換動作の割合は凡そ1割以下にできる。

(もっと読む)

A/D変換方法およびカメラシステム

【課題】カウンタをクロックの両エッジでカウント可能とし、かつアップ・ダウンカウント値を保持したまま切り替えることができ、両エッジカウントでもカウント動作のデューティが崩れにくいA/D変換回路、固体撮像素子、およびカメラシステムを提供する。

【解決手段】ADC15Aは、コンパレータ151および非同期カウンタ152を用いた積分型A/D変換回路として構成され、カウンタ152は、値を保持したままアップカウントからダウンカウントへ、また、ダウンカウントからアップカウントへ、カウントモードを切り替えられる機能と、入力クロックCKの立ち上がり、立ち下りの両エッジでカウントする、入力クロックの倍の周波数でカウントする機能と、コンパレータ151の出力の非同期信号により、入力クロックCKを非同期でラッチし、そのラッチデータの正転、または反転データをLSBのデータとする機能とを有する。

(もっと読む)

変換装置、及び計測装置

【課題】温度調整手段が別途不要で内部の温度調整対象を適温に制御可能な構成とすることで、使用環境温度が変化しても安定して高精度な計測結果が得られる計測装置を提供する。

【解決手段】デジタル処理回路での処理にかかるA/Dコンバータの待機時間での通常モードと待機モードとの時間割合(時間ta,tbの割合)をアナログ回路の周囲温度の検出温度に基づいて変更し、各モードの異なる電力消費に基づく発熱量の違いにてその周囲温度の温度制御を行うようにした。つまり、A/Dコンバータの動作不要な時間にA/Dコンバータ自身を温度調整手段として機能させることでその温度制御が行われる。

(もっと読む)

積分型A/D変換器、積分型A/D変換方法、固体撮像素子、およびカメラシステム

【課題】性能のトレードオフが少なく、クロック周波数をあげずに分解能を向上させることが可能な積分型A/D変換器、積分型A/D変換方法、固体撮像素子、およびカメラシステムを提供する。

【解決手段】時間とともに電圧値が線形に変化するランプ波形の参照電圧と入力電圧とを比較する比較器11と、比較器11の出力信号VCOが反転したことをトリガとして動作開始または動作停止し、クロック信号CLKの周期ごとに計数して上位ビットを出力する上位ビットカウンタ12と、比較器11の出力信号を遅延させた複数の信号に応じたクロック信号CKの位相情報をラッチし、そのラッチした値をデコードすることでクロック周期より分解能が高い下位ビットを出力する時間量子化器13とを有する。

(もっと読む)

41 - 60 / 238

[ Back to top ]