Fターム[5J022CF10]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 信号検出トランスジューサ (238)

Fターム[5J022CF10]に分類される特許

121 - 140 / 238

アナログデジタル変換器及びアナログデジタル変換方法、並びに撮像装置及びその駆動方法

【課題】高速処理に対応可能なアナログデジタル変換器を提供する。

【解決手段】先のタイミングでアナログデジタル変換がなされた複数のアナログ信号のうち、最大の電圧値を示す電圧値V(N−1)よりも所定電圧d(d1、d2)だけ大きな電圧値を初期電圧値(DP、DD)としたダウンカウントのランプ波LNを生成する。こうして生成されたランプ波LNを利用して後のタイミングでアナログデジタル変換を行なう。

(もっと読む)

アナログ/デジタル変換器

【課題】アナログ/デジタル変換器のビット数を、複雑さ又は処理時間を過度に増加させずに増加させることを目的とする。

【解決手段】アナログ信号をn ビットのデジタルデータに変換するアナログ/デジタル変換方法において、前記アナログ信号の振幅を、フルスケールアナログ信号の振幅を2k(k; nより小さい整数)で除算した閾値と比較する比較ステップと、前記アナログ信号をn-k ビットにアナログ/デジタル変換を行い、前記比較ステップの結果が前記アナログ信号の振幅が前記閾値より大きいことを示す場合、n ビットのデジタルデータのMSB 側のn-k ビットを得て、前記比較ステップの結果が前記アナログ信号の振幅が前記閾値以下であることを示す場合、前記n ビットのデジタルデータのLSB 側のn-k ビットを得るステップとを備える。

(もっと読む)

デジタルマイク

【課題】A/Dコンバータへの入力電圧の制限範囲を、A/Dコンバータのフルスケール電圧に対応して精度良く設定可能なデジタルマイクを提供する。

【解決手段】デジタルマイク1は、マイク素子2から入力信号V12を入力し、該入力信号V12に応じたアナログ信号V14を出力するとともに、該アナログ信号V14を所定の電圧範囲に制限するバッファ3と、バッファ3からアナログ信号V14を入力してデジタル信号に変換するA/Dコンバータ4と、バッファ3の所定の電圧範囲を規定する基準電圧V13をバッファ3へ提供するとともに、A/Dコンバータ4のフルスケール電圧を規定する特定電圧V11をA/Dコンバータ4へ提供する基準電圧生成部5とを備え、基準電圧生成部5が、基準電圧V13および特定電圧V11を共通の回路(基準電圧発生回路51)からの出力電圧を基に生成する。

(もっと読む)

AD変換制御装置及び車両制御装置

【課題】 AD変換の処理遅延を低減させたAD変換制御装置を提供する。

【解決手段】 AD変換器11の起動セットを行ってからAD変換器11の起動が行われるまで、既にセットしたチャネルとは異なるチャネルについての非同期のAD変換要求があると、AD変換要求のあった複数のチャネルについてのAD変換を行うのに要する時間を考慮した所定時間後にAD変換が行われるように、AD変換器11の起動セットを再度行うCPU13を有している。

(もっと読む)

多チャンネル信号処理装置

【課題】比較的低速で幅広いレンジを計測するとともに、比較的狭いレンジで高速かつ高分解能で計測する多チャンネル信号処理装置を得る。

【解決手段】センサ信号S1からセンサ低速信号S4を抽出するローパスフィルタ2と、センサ低速信号S4を基準信号S2として記憶する基準信号記憶器3と、センサ信号S1と基準信号S2との差動増幅信号S3を生成する差動増幅器1と、差動増幅信号S3のADコンバータ101と、センサ低速信号S4のADコンバータ102と、ローパスフィルタ2から基準信号記憶器3への信号路を開閉するスイッチ4と、ローパスフィルタ2からADコンバータ102へのチャンネルを選択する選択器103と、選択チャンネルを決定する選択決定器202と、基準信号S11と差動増幅信号S7とからセンサ物理量S9を計算する換算器201とを備えている。

(もっと読む)

アナログデジタル変換器及びアナログデジタル変換方法、並びに撮像装置及びその駆動方法

【課題】消費電力の低減を実現することができるアナログデジタル変換器を提供する。

【解決手段】第1のコンパレータ7で、先のタイミングでAD変換を行なったアナログ信号と後のタイミングでAD変換を行なうアナログ信号の大小関係を比較し、比較結果に基づいてDAC3によってダウンカウント若しくはアップカウントのランプ波を出力する。また、比較結果に基づいて、カウンタ制御部8によって昇順若しくは降順にカウントを行なう様にカウンタ5を制御する。カウンタ5では、先のタイミングでAD変換を行なったアナログ信号と後のタイミングでAD変換を行なうアナログ信号との差分のみをカウントする。

(もっと読む)

数ギガビットアナログ−デジタル変換器

高速で動作するためのアナログ−デジタル変換器は、マイクロコンパレータ/サンプラ、符号器、および選択器を有して実装されることができる。マイクロコンパレータは、受信機/送受信機システムのアンテナからの入力と、トランジスタ対と、リセットトランジスタと、縦続接続されたインバータと、インバータ回路と、バッファと、Dフリップフロップ回路とを含む。並列に設置されたマイクロコンパレータ/サンプラの数に応じて、多数のビットを生成することができる。例えば、15個の異なるマイクロコンパレータ/サンプラからの15個のビットを、15ビットから4ビットへの符号器へ挿入して、4つのビットを生成することができる。  (もっと読む)

(もっと読む)

AD変換装置及びAD変換方法

【課題】アナログ・デジタル変換においてBGR回路による基準電圧を利用する際にアンプのオフセット電圧に影響されないAD変換装置を提供する。

【解決手段】AD変換装置において、バンド・ギャップ・リファレンス回路は、基準電圧に応じて温度依存性を有する素子に現れる電圧を入力電圧とし基準電圧を出力するオペアンプと、オペアンプの反転入力と非反転入力とを入れ替える状態及び入れ替えない状態を切り替え可能な第1のスイッチ回路と、オペアンプの出力電圧を正相で出力する状態及び逆相で出力する状態を切り替え可能な第2のスイッチ回路とを含み、基準電圧を利用するAD変換回路は、第1及び第2のスイッチ回路を所定の状態に設定して第1のデジタル値を求め、第1の及び第2のスイッチ回路を所定の状態とは逆の状態に設定して第2のデジタル値を求め、第1及び第2のデジタル値の平均値としてAD変換結果を求める。

(もっと読む)

固体撮像装置

【課題】ラッチ回路のレイアウトサイズを小さくし、カラムADC回路のレイアウトサイズを小さくする。

【解決手段】カラムADC回路は、画素アレイの各列に対応して設けられ、垂直走査回路により選択された行の画素信号を読み出し、読み出した画素信号を上位ブロック及び下位ブロックの2つのブロックに分けて順次にAD変換する。そして、カラムADC回路のラッチ回路40を、上位ブロックと下位ブロックとのうちビット数が大きい方のブロックのデジタルデータが格納可能な記憶容量のラッチ回路で構成する。

(もっと読む)

デジタル・アナログ変換回路、固体撮像装置、カメラシステム及びデジタルコードのアナログ変換方法

【課題】D/A変換器の消費電流増加を避けながら、イメージでの横筋状のノイズ低減に有効なD/A変換技術を提案する。

【解決手段】基準電圧をドライバから出力するレギュレータと、そのレギュレータから出力される基準電圧が供給されて、入力したコードに応じたアナログ電圧を出力するアナログ電圧出力部とを備えた構成とする。そして、レギュレータ内のドライバのサイズを、入力したコードに応じて可変させる制御を行う。このようにしたことで、ドライバのゲート電圧が再調整などによって変化することが抑制され、レギュレータに求められる過渡応答特性を下げることが可能となる。

(もっと読む)

撮像装置

【課題】撮像信号を高精度に検出することができる撮像装置を提供する。

【解決手段】A/D変換部11は、画素10aからの出力信号の大きさに応じた周波数を有するクロックをカウントし、デジタル化してカウント値を生成すると共に、画素10aのリセット期間の出力信号に係る第1のカウント値と、画素10aの露光期間の出力信号に係る第2のカウント値との差分を演算して当該画素10aの撮像信号として出力する。制御部12は、A/D変換部11に対し、画素10aのリセット期間及び露光期間の出力信号を連続する略等しい複数の小期間の各々においてカウントさせ、小期間毎のカウント値の内、他の小期間のカウント値との差分が所定の変動幅に収まる小期間のカウント値を加算して、それぞれ第1のカウント値及び第2のカウント値とさせるように制御する。

(もっと読む)

角度検出AD変換器及びAD変換方法

【課題】逐次比較法に基づいて2次元アナログ信号から角度成分を検出するにあたり、角度検出AD変換回路内のオフセットに起因して発生する精度劣化をキャンセルすること。

【解決手段】互いに直交して回転体に配設された2つの磁気センサからの2次元入力信号及び第1の角度に対応する正弦及び余弦に基づいて算出した出力信号を基準値と比較して得た比較結果に従って第1のビットを算出する。2次元入力信号及び正弦及び余弦の極性を反転させた値に基づいて算出した出力信号を基準値と比較して得た比較結果に従って第2のビットを算出する。2次元入力信号及び第2の角度に基づいて算出した第3の出力信号を基準値と比較して得た比較結果に従って第3のビットを算出する。第1のビットが第2のビット及びが第3のビットと異なるか否か判定する。

(もっと読む)

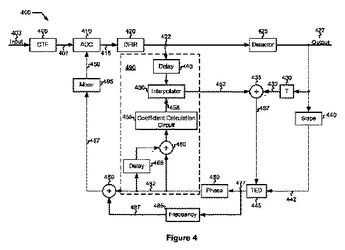

データ検出器フィードバックループにおいて遅延を軽減するためのシステム及び方法

本発明の種々の実施例はデータ検出器フィードバックループにおける遅延を軽減するためのシステム及び方法を提供する。その方法は、デジタルサンプルを生成するために或るサンプリングインスタントにおいてアナログ−デジタル変換を実行するステップ、及び検出出力を生成するためにデジタルサンプルに対してデータ検出を実行するステップを含む。検出された出力は、位相エラーを特定するためにデジタルサンプルに比較される。一時的期間中に、デジタルサンプルは位相エラーを反映して調整デジタルサンプルを生成するために調整される。一時的期間後に、位相エラーを反映するためにサンプリングインスタントが調整される。  (もっと読む)

(もっと読む)

信号処理回路および電子内視鏡システム

【課題】アナログ信号の歪や、減衰、レベル変動が生じても、サンプリングパルスの位相を最適に調整し、出力信号の精度を確保することができる信号処理回路を提供する。

【解決手段】サンプリングパルス生成部5は、基準レベル部と、信号電荷に応じた信号レベル部とを有するアナログ信号のサンプリングに用いるサンプリングパルスを生成する。アナログ/デジタル変換部2は、サンプリングパルスに従ってアナログ信号の基準レベル部と信号レベル部とを各々複数回サンプリングし、各サンプリング値を標本化する。評価値演算部3は、アナログ/デジタル変換部2から出力された複数のサンプリング値に基づいて評価値を演算する。パルス位相制御部6は、評価値に基づきサンプリングパルスの位相を制御する。

(もっと読む)

スキャンタイプAD変換方法、スキャンタイプAD変換システム

【課題】サンプルジッターを低減したスキャンタイプのAD変換方法、及びスキャンタイ

プのAD変換システムを提供する。

【解決手段】マイコン72の制御により、パラレルに接続された複数のセンサ12から入

力されるアナログ信号を遂次的にAD変換器16でAD変換し、シリアルデータ32に変

換して出力するスキャンタイプのAD変換である。マルチプレクサ14により前記複数の

センサを遂次的に選択し、遂次的に入力される前記アナログ信号をAD変換するシーケン

サ18によるシーケンス制御を周期的に行う。前記シーケンサ18は、マイコン18から

出力されるクロックをクロック源として駆動し、前記シリアルデータ32は、前記マイコ

ン72内のシリアルインターフェース76に入力される。

(もっと読む)

同時サンプリング型のAD変換方法、同時サンプリング型のAD変換システム

【課題】サンプルジッターを低減した同時サンプリング型のAD変換方法、及びAD変換

システムを提供する。

【解決手段】マイコン制御により、複数のアナログ信号を同時に複数のAD変換器14に

よりAD変換し、シリアルデータ化して出力する同時サンプリング型のAD変換方法であ

って、前記AD変換により得られる複数のデジタルデータ20をシフトレジスタ26によ

り遂次的に出力させ、前記複数のデジタルデータ20をシリアルデータ化して出力するシ

ーケンス制御をシーケンサ34が周期的に行う。

(もっと読む)

演算処理装置及び演算処理方法

【課題】安価なマイクロコンピュータであっても、ノイズの発生による影響を回避して、適切なタイミングで信号の変換入力が可能な演算処理装置を提供する。

【解決手段】信号端子AF+に入力された信号を変換指令に基づいてA/D変換するA/D変換部31aと、A/D変換された信号データを入力し、信号データと閾値を比較して、その結果に基づいて所定の制御信号を出力する信号出力部31bと、信号データに基づいて閾値を調整する閾値算出部31cを備え、信号出力部31bはA/D変換された信号データを入力した後、制御信号S2を出力する前に、A/D変換部31aに次のA/D変換のための変換指令を出力する。

(もっと読む)

アナログ入力データの温度補正装置

【課題】複雑な補正操作を行うことなく、また、高価な温度特性のよいオペアンプやA/D変換器をもちいることなく、データの精度を高める。

【解決手段】制御対象から入力されるアナログ入力信号をデジタル信号に変換して出力するアナログ入力部12と、装置回りの周囲温度を検出する温度検出器18と、温度が異なる条件下で、前記デジタル信号のデジタル値とアナログ入力信号の期待値との間に生じる誤差との実測定に基づいて作成され、周囲温度と補正値とが一対一に対応付けられた補正データが格納された温度補正テーブル24と、温度検出器で検出した温度に対応する補正値を温度補正テーブル24から読み込み、アナログ入力回路12から読み込んだデジタル値を前記補正値で補正し、最終的なデジタルデータとする温度補正手段16を設ける。

(もっと読む)

光量デジタル変換回路、IC、および電子機器

【課題】各誤差要因に依存しない光量の測定を行い、高精度なデジタル変換を行う。

【解決手段】光量に応じて光電流を出力するPD101と、参照電流を出力する定電流源102と、第1制御信号に基づいて光電流を選択するとともに、第2制御信号に基づいて参照電流を選択するセレクタ103と、光電流または参照電流の大きさに応じた周波数のクロック信号を作成するI−F変換回路104と、クロック信号のパルスをカウントするカウンタ105と、第1制御信号および第2制御信号をセレクタ103に出力するコントロール部108と、参照電流を基に作成されたクロック信号に対して、所定のパルス数がカウントされた時間を計測し、そのM倍(M:正の定数)を基準時間として保持する時間計測装置107と、光電流を基に作成されたクロック信号に対して、上記基準時間にカウントされたパルス数に基づいてデジタル値を作成するレジスタ106と、を備えている。

(もっと読む)

信号処理装置

【課題】交流電源の周期数に拘わることなく一定のサンプリング周期で入力信号を取り込んで電源周期数に起因するコモンモードノイズを除去し得る簡易な構成の信号処理装置を提供する。

【解決手段】A/D変換手段においては、演算処理手段に設定された一動作周期内において、第1の入力信号を電源周波数に応じて定められる回数に亘って繰り返しサンプリングすると共に、第2の入力信号を少なくとも1回サンプリングし得る一定の周期で前記第1および第2の入力信号をそれぞれデジタル変換し、平均化処理手段においては前記電源周波数に応じて定められる回数に亘って繰り返しサンプリングされた前記第1の入力信号のデジタル変換値の平均値を求める。

(もっと読む)

121 - 140 / 238

[ Back to top ]