Fターム[5J022CF10]の内容

アナログ←→デジタル変換 (13,545) | 周辺・部分回路構成 (2,714) | 信号検出トランスジューサ (238)

Fターム[5J022CF10]に分類される特許

221 - 238 / 238

センサ信号処理回路装置

【課題】出力信号がON/OFFのセンサのみならず、アナログ信号のセンサも併せてハーネスを少なくし得るセンサ信号処理回路装置を提供する。

【解決手段】ON/0FFの検出信号を出力する複数のセンサの各検出信号を、各検出信号が入力される記憶部を持つ記憶回路42,43,45に記憶し、またアナログの検出信号を出力するセンサの検出信号をA/D変換器48A、48B、でデジタル信号に変換して記憶回路49A,49Bに記憶し、これら記憶回路42、・・・、49Bに記憶したパラレルのデジタル信号をシリアルOUT回路46で、シリアルデータに変換し、シリアルデータ伝送路13、26を介してメインコントロール部3に伝送する。

(もっと読む)

AD変換器の故障検出装置

【課題】簡単な回路構成で製造コストの上昇につながらないAD変換器の故障検出装置を提供する。

【解決手段】アナログ信号電圧を入力するための3チャンネル以上の入力端子を有し、アナログ信号電圧をデジタル信号値にAD変換するAD変換器において、AD変換後の値が予め定められた所定の関係になるように、少なくとも2点の電圧値を設定する設定手段と、少なくとも2点の電圧値のAD変換値から少なくとも2点の電圧値の関係を求める算出手段と、算出された少なくとも2点の電圧値の関係と所定の関係とを比較し、両者の差が所定の値を超えた場合にAD変換器の故障と判定する故障検出手段と、を備えることを特徴とするAD変換器の故障検出装置として実現可能である。

(もっと読む)

AD変換器の故障検出装置

【課題】簡単な回路構成で製造コストの上昇につながらないAD変換器の故障検出装置を提供する。

【解決手段】アナログ信号電圧を入力するための少なくとも一つの入力端子を有し、アナログ信号の電圧値をデジタル信号値にAD変換するAD変換器と、アナログ信号のAD変換値に、パリティビットを付加するパリティ演算部と、アナログ信号のAD変換値およびパリティビットを記憶する変換結果記憶部と、変換結果記憶部からAD変換値を読み出すとともにパリティビットの整合性を調べ、パリティビットの不整合があった場合にAD変換器の故障と判定する故障検出手段と、を備えたことを特徴とするAD変換器の故障検出装置として実現可能である。

(もっと読む)

アナログデジタル変換器

【課題】AD変換ブロックに入力されるアナログ信号をサンプルして少なくとも保持するための回路に入力される信号のセトリングタイムは、遅延しがちであった。

【解決手段】アナログデジタル変換器3において、AD変換回路18は、アナログ信号をサンプルし、目標ビット数より少ない所定ビット数のデジタル値に変換する。増幅回路16は、AD変換回路18と並列に設けられ、AD変換回路18がサンプルするアナログ信号を保持、または所定の増幅率で増幅する。サンプルホールド回路10の出力側に、増幅回路16用の第1ソースフォロワ回路12と、AD変換回路18用の第2ソースフォロワ回路14を個別に設けた。

(もっと読む)

走査形プローブ顕微鏡及びD/Aコンバータ

【課題】漏れ信号の少ないDAコンバータを提供する。

【解決手段】抵抗値Rの抵抗18a,18b,18cと抵抗値2Rの抵抗19a,19b,19c,19d,19eから成り、基準電圧Vrefを分割する様に成したR−2R型ラダー抵抗網、入力信号であるデジタル信号の各ビット毎に設けられ、抵抗値2R抵抗の抵抗値R抵抗と接続されていない端部をアース若しくは演算増幅器OAの反転入力端子の何れかに切り換える切換スイッチを備え、切換スイッチは2段構えとし、1段目の切換スイッチは、前記抵抗値2R抵抗の抵抗値R抵抗と接続されていない端部をアース若しくは2段目の切換スイッチの何れかに切り換える様にし、2段目の切換スイッチはアース若しくは演算増幅器OAの反転入力端子の何れかに切り換える様に成す。

(もっと読む)

信号処理装置

【課題】 共通の信号発生源からのアナログ信号が複数のマイクロコンピュータに入力される場合に、信号ラインにインピーダンス変換素子やノイズ吸収用のコンデンサを設けなくとも、正確に信号を入力できる信号処理装置を提供する。

【解決手段】 共通の信号発生源からのアナログ信号をデジタル信号に変換するA/D変換処理部を有し、前記A/D変換処理部で変換処理されたデジタル信号を入力して所定の処理を実行するマイクロコンピュータが前記共通の信号発生源に対して複数設けられる信号処理装置であって、前記マイクロコンピュータの少なくとも一つに、他のマイクロコンピュータからの入力許容信号を受けて前記A/D変換処理部を駆動する受動入力制御を実行する信号入力制御部と、他のマイクロコンピュータに対して前記A/D変換処理部の駆動を許容する入力許容信号を出力する信号出力制御部を設ける。

(もっと読む)

材料試験機

【課題】 試験力や伸び等の複数の検出出力をそれぞれA−D変換する材料試験機において、その材料試験機が有しているA−D変換用のチャンネル数を無駄なく活かした設定を可能とする。

【解決手段】 A−D変換器22,23として、複数のチャンネルを備え、かつ、外部からの選択信号により各チャンネルの使用/不使用状態を選択できるとともに、使用チャンネル数がサンプリングレート/精度とトレードオフとなっているものを用い、その各A−D変換器22,23に対して各チャンネルの使用/不使用の選択信号を供給する選択手段(操作部2a)を設けることにより、材料試験機が有しているA−D変換用チャンネル数と、ユーザーが実際に使用するA−D変換チャンネル数との関連により、少ないチャンネル数でよい場合には高速・高精度のA−D変換を行うなど、チャンネル数とサンプリングレートまたは精度のうち、どちらを優先させるか等をユーザーサイドで選択可能とする。

(もっと読む)

医用画像のためのデータ収集システム

【課題】アナログ信号(40)をデジタル信号に変換するシステムおよび方法を提供する。

【解決手段】本技術は、サンプリングされたアナログ信号を受け取り、DAC出力値と所望のADC入力値との間のセグメント化された関係(64)の複数のセグメント(66、70、72、74、76、および78)のうちの1つを選択するものである。選択されたセグメントに基づいて、所望のゲインおよびオフセット値がDAC出力値またはサンプリングされたアナログ信号に適用される。サンプリングされたアナログ信号は、所望のゲインおよびオフセット値に基づいてデジタル信号に変換される。

(もっと読む)

アナログ信号計測装置、および、アナログ信号計測方法

【課題】 センサの温度ドリフトや外来ノイズの影響により出力信号が大きく変動して飽和することを防ぎ、安定した測定を行うこと。

【解決手段】 オフセット成分11を加減算して測定されたアナログ入力信号10をA/Dコンバータ2によりデジタルの出力信号13に変換し、オフセット成分を更新する条件が満たされている場合にはA/Dコンバータ2から出力された出力信号13をもとに、新たにオフセット成分を算出し、その算出されたオフセット成分を更新する。

(もっと読む)

半導体装置

【課題】

供給される基準電圧に応答して、入力されるアナログ信号をAD変換してデジタルデータを出力する半導体装置において、その基準電圧が変動するときでも、その電圧変動の影響を受けることのないデジタルデータを生成する半導体装置を提供する。

【解決手段】

基準電圧を生成する基準電圧生成回路と、その基準電圧に応答して、センサから出力される出力電圧をAD変換するAD変換回路とを具備する半導体装置を構成する。そして、その基準電圧生成回路は、基準電圧に対応するセンサ用電圧を生成して、そのセンサ用電圧をセンサ用電圧出力端子を介してセンサに供給する。

(もっと読む)

AD変換回路および固体撮像装置

【課題】 アナログ信号のレベルを検出できない場合でも、アナログ信号をデジタル信号に正しく変換でき、異常なデジタル信号が出力されてしまうような事情を抑制すること。

【解決手段】 AD変換回路は、アナログ信号のレベルが基準信号のレベルより低い場合に、このアナログ信号を第1の固定レベルのデジタル信号に変換する第1のレベル固定回路、及びアナログ信号のレベルが基準信号のレベルより高い場合に、このアナログ信号を第2の固定レベルのデジタル信号に変換する第2のレベル固定回路の少なくともいずれか一つを含む。

(もっと読む)

差動シリアル・ディジタル出力A/D変換手段および撮像装置

【課題】多線読出しセンサを用いた撮像装置において、AD変換後にディジタル信号処理プロセッサまでの基板内配線数を減らすことによって、装置内部でのノイズ発生量を抑圧し、センサからADまでのアナログ信号系にフィードバックするキックバックノイズを減少させる。

【解決手段】結果的にディジタル信号の配線数を減らすことによって、アナログ・フロント・エンドLSIや基板の面積を小さくする。

(もっと読む)

複数のDACを備えているマルチチャンネル集積回路、およびDACの出力を監視するための方法

マルチチャンネル回路(1)は、複数のオンチップチャンネル(CH1からCH4)を備えていて、それらの各々は、インターフェース及び制御論理回路(11)の制御下で、互いに別々に、デジタルデータをアナログ出力信号に変換するためのDAC(3)を備えている。DAC(3)からのアナログ出力信号は、それぞれのチャンネル(CH1からCH4)の出力端子(7)に出力される。デジタル入力データと、DAC(3)内のデジタルデータの変換を制御するための制御及びアドレス信号とが、I/Oポート(10)を通して、インターフェース及び制御論理回路(11)に入力される。DACレジスタ(9)が、それぞれのチャンネル(CH1からCH4)に設けられていて、対応するDAC(3)で変換されるべきデジタルワードを格納する。アナログ入力端子(20)が設けられていて、アナログ入力信号、例えば、DAC(3)からの出力信号によって制御可能な外部システムからのアナログ信号を受信する。マルチプレクサ(15)は、インターフェース及び制御論理回路(11)の制御下で操作可能であり、DAC(3)からのアナログ出力信号と、アナログ入力端子(20)からのアナログ入力信号とを、監視出力端子(16)に、選択的かつ順次的に加えて、DAC(3)からのアナログ出力信号と、アナログ入力端子(20)上のアナログ入力とを別々に監視することを容易にする。  (もっと読む)

(もっと読む)

データ処理方法およびデータ処理装置並びに物理量分布検知の半導体装置および電子機器

【課題】AD変換装置を同一チップ上に搭載した固体撮像装置において、回路規模や伝送信号線の数をコンパクトにしつつ、積和演算処理も効率的にできるようにする。

【解決手段】n行の読出期間の画素信号と、この画素信号をデジタル化する参照信号とを比較するとともに、この比較処理と並行してダウン/アップの何れかのモードでカウント処理を行ない、比較処理が完了した時点のカウント値を保持する。次に、このn行のカウント処理結果を初期値として、n+1行の読出期間の画素信号と、この画素信号をデジタル化する参照信号とを比較するとともに、ダウン/アップの何れかのモードでカウント処理を行ない、比較処理が完了した時点のカウント値を保持する。n+1行のカウント処理後のカウント値は、n+1行のカウント処理のモードをn行におけるカウントモードと逆にすれば減算結果となり、同じにすれば加算結果となる。

(もっと読む)

オプトエレクトロニック送受信機におけるアナログ・ディジタル変換信号処理

オプトエレクトロニック送受信機の動作監視回路は、オプトエレクトロニック送受信機の一つまたは複数の動作状態を表わすアナログ入力信号を処理しディジタル信号結果を生成するための一連の相互接続された信号処理回路を含む。一連の信号処理回路は、アナログ入力信号を利得値により増幅または減衰してスケーリングされたアナログ信号を生成する利得回路、スケーリングされたアナログ信号を第1のディジタル信号に変換するアナログ・ディジタル変換器、および第1のディジタル信号をディジタル的に調整してディジタル信号結果を生成するディジタル調整回路を含む。ディジタル調整回路は、ディジタルシフト信号を生成するために、入力ディジタル信号をシフト値に従ってシフトするように構成されたシフト回路を含む。ディジタル信号結果は、ホストによりアクセス可能な所定の場所の記憶装置に格納される。

(もっと読む)

(もっと読む)

信号のダイナミックレンジを増加するための複数の信号利得を有するデータ信号増幅器及びプロセッサ

【解決手段】信号のダイナミックレンジを増加するための複数の信号利得を有するデータ信号増幅及び処理回路が与えられる。入力データ信号は複数の信号利得に従って処理される。生成された信号は複数の信号値を有し、所定の下側及び上側閾値と比較される。所望の出力信号は、最大値が所定の下側閾値を横切らない場合には最大サンプル信号値であり、複数のサンプル信号値の内の隣接する大きいものが所定の上側閾値を横切る場合には最小サンプル信号値であり、一対のサンプル信号値の大きい方が所定の上側閾値を横切りかつ小さい方の値が所定の下側閾値を横切らない場合には複数のサンプル信号値の内の相互に隣接する一対の小さい方であり、大きい方の値が所定の下側閾値を横切りかつ所定の上側閾値を横切らない場合には一対のサンプル信号値の小さい方と大きい方との組み合わせである。 (もっと読む)

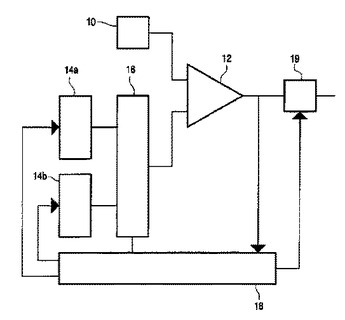

電子的センシング回路

センサ(10)は、第1の比較器入力端に結合される出力端を有する。制御回路(18)は、上方向追跡モードから、下方向相対レベル検出モード、下方向追跡モード、上方向相対レベル検出モード、そして再び上方向追跡モードに、次々に切り換わるように構成される。第1および第2のディジタル・アナログ変換回路(14a、b)は、制御回路(18)からそれぞれ第1および第2のディジタル制御値を受け取る。制御可能コンバイナ回路(16)は、第1および第2のディジタル・アナログ変換回路(14a、b)の出力端に結合された入力端と、第2の比較器入力端に結合された出力端とを有し、制御回路(18)は、コンバイナ回路(16)が、上方向および下方向追跡モードではそれぞれ第1および第2のディジタル・アナログ変換回路(14a、b)によって決まる第1および第2のコンバイナ出力信号を第2の比較器入力端に供給し、相対レベル検出モードでは第1および第2のコンバイナ出力信号の平均値に対応する第3のコンバイナ出力信号を第2の比較器入力端に供給させるために、制御可能コンバイナ回路(16)に結合された、第1の出力端を有する。制御回路(18)は比較器(12)の出力端に結合された入力端を有し、制御回路(18)は、上方向追跡モードでは、第1のディジタル・アナログ変換回路(14a)による、センシング信号の上方向変化に対する一方向性の上方向追跡を制御し、上方向追跡モードでは、第2のディジタル・アナログ変換回路(14b)による、センシング信号の下方向変化に対する一方向性の下方向追跡を制御する。  (もっと読む)

(もっと読む)

測定量検出のための電子回路

本発明は、アナログ測定信号を用意するための少なくとも1つのセンサ装置とアナログ測定信号のデジタル化のための第1のアナログ/デジタル変換器を備えている信号検出装置とを備えている電子回路に関する。センサ装置および信号検出装置に給電する給電電圧の変動の差異は基本的に測定信号中の所望しない変動の形において現れる。

この作用効果を最小限にするまたは補償するために、本発明によれば、第1の給電電圧(VS1)の不正確さx1を表している電圧信号(U)に応答してデジタル化された測定信号を補正することが提案される。  (もっと読む)

(もっと読む)

221 - 238 / 238

[ Back to top ]