Fターム[5J023CB01]の内容

遅延要素を用いたフィルタ (1,075) | 目的 (151) | 特性改善・可変 (109)

Fターム[5J023CB01]の下位に属するFターム

Fターム[5J023CB01]に分類される特許

1 - 20 / 34

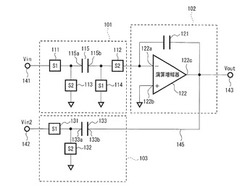

スイッチドキャパシタ積分器

【課題】演算増幅器の充電にかかる負荷を抑え、低消費電力化を実現できるスイッチドキャパシタ積分器を提供する。

【解決手段】演算増幅器122を含む積分器102、演算増幅器122の入力端子122aに信号を入力するスイッチドキャパシタ回路101、演算増幅器122の出力端子122cと接続する出力端子443を有するスイッチドキャパシタ回路103を含み、積分器102及びスイッチドキャパシタ回路101がサンプリング動作と積分動作とを繰返し、スイッチドキャパシタ回路103は、キャパシタ133、キャパシタ133をサンプル、ホールド動作させるスイッチング素子131、132を含み、スイッチング素子131、132がキャパシタ133を、積分動作中にホールド動作させる。

(もっと読む)

スイッチトキャパシタ回路

【課題】システムの性能劣化を避けつつ、システムの消費電力を低減する。

【解決手段】コンデンサC1と、コンデンサC1の入力側及び出力側にそれぞれ設けられたスイッチSW1〜SW4と、コンデンサC1の出力を受ける後段のオペアンプ204とを備え、スイッチSW1〜SW4の少なくとも一つの開閉状態に応じてオペアンプ204へ供給される電流値を切り替える。

(もっと読む)

時定数調整回路

【課題】参照用の時定数発生回路を集積回路の外部に用意すると、集積回路の端子数の増加および半導体チップ面積の増大を招き、その結果、製造コストが増大してしまう。また、集積回路単体では時定数の調整を行えない。

【解決手段】スイッチトキャパシタを用いることで、時定数発生回路を集積回路に内蔵しても十分な精度が保たれる。さらに、時定数の補正結果を記憶する記憶部を設けることで、時定数調整用回路と、時定数調整後の通常動作用回路を、一部兼用することが可能となる。集積回路の端子数と、半導体チップ面積を節約でき、その結果、製造コストを抑えられる。さらに、外部から電源さえ供給されれば、自動的かつ自律的に時定数の調整を行える。

(もっと読む)

離散時間受信機

【課題】本発明は離散時間受信機に関する。

【解決手段】本発明の離散時間受信機は、サンプリングクロックに応じて入力信号をサンプリングするサンプリングミキサと、制御信号を用いてデシメーション比を調節し、フィルタクロックを用いて上記サンプリングされた信号をフィルタリングする離散時間フィルタと、上記サンプリングミキサに供給されるサンプリングクロックを生成し、上記サンプリングクロックの周波数と予め設定された出力周波数とを比較して制御信号及びフィルタクロックを生成するクロック生成器と、を含み、広帯域の入力信号に対して出力信号のダイナミック範囲を向上させることができる。

(もっと読む)

フィルタ装置

【課題】アンチエイリアシングフィルタを搭載することなく、サンプリング周波数近傍のエイリアシングを減衰することができる小型のフィルタ装置を得ることを目的とする。

【解決手段】Clock11〜14に同期して、I信号をサンプリングして、そのI信号の帯域を制限するサンプリングフィルタ10と、Clock11〜14と4分の1周期ずれているClock21〜24に同期して、そのI信号と直交しているQ信号をサンプリングして、そのQ信号の帯域を制限するサンプリングフィルタ11とを設け、合成部12がサンプリングフィルタ10により帯域が制限されたI信号とサンプリングフィルタ11により帯域が制限されたQ信号を合成する。

(もっと読む)

フィルタ回路及び通信装置

【課題】電荷の移動に伴う過渡現象が出力に与える影響を抑止すること。

【解決手段】入力端に入力された電圧信号を電流信号に変換するトランスコンダクタンスアンプ102と、複数のキャパシタから構成され、トランスコンダクタンスアンプ102から出力された電流信号が周期毎に各キャパシタへ順次に入力されるキャパシタ集合体と、電流信号が入力された1群のキャパシタを互いに接続し、当該1群のキャパシタに蓄積された電荷を加算するシェアスイッチS1aS〜S4aS,S1bS〜S4bSと、シェアスイッチS1aS〜S4aS,S1bS〜S4bSにより電荷が加算された後、1群のキャパシタのうちの少なくとも1つのキャパシタを出力端に接続するダンプスイッチS1aD〜S4aDと、を備える。

(もっと読む)

スイッチトキャパシタフィルタ回路

【課題】インバータにより反転増幅回路を構成したスイッチトキャパシタフィルタ(SCF)回路では、出力信号のオフセット電位が変動しやすい。

【解決手段】SCF回路2は、出力段にインバータ回路14a,14bを有した2つのSCF4,6を備え、差動形式の出力信号を生成する。差動出力端子間に接続した抵抗RA,RBは差動信号を分圧し、中点電位VCMを生成する。比較器30は、VCMと目標電位VCTとを比較する。インバータ回路14a,14bのCMOSインバータと接地電位との間に接続されたトランジスタは、比較器30での比較結果に応じてチャネル抵抗を変化させ、CMOSインバータの出力端のバイアス電位を変化させ、オフセット電位をVCTへ向けてフィードバック制御する。

(もっと読む)

スイッチトキャパシタ回路を用いた積分回路、ローパスフィルタおよび電子機器

【課題】 カットオフ周波数が極めて低いスイッチトキャパシタ積分回路(SC積分回路)を、SC回路のキャパシタ(入力容量)およびオペアンプの帰還容量の容量値の比(Cp/Ci:容量素子係数)を極端に小さくすることなく、高精度に実現すること。

【解決手段】 積分回路の入力部170において、第1の入力回路(第1のスイッチトキャパシタ回路)10と、第2の入力回路(第2のスイッチトキャパシタ回路)11と、積分部61とを設ける。SC積分回路150の等価的な伝達関数をH(z)とするとき、{αH(z)−(α−X)H(z)}で表わされる信号処理を実行する。すなわち、信号伝送路において電荷の減算を実行し、キャパシタの容量値を、見かけ上、小さくし、現実的なサイズのキャパシタを用いて、カットオフ周波数が極めて低いSC積分回路を構成する。

(もっと読む)

フィルタ回路および通信装置

【課題】フライングキャパシタを備え、急峻な減衰特性を備えた上でさらにQ値を可変にすることが可能なフィルタ回路の提供。

【解決手段】入力端から出力端へ切り替わる場合には極性を維持し、出力端から入力端へ切り替わる場合には極性が反転するフライングキャパシタと、フライングキャパシタの入力端にフライングキャパシタと並列に設けられる第1のキャパシタCh1と、フライングキャパシタの出力端にフライングキャパシタと並列に設けられる第2のキャパシタCh2と、を備え、フライングキャパシタは、出力端から入力端へ切り替わってから所定の時間遅延して入力端から出力端へ切り替わり、入力端から出力端へ切り替わってから所定の時間遅延して出力端から入力端へ切り替わる、フィルタ回路。

(もっと読む)

フィルタ回路および通信装置

【課題】チャージドメイン2次IIR−LPFの周波数特性におけるゲインを向上させることが可能なフィルタ回路を提供する。

【解決手段】入力端から出力端へ切り替わる場合には極性を維持し、出力端から入力端へ切り替わる場合には極性が反転するフライングキャパシタと、フライングキャパシタの入力端にフライングキャパシタと並列に設けられる第1のキャパシタと、フライングキャパシタの出力端にフライングキャパシタと並列に設けられる第2のキャパシタと、を備え、フライングキャパシタは、入力端から出力端へ切り替わる場合には容量が小さくなり、出力端から入力端へ切り替わる場合には容量が大きくなる可変容量素子を含む、フィルタ回路が提供される。

(もっと読む)

サンプルホールド回路

【課題】キャパシタを用いたサンプルホールド回路において、サンプリング時におけるキャパシタの充電状態をホールド状態とするためにオフされるべきスイッチにリーク電流が生じる。

【解決手段】サンプルホールド回路10は、オペアンプ12の反転入力端子IN−に一方端を接続されたキャパシタC1にサンプリング電圧に応じた電荷を蓄積する。その際、C1のIN−側の端子はスイッチ回路14を介して出力端子VOUTに接続し、所定電位に設定する。ホールド状態ではスイッチ回路14はオフされ、それが接続されたC1の端子をフローティング状態とする。スイッチ回路14は、IN−とVOUTとの間に直列に接続され同相でオン・オフされるMOSトランジスタスイッチS11,S12と、それら相互の接続点と接地電位との間に接続されたキャパシタC2とからなる。

(もっと読む)

ローパスフィルタおよび半導体圧力センサ装置

【課題】カットオフ周波数が低い場合であっても、電源オンの後速やかに出力を安定させる。

【解決手段】電源オンから整定化時間Tsが経過するまでは、フィルタ動作有効化信号φ3をオフにするとともに第1相、第2相クロックパルスφ1、φ2をともにオンにして、アナログスイッチS11〜S26をオン、アナログスイッチS37をオフにする。整定化時間Tsが経過した後は、フィルタ動作有効化信号φ3をオンにするとともに第1相、第2相クロックパルスφ1、φ2を互いにオン期間が異なるように2相動作させ、スイッチトキャパシタフィルタとして動作させる。

(もっと読む)

プログラム可能な信号帯域を有する回路およびその方法

【課題】広帯域信号の受信に適用できるだけでなく、異なる周波数帯の受信信号に関し、複数の制御信号によって周波数応答の帯域幅をプログラムすることが可能な回路を提供する。

【解決手段】回路は、第1の充放電デバイス803、第1のリセットデバイス804、および、第1の可変コンデンサデバイス805を含む。第1のリセットデバイス804は、第1の充放電デバイス803に結合され、第1の可変コンデンサデバイス805は、第1の充放電デバイス803に結合される。第1のリセットデバイス804は、放電イネーブル信号により制御され、第1の放電経路を提供する。放電イネーブル信号が第1のリセットデバイス804をオフにすると、第1の可変コンデンサデバイス805は、n個の基準信号に従い第1の充放電デバイス803に対し第1の総等価コンデンサを生成し、nは、0より大きい整数である。

(もっと読む)

フィルタ装置

【課題】少ないタップ数で急峻な特性を持つスイッチドキャパシタフィルタ装置を提供する。

【解決手段】正極性選択スイッチ1311−1354と、負極性選択スイッチ1411−1454と、正極性読み出しスイッチ1711−1754と、負極正読み出しスイッチ1811−1854と、タイミング制御部5とを備える。書き込み時の極性と読み出し時の極性を同一もしくは異なるように制御することによって、負の電荷を読み出すことを可能にし、フィルタの重み付け係数として負の係数を設定することを実現することによって、急峻な特性をもつFIRフィルタを提供する。

(もっと読む)

離散フィルタ、サンプリングミキサ及び無線装置

【課題】デシメーション数を小さくしても、高い周波数のREF信号を必要としない回路構成のサンプリングフィルタを提供すること。

【解決手段】4並列に構成されたCr7a〜7dを含んだスイッチドキャパシタ回路のそれぞれのローテートキャパシタが、同じタイミングでは互いに異なる積分、放出、リセット、フィードバックの4相で動作し、スイッチドキャパシタ回路を駆動する制御信号を共用化することで、DCU104の回路規模を削減し、デシメーション無しの動作においてもREF信号の周波数をLO信号と同じ周波数まで低くすることができる。

(もっと読む)

チャージドメインフィルタ回路

【課題】低消費電力で動作可能であり、フィルタ特性がリコンフィギュアラブルである、チャージドメインフィルタ回路を提供すること。

【解決手段】所定の間隔でサンプリングされる第1の信号を出力する第1の信号出力手段と、第1の信号からサンプリング間隔のn倍(nは自然数)遅れて、かつ連続したタイミングでサンプリングされる第2の信号を出力する少なくとも1つの第2の信号出力手段と、第2の信号出力手段において時間的に後にサンプリングが行われる一つの第2の信号からサンプリング間隔のn倍遅れたタイミングでサンプリングされる第3の信号を出力する第3の信号出力手段と、第1の信号、第2の信号、および第3の信号を加算して出力する加算手段と、を含み、第1の信号出力手段と第2の信号出力手段とに備えられるサンプリングキャパシタの容量比を連続的にまたは離散的に可変とするチャージドメインフィルタ回路が提供される。

(もっと読む)

複数のクロックを用いるサンプリングフィルタ

フィルタリングされた入力信号の一連のサンプルを形成する方法及び装置に関する。複数のタップ電流セルは、夫々、入力信号からタップ電流を生成する。複数の分配手段はタップ電流セルを複数の積分手段に結合する。分配手段は、第1のクロック信号によって制御される。複数の積分手段は、それらが受け取るタップ電流を積分して、サンプルを形成する。生成されたタップ電流は、夫々、第1のクロック信号に従って所定のシーケンスで各積分手段へ送られる。積分手段は、夫々、第2のクロック信号によって制御される積分相及びサンプリング相を用いる。積分相の間、積分手段は順にタップ電流を受け取り、一方、休息相の間、タップ電流は受け取られず、回路のコンテンツはサンプリングされ、積分手段はリセットされる。  (もっと読む)

(もっと読む)

信号処理装置、フィルタ装置、信号処理方法、およびフィルタ方法

【課題】信号処理装置、フィルタ装置、信号処理方法、およびフィルタ方法を提供すること。

【解決手段】静電容量が可変である可変キャパシタと、前記入力信号を前記可変キャパシタにサンプリングさせるサンプリングモードと、前記入力信号をサンプリングして得られた電荷を前記可変キャパシタに保持させる保持モードと、前記可変キャパシタに保持されている電荷を出力させる出力モードと、を含む回路モードを切り替えるスイッチング部とを備え、前記可変キャパシタは、前記サンプリングモード時に前記入力信号が入力される入力端子と、前記入力端子との間に絶縁層が設けられており、前記出力モード時に前記可変キャパシタの静電容量を前記サンプリングモード時の静電容量より減少させる第1の制御信号が入力され、前記保持モード時に所定の基準電圧を有する第2の制御信号が入力される制御端子と、を備える信号処理装置。

(もっと読む)

可変フィルタ

【課題】可変フィルタにおいて、入力信号に対するサンプル平均数の増大に応ずるキャパシタ数の増加率を低減すること。

【解決手段】充放電回路部は、縦続接続された複数の充放電部21,22を構成して成る。これらの充放電部のうち、電圧電流変換部202に接続される初段の充放電部21は、並列に接続される複数のキャパシタ203,204を有するキャパシタバンク24および並列に接続される複数のキャパシタ205,206を有するキャパシタバンク25を備えて構成される。キャパシタバンク24,25に蓄積された電荷は所定のタイミングで後段の充放電部22に移送され、充放電部22のキャパシタ218〜220とキャパシタ221との間で共有された電荷が所定のクロック周波数で出力される。

(もっと読む)

受信回路

【課題】 PLL周波数シンセサイザ回路を用いることなく構成して安定した受信動作を行うことができる受信回路を提供する。

【解決手段】 同一の周波数で互いに位相が90度異なる第1及び第2ローカルクロック信号と、スイッチングクロック信号とを生成し、高周波信号と第1及び第2ローカルクロック信号とを各々混合して受信周波数に対応した中間周波数の第1及び第2中間周波信号を生成し、スイッチングクロック信号に同期して動作して第1及び第2中間周波信号の中間周波数の帯域成分をスイッチドキャパシタフィルタによって抽出し、受信周波数は第1及び第2ローカルクロック信号の周波数、スイッチングクロック信号の周波数、並びに第1及び第2ローカルクロック信号の位相関係に応じて設定される。

(もっと読む)

1 - 20 / 34

[ Back to top ]