Fターム[5J039BB04]の内容

パルスの操作 (9,993) | ノイズの除去 (179) | パルス幅の弁別によるもの (107) | 遅延出力との論理操作 (43)

Fターム[5J039BB04]に分類される特許

1 - 20 / 43

パルス幅延長回路および方法

集積回路

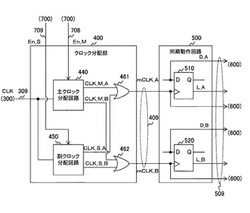

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

信号伝達装置

【課題】ハイブリッド自動車、電気自動車、家電機器、産業機器、及び医療機器の分野では、入出力間を直流的に絶縁した信号伝達装置が用いられているが、並列接続された2つのトランスに入力されるノイズレベルが互いに異なる場合でも、ノイズキャンセルを正常に作動させる。

【解決手段】信号伝達装置100は、1次巻線T11と2次巻線T12とは直流的に分離されており、1次巻線T11と2次巻線T12とは互いに別々の接地電位に接続されるトランスT1と、前記トランスT1の2次巻線T12からの出力が入力される第1コンパレータCM1及び第2コンパレータCM_M1と、前記第1コンパレータCM1の出力が入力される遅延信号生成部141aと、前記第2コンパレータCM_M1の出力が入力されるマスキング信号生成部143aとを有する。

(もっと読む)

半導体回路

【課題】本発明は、ハイレベルの入力信号に混入されたローレベルのノイズ及びローレベルの入力信号に混入されたハイレベルのノイズをより効果よく取り除くことができる半導体回路を提供する。

【解決手段】 入力信号を所定時間遅延して出力する遅延部120、220、320と、該入力信号のレベルによって電圧を充放電させる電圧調整部140、240、340と、該入力信号のレベル及び遅延部120、220、320から出力される信号のレベルを用いて生成された信号によって、電圧調整部140、240、340の充放電動作を制御する組合せ部160、260、360とを含む。

(もっと読む)

グリッジ処理回路

【課題】グリッジのパルス幅を十分に伸張させて後段回路で貫通電流が発生しないようにする。

【解決手段】単相の入力信号から差動信号をノードN1,N2に生成する単相/差動変換回路10と、ノードN1の信号をノードN3の信号でマスキシグしてノードN4に出力し、ノードN2の信号をノードN5の信号でマスキングしてノードN6に出力するマスキング回路30と、ノードN4,N6の信号を入力しノードN7,N8に出力信号を出力するラッチ回路30と、ノードN7の信号を時間T0だけ遅延させてノードN5に出力し、ノードN8の信号を時間T0だけ遅延させてノードN3に出力する遅延回路40とを具備し、ノードN8の信号を出力信号とする。

(もっと読む)

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

遅延回路、及び電子機器

【課題】遅延回路のキャパシタの容量を増大させることなく、外来ノイズの影響による出力電圧の誤動作を防止する。

【解決手段】キャパシタと第1のノードを介して接続され、前記キャパシタを充電または放電する定電流源と、入力電圧が第1のレベルに変化したときに前記キャパシタを放電または充電し、入力電圧が第2のレベルに変化したときに前記キャパシタを充電または放電する充放電回路と、前記キャパシタの充放電の開始から、前記第1のノードの電圧が所定の検知電圧を超えるまでの時間遅延して、出力電圧のレベルを第1のレベルから第2のレベルに変化させる電圧検知回路とを有する遅延回路において、前記入力電圧が第2のレベルであって、かつ前記出力電圧が第2のレベルに変化したときに、前記第1のノードの電圧を前記検知電圧を超えるレベルに保持する電圧保持回路を備えることで出力電圧の誤動作を防止する。

(もっと読む)

半導体装置

【課題】半導体装置の外部に出力される信号にハザードが含まれないようにする。

【解決手段】半導体装置において、IOセル23_1は、タイミング調整回路50および出力バッファ70を含む。出力バッファ70は、タイミング調整回路50によってタイミング調整されたデータ信号DOcおよび出力許可信号OEcを受ける。タイミング調整回路50は、出力バッファ70にデータ信号DOcおよび出力許可信号OEcが入力された時点で、出力すべき論理レベルにデータ信号DOcが変化した後に出力許可信号OEcが非活性状態から活性状態に切替わり、かつ、出力すべき論理レベルをデータ信号DOcが保持している間に出力許可信号OEcが活性状態から非活性状態に切替わるように、IOポート論理回路18から受けたデータ信号DOおよび出力許可信号OEの少なくとも一方のタイミングを調整する。

(もっと読む)

ノイズ除去装置

【課題】使用環境状況の影響を受けずに、ノイズを確実に除去する。

【解決手段】n個のD型フリップフロップを直列に接続し、各D型フリップフロップの出力した信号の論理積を出力とするデジタル・フィルタ20と、m×2個のプリミティブ素子を有するインバータを直列に接続したディレイ・フィルタ30を並列に接続する。入力信号INPUTを両フィルタに入力し、AND回路40が各フィルタの出力する信号DELAYと信号ANDの論理積である信号FILTを出力する。発生期間がクロック信号の周期とDFF回路の段数に対応する期間より短いノイズをデジタル・フィルタ20が除去し、インバータ回路の遅延時間より周期の短いノイズをディレイ・フィルタ30が除去する。

(もっと読む)

スイッチングドライバ回路

【課題】ディスクリート部品を用いることなく、パルス時間が長く、しかも、電圧変動が大きいノイズを確実に除去可能とする。

【解決手段】

入力信号の立ち上がり、立ち下がりを検出し、エッジ検出信号を出力するエッジ検出回路101と、入力信号を所定シフト時間t1シフトして出力するシフトレジスタ回路106と、エッジ検出回路101のエッジ検出信号の入力時点から所定入力時間t2経過後にカウントアップ信号を出力するカウンタ回路102と、シフトレジスタ回路106の出力信号を、カウンタ回路102のカウントアップ信号に同期して出力するDFF回路103と、DFF回路103の出力信号を外部へ出力する出力回路104と、シフトレジスタ回路106とカウンタ回路101のクロック信号を生成、出力する発振回路105とを具備してなり、所定入力時間t2に満たない入力信号が出力されないようになっている。

(もっと読む)

デジタルノイズ保護用回路及び方法

【課題】コンパレータによって生成されたデジタル信号をノイズからの保護方法を提供する。

【解決手段】コンパレータ1によって生成されたデジタル信号(Vcomp)のロジック状態の第1スイッチングにおいて第1ロジック状態から第2ロジック状態へと切り替える出力信号(Vout)の生成ステップと、前記出力信号(Vout)の第1ロジック状態から第2ロジック状態への変更の検出ステップと、第1ロジック状態から第2ロジック状態への変更後の第1時間間隔に対する前記出力信号(Vout)のさらなる切り替えの禁止ステップとにより前記デジタル信号(Vcomp)をノイズから保護する。

(もっと読む)

半導体装置、半導体装置のノイズ除去方法

【課題】より確実にノイズ除去のできるノイズ除去回路を搭載する半導体装置、ノイズ除去方法を提供する。

【解決手段】半導体装置は、ノイズ検知回路(21)と、入力信号遅延回路(22)と、マスク回路(23)とを具備する。ノイズ検知回路(21)は、入力信号(RESETB)に重畳するノイズを検知して、所定時間のマスク信号(NE_FLG)を出力する。入力信号遅延回路(22)は、入力信号(RESETB)を遅延させて遅延信号(RES_DLY)を出力する。マスク回路(23)は、マスク信号(NE_FLG)に基づいて、前記遅延信号(RES_DLY)をマスクした出力信号(RESB)を出力する。

(もっと読む)

電源検出回路

【課題】電源ノイズに起因する誤信号の出力を確実に抑制しつつ回路面積を削減する。

【解決手段】比較回路50は電源出力回路10の出力電圧Aを基準電圧回路20による基準電圧Bと比較し、電源電圧が所定電圧以下の場合は電源未検出信号を出力し、電源電圧が所定電圧よりも高いときは電源検出信号を出力する。基準電圧判別回路60は基準電圧が安定状態にあるか否かを判別し、安定状態にあるときには安定信号を出力し、安定状態にないときには不安定信号を出力する。出力固定回路70は不安定信号を入力したときには比較回路の出力信号を電源未検出時の出力である電源未検出信号に固定化し、安定信号を入力したときには固定化を停止する。ノイズ除去回路80は遅延回路90を内蔵し、その遅延作用により出力固定回路の出力信号に重畳しているノイズを除去する。そして、遅延回路90は、基準電圧回路の内部所定部位の電流値を参照して遅延信号を生成する。

(もっと読む)

半導体スイッチモジュール

【課題】当該半導体スイッチモジュールが適用された機器の誤動作や自己の故障を防止できる半導体スイッチモジュールを提供する。

【解決手段】外部からの駆動信号に含まれる所定幅以下のパルスを除去するフィルタ回路12〜16、と、フィルタ回路で所定幅以下のパルスが除去された駆動信号をゲート信号としてオン/オフする半導体スイッチ19とを備える。

(もっと読む)

半導体集積回路

【課題】複数のノイズパルスが連続して印加される場合においてもノイズを除去する能力を高めたノイズ除去回路を含む半導体集積回路を提供する。

【解決手段】この半導体集積回路は、入力信号を遅延する直列接続された複数の遅延回路と、複数の遅延回路によって互いに時間差が与えられた少なくとも3つの信号の論理積を求めることによってセット信号を生成する第1の論理回路と、複数の遅延回路によって互いに時間差が与えられた少なくとも3つの信号の論理和を求めることによってリセット信号を生成する第2の論理回路と、第1の論理回路によって生成されるセット信号によってセットされ、第2の論理回路によって生成されるリセット信号によってリセットされることにより、正論理の入力信号からパルス状のノイズが除去された出力信号を生成するRSラッチ回路とを具備する。

(もっと読む)

ポートからポートへの遅延を実装することにより雑音を減らす方法

【課題】

ポートからポートへの遅延を実装することにより雑音を減らす。

【解決手段】

雑音を減らす方法は、次を含む:電源供給網をオンにする時に、高速データリンクの最大の雑音の周波数を特定すること;その最大の雑音を最小化する、第1のポートと第2のポートの間の遅延時間を特定すること;及び、第1のポートをオンにした時から、その遅延時間後に、第2のポートをオンにすること。他の実施例も開示し請求する。

(もっと読む)

ノイズリダクション回路、および電子機器

【課題】伝送路に入る信号の両電圧レベルに含まれるノイズを減少させる。

【解決手段】入力信号を遅延させる遅延ユニット14と、入力信号と遅延ユニットの出力信号との論理積を取る論理積ユニット10と、入力信号と遅延ユニットの出力信号との論理和を取る論理和ユニット12と、論理積ユニットから出力される第1の出力信号または論理和ユニットから出力される第2の出力信号の何れか一方を選択して出力する選択ユニットSELと、を含み、選択ユニットは、選択ユニットの出力信号が第1の電圧レベルの場合に第1の出力信号を出力し、選択ユニットの出力信号が第2の電圧レベルの場合に第2の出力信号を出力し、遅延ユニットは、複数の遅延回路DL10_1〜DL10_Nがカスケード接続される構成であり、各遅延回路間のタップTp1〜Tp(N−1)が論理積ユニットおよび論理和ユニットの入力端子にそれぞれ接続される。

(もっと読む)

ノイズフィルタ回路、およびその方法、ならびに、サーマルヘッドドライバ、サーマルヘッド、電子機器、および印刷システム

【課題】 簡易な構造を有するノイズフィルタ回路等を提供する。

【解決手段】 ノイズフィルタ回路(10;60)は、入力信号(IN)を入力するラッチ回路(14;64)を備える。ラッチ回路(14;64)は、第1および第2の論理演算回路(たとえば、NAND回路)を含む。第1および第2のNAND回路のそれぞれにおいて、セット信号(S)またはリセット(R)信号を入力するP型トランジスタ(P1)の能力は、セット信号(S)またはリセット(R)信号を入力するN型トランジスタ(N1)の能力、および、このN型トランジスタ(N1)と直列に接続されるN型トランジスタ(N2)の能力(トータルな能力)より低い。ノイズフィルタ回路(10;60)は、ラッチ回路(14;64)からの出力信号(OUT(XQ;Q))を入力する波形整形回路(16)を、備えてもよい。

(もっと読む)

ノイズリダクション回路、および電子機器

【課題】簡単な回路構成で伝送路に入る信号の両電圧レベルに含まれるノイズを減少させる。

【解決手段】入力信号S10に含まれるノイズを減少させるノイズリダクション回路であって、入力信号を遅延させる遅延ユニットDL10と、入力信号と遅延ユニットの出力信号DLS10との論理積を取る論理積ユニット10と、入力信号と遅延ユニットの出力信号との論理和を取る論理和ユニット12と、論理積ユニットから出力される第1の出力信号ANDS10または論理和ユニットから出力される第2の出力信号ORS10の何れか一方を選択して出力する選択ユニットSELと、を含み、選択ユニットは、選択ユニットの出力信号が第1の電圧レベルの場合に第1の出力信号を出力し、選択ユニットの出力信号が第2の電圧レベルの場合に第2の出力信号を出力する。

(もっと読む)

ノイズリダクション回路、および電子機器

【課題】簡単な回路構成で伝送路に入る信号の両電圧レベルに含まれるノイズの減少をする。

【解決手段】ノイズリダクション回路は、入力信号IS10と、この入力信号を遅延させる遅延ユニットDL10の出力信号DLS10との論理積を取る論理積ユニットまたは論理和を取る論理和ユニットのいずれか一方である少なくとも1つの第1の論理ユニット10と、第1の論理ユニットの後段側に設けられ、論理積ユニットまたは論理和ユニットのいずれかであって上記の一方とは異なる他方である少なくとも2つの第2の論理ユニット12、14と、を含み、少なくとも1つの第1の論理ユニット10および少なくとも2つの第2の論理ユニット12、14がカスケード接続されて構成される。

(もっと読む)

1 - 20 / 43

[ Back to top ]