Fターム[5J039DB13]の内容

パルスの操作 (9,993) | しきい値の特性 (335) | 入力信号レベルに応動するもの (84) | ピーク検波(ホールド)による作成 (18)

Fターム[5J039DB13]の下位に属するFターム

正負ピーク値の中間値をとるもの (5)

Fターム[5J039DB13]に分類される特許

1 - 13 / 13

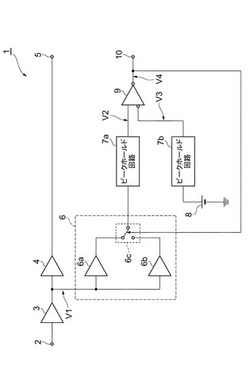

信号レベル検出回路

【課題】増幅回路の動作に必要な電流値を増加させることなく、ヒステリシスを用いて耐ノイズ特性を向上させることができる信号レベル検出回路を提供すること。

【解決手段】増幅回路6aの電圧利得は、増幅回路6bの電圧利得より大きく、切替装置6cは、ピークホールド回路7aに増幅回路6aの出力信号が入力している場合に比較回路9からアラーム信号を受信すると、ピークホールド回路7aに出力する信号を増幅回路6aの出力信号から増幅回路6bの出力信号に切り替え、ピークホールド回路7aに増幅回路6bの出力信号が入力している場合に比較回路9からアラーム信号を受信すると、ピークホールド回路7aに出力する信号を増幅回路6bの出力信号から増幅回路6aの出力信号に切り替える。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22と判定クロック端子23とリセット端子24と温度補償クロック端子25と2値化出力端子26と遅れ出力端子28とピークホールド回路30とボトムホールド回路40と2値化判定回路120と入力信号検出回路130と停止判定回路140を備えている。2値化回路10では、停止判定信号が入力信号の停止期間を検出し、この停止期間にピークホールド回路30とボトムホールド回路40が、各々の記憶値を入力信号に追従して変化させる。これによって、停止期間に、入力信号がピークホールド回路30とボトムホールド回路40の記憶値から算出される閾値を越えて変化することが抑制され、停止期間に2値化出力が反転することが抑制される。

(もっと読む)

2値化回路と位相差判別装置

【課題】 入力電圧を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と第1出力端子26と第2出力端子28とピークホールド回路30とボトムホールド回路40と閾値演算回路50と第1比較回路60と第2比較回路70と第1選択回路80と第2選択回路90と第3選択回路100と第4選択回路110を備えている。第1選択回路80は2値化信号を出力し、第2選択回路90は遅れ2値化信号を出力する。ピークホールド回路30は遅れ2値化信号に基づいてピーク電圧を減少させ、ボトムホールド回路40は遅れ2値化信号に基づいてボトム電圧を増加させる。そのため、遅れ2値化信号を2値化信号に対して確実に遅延させることが可能となる。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】受信した差動信号RX+,RX−の電位振幅が所定値を超えているときその検出信号Vpをパルスとして出力するピーク検出回路11と、ピーク検出回路11から出力する検出信号Vpのパルス幅を差動信号RX+,RX−の少なくとも1周期分延長するパルス幅延長回路12とを備える。ピーク検出回路11は、差動信号RX+,RX−に同一のDCバイアスを与えた後にその差分に対応する電圧信号Vdataを出力する入力差動増幅回路11Aと、入力差動増幅回路11Aのほぼレプリカ回路として構成され、参照電圧Vref’をレベルシフトしたシフト参照電圧Vrefを出力するレプリカ参照電圧生成回路11Bと、電圧信号Vdataとシフト参照電圧Vrefとを比較して検出信号Vpを出力する電圧比較回路11Cと、を備える。

(もっと読む)

ピークホールド回路

【課題】 入力信号が高速な場合など、オペアンプの出力電圧レベルが不足の場合にも、ピーク電圧を出力できるピークホールド回路を得ること。

【解決手段】 入力コンパレータ、ホールドコンデンサ、充電電流制御端子を有し前記ホールドコンデンサに充電電流を供給する充電電流回路、放電回路を備えたピークホールド回路において、前記入力コンパレータを入力信号の電圧と前記ホールドコンデンサの保持電圧を比較するオペアンプで構成し、前記オペアンプの出力端子と前記充電電流回路の充電電流制御端子との間にレベルシフタを備えた。

(もっと読む)

充放電回路および2値化回路

【課題】RSSIを使用したASK信号の復調時においても、2値化の閾値と比較される入力信号の振幅を一定に保つ。

【解決手段】RSSI検波器17にて復調されたASK信号はピークホールド回路23に入力され、ピークホールド回路23は、充放電部24に入力される入力信号のピーク値を検出し、クリップ回路22は、充放電部24に入力される入力信号のピーク値から一定値以下のレベルをクリップし、充放電部24は、クリップ回路22にてクリップされた信号を用いてコンデンサC2を急速充放電することで、コンパレータ27の閾値として用いられる基準電圧Vrefを発生させる。

(もっと読む)

ヒステリシスコンパレータ

【課題】入力信号の振幅が当初の想定よりも小さい場合や入力信号の振幅変動が生じた場合でも、適正な出力信号を得ることができるヒステリシスコンパレータを提供する。

【解決手段】電圧レベルが連続的に変化する入力信号を互いに異なる電圧レベルを有する2つの閾値電圧に基づいて2値化判定し、この判定結果に応じた出力信号を生成するヒステリシスコンパレータであり、入力信号のトップピークを検出し、トップピークに応じたトップピーク検出電圧を生成するトップピーク検出部と、入力信号のボトムピークを検出し、ボトムピークに応じたボトムピーク検出電圧を生成するボトムピーク検出部と、トップピーク検出電圧の電圧レベルとボトムピーク検出電圧の電圧レベルの範囲内で第1および第2の閾値電圧を生成する閾値電圧生成部と、第1および第2の閾値電圧と入力信号の電圧レベルを比較して入力信号を2値化判定し、この判定結果に応じた出力信号を生成する電圧比較部と、を含む。

(もっと読む)

データスライス回路及びデータ復元回路

【課題】復調信号の最初のパルスから確実にデータを復元することが可能なデータスライ

ス回路を提供する。

【解決手段】データスライス回路3は、レベルシフト回路5と基準電圧生成回路6とコン

パレータ7とにより構成されている。レベルシフト回路5は、入力信号SIの電圧レベル

を一定電圧レベルだけシフトしたレベルシフト電圧SLを生成し、基準電圧生成回路6は

、入力信号のピーク電圧及びボトム電圧を分圧した基準電圧SBを生成する。コンパレー

タ7は、レベルシフト電圧SLと基準電圧SBとを比較した結果を出力する。

(もっと読む)

リミッタアンプ回路

【課題】良好な同相雑音耐性が得られ、入力信号に対する高速応答が可能なリミッタアンプ回路を提供する。

【解決手段】リミッタアンプ回路は、正相入力信号VIPと逆相入力信号VINとからなる差動形式の入力信号を増幅する差動増幅器2と、正相入力信号VIPの最大値と逆相入力信号VINの最大値との電圧差に応じた電流を、差動増幅器2の入力段に設けられた差動回路の1対の負荷抵抗24,25から引き抜くオフセット補償回路(AOC回路3)とを有する。

(もっと読む)

二値化回路及び二値化方法

【課題】入力信号を二値化するための二値化回路及び二値化方法に関し、ノイズに対して適切な二値化が行なえる二値化回路及び二値化方法を提供することを目的とする。

【解決手段】本発明は、入力信号を二値化する二値化回路であって、入力信号を微分し、全波整流した波形に整形する波形整形回路(111、112)と、波形整形回路(111、112)で整形された信号の最大値をホールドするホールド回路(113)と、ホールド回路(113)にホールドされた最大値に応じて閾値を生成する閾値生成回路(114)と、波形整形回路(111、112)で整形された信号と閾値生成回路(114)で生成された閾値とを比較する比較回路(115)と、比較回路(115)の比較結果に応じて入力信号を二値化した信号を生成する出力回路(116)とを有することを特徴とする。

(もっと読む)

ディジタル信号受信回路

【課題】 復調信号に直流電位オフセットが生じても、ベースバンド信号を正しく再生できるディジタル信号受信回路を提供する。

【解決手段】 遅延ピーク検出部13によって、ピーク検出部11よりも遅れたタイミングで入力信号INのピークレベルを検出し、遅延ピークレベルDPLとピークレベルPLとのピーク差PLDをピーク差分検出部15で検出する。リセット部17では、ピークレベルPLとボトムレベルBLのレベル差が入力信号INの振幅に対応する所定値を越え、かつピーク差PLDが許容ピーク差PLMを越えたときに、ボトム検出部12に対するリセット信号BRSを出力する。これにより、ボトム検出部12から出力されるボトムレベルBLは、最新の入力信号INに基づいたボトムレベルに置き換えられる。

(もっと読む)

バースト信号受信装置

【課題】 光入力信号の持つ消光比に対する信号再生能力を向上させるバースト信号再生方法を提供する。

【解決手段】 光モジュール10において光電気変換された出力信号をATC−IC20に入力し、インプットバッファ22でレベル調整され、ゲインバッファ(ローゲイン)24で正相に変換された信号を2分岐して、一方はピーク検出回路25に入力してそのピーク値を閾値としてゲインバッファ(ハイゲイン)26に入力し、2分岐したもう一方の信号をゲインバッファ(ハイゲイン)26に入力させて増幅させ、ゲインバッファ(ハイゲイン)26の正相出力と逆相出力をATC回路27にする。

(もっと読む)

スイング低減信号回路のための適応ヒステリシス

差動入力信号を処理するための装置(50)。装置(50)は、差動入力(28)を有する最小ピーク検出器(51)を含む。ピーク検出器(51)は、ピーク検出器の差動入力(28)における平均電圧ピークに比例する第1の電圧を供給する。コンプレッサ(53)が、第2の電圧を供給するために第1の電圧を処理するように設けられている。コンプレッサ(53)の後に、第2の電圧によって調整可能なトリム電流を供給する電圧制御可能な電流源が続いている。トリム電流によってヒステリシス特性が調整可能なヒステリシス具備回路(67.1)は、装置(50)の一部である。  (もっと読む)

(もっと読む)

1 - 13 / 13

[ Back to top ]