Fターム[5J039DB19]の内容

Fターム[5J039DB19]の下位に属するFターム

デジタル演算によるしきい値の作成 (8)

Fターム[5J039DB19]に分類される特許

1 - 20 / 41

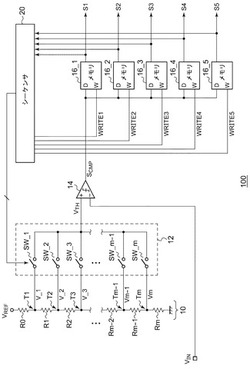

電圧検出回路、それを用いた温度検出回路、電子機器

【課題】回路面積、消費電力を低減するとともに、正しい電圧比較が可能な電圧比較回路を提供する。

【解決手段】抵抗ストリング10は、直列に接続された複数の抵抗の接続点に設けられた各タップに電圧を発生する。セレクタ12は、複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力する。コンパレータ14は、入力電圧VINをセレクタ12の出力電圧と比較する。メモリ16_iは、それぞれがしきい値電圧VTHiごとに設けられ、書き込み信号WRITEiに応答してコンパレータ14の出力SCMPを格納して検出信号Siを生成する。シーケンサ20は、N個のメモリ16_1〜16_Nからの検出信号S1〜SNを受け、セレクタ12の複数のスイッチを制御するとともに、書き込み信号を生成する。

(もっと読む)

二値化回路

【課題】動作速度の低下を抑えつつ、ハイレベル及びローレベルの判定精度を高めることができる二値化回路を提供する。

【解決手段】二値化回路20は、ダイオード31及びコンデンサ32を有するピークホールド回路部30と、ダイオード41及びコンデンサ42を有するボトムホールド回路部40と、コンデンサ32とダイオード31との間のノードN1の電圧、及びコンデンサ42とダイオード41との間のノードN2の電圧の平均電圧VAと入力信号Vinの電圧とを比較して入力信号Vinを二値化する比較回路部70と、上記平均電圧VAに比例する電圧を出力する基準電圧生成回路部60とを備える。ボトムホールド回路部40は、基準電圧生成回路部60から出力された電圧を基準電位VSとして用いる。

(もっと読む)

コンパレータ

【課題】安定したヒステリシス特性を有するコンパレータを提供する。

【解決手段】コンパレータ1は、一対の差動入力トランジスタT1,T2を有する差動回路部10と、差動回路部10にヒステリシスを付加するためのセレクタ回路部20と、レベル変換増幅部30とを備える。セレクタ回路部20は、差動入力トランジスタT1,T2のドレインにそれぞれ接続するトランジスタT3,T4を有し、トランジスタT3,T4の一方がオンするときオンしたトランジスタに接続する側のトランジスタT1,T2から一定のバイアス電流Ibを吸引するように接続される。レベル変換増幅部30の2つの増幅回路31,32は、セレクタ回路部20のトランジスタT3,T4に対して並列に接続されており、差動回路部10の出力に応じてトランジスタT3,T4の一方をオンし同時に他方をオフすることでバイアス電流Ibを切り換える。

(もっと読む)

電圧比較回路

【課題】入力電圧の変化を高精度に検出できる電圧比較回路を実現する。

【解決手段】比較器の出力電圧に応じて所定のヒステリシス電圧幅を持たせて比較器の比較電圧を変化させる電圧比較回路において、一端が比較器の出力端子に接続され、他端に基準電圧に応じた電圧が印加され、比較器の出力電圧に応じてオンまたはオフするダイオードを備え、このダイオードがオフしている時は、基準電圧が比較器の比較電圧となる。

(もっと読む)

比較回路、比較出力方法、A/D変換回路およびA/D変換方法

【課題】比較回路におけるメタステーブル状態による比較結果の判定時間を、劇的に改善することができる比較回路を提供する。

【解決手段】比較回路を、第1段目比較回路部と第2段目比較回路部の2段構成とする。第1段目比較回路部は、第1のクロックタイミングで動作し、入力信号のレベルと基準レベルとの比較判定結果に応じて、ハイレベルまたはローレベルの出力電圧を比較出力として出力すると共に、比較判定ができない間は、ハイレベルとローレベルの出力電圧の中間値の出力電圧を、比較出力として出力する。第2段目比較回路部は、第1のクロックタイミングより遅れた第2のクロックタイミングで動作し、第1段目比較回路部の比較出力を、前記中間値の出力電圧とは異なる値の比較用電圧と比較し、その比較判定結果に応じて比較出力を出力すると共に、その判定結果の比較出力を自己保持するようにする。

(もっと読む)

レベルシフト回路

【課題】レベルシフト回路において、電源電圧が変動した場合のオフセットを抑制する。

【解決手段】レベルシフト回路1は、差動増幅回路10、電流発生回路11、コンデンサ12、保持回路13を備える。差動増幅回路10の非反転入力端子(+)に光ピックアップ2からの入力信号Vinが印加される。先ず、第1のスイッチ14aをオンすることにより、差動増幅回路10、電流発生回路11、コンデンサ12によりフィードバックループを形成してレベルシフトを行い、コンデンサ12に充電された電圧を保持回路13で保持する。その後、第1のスイッチ14aをオフし、第1のスイッチ14bをオンすることにより、保持回路13によって保持された電圧を差動増幅回路10の非反転入力端子(+)に印加してレベルシフトを行う。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22とリセット端子24と第1出力端子26と第2出力端子28と判定クロック端子27とピークホールド回路30とボトムホールド回路40と出力信号生成回路120と補償信号生成回路130を備えている。出力信号生成回路120は、入力端子20に入力される入力信号が短周期で変化する稼動期間に、ピークホールド値減少信号をピークホールド回路30に出力し、ボトムホールド値増加信号をボトムホールド回路40に出力する。補償信号生成回路130は、入力信号が短周期で変化しない停止期間に、補償信号をピークホールド回路30とボトムホールド回路40に出力する。これによって、入力信号の状態に関わらず入力信号を適切に2値化することができる。

(もっと読む)

パルス分離回路

【課題】入力信号からシリアル信号に重畳されたクロックパルスや同期パルスを分離するための閾値電圧を動的に調整することにより、調整の煩雑さを回避することができるパルス分離回路を提供すること。

【解決手段】シリアル信号81にクロックパルス80が重畳された入力信号Sig1と閾値電圧Vthとを比較し、当該比較結果を出力するコンパレータ2と、入力信号Sig1からクロックパルス又は同期パルスを分離可能となる電圧値の電圧を閾値電圧Vthとして出力する閾値電圧調整回路3とを備え、閾値電圧調整回路3は、コンパレータ2の出力に応じて閾値電圧Vthの昇降を行うようにした。

(もっと読む)

電圧比較器

【課題】消費電流を増加することなく高速化することが可能な電圧比較器の提供。

【解決手段】この発明は、差動増幅回路11、微分回路12、および出力増幅回路13を備えている。差動増幅回路11は、差動入力された信号を差動増幅して出力する。微分回路12は、差動増幅回路11の出力を微分し、この微分出力を出力増幅回路13の定電流トランジスタM7のバイアス電圧に加算する。

(もっと読む)

オフセット圧縮回路およびそれを用いたAD変換器

【課題】差動増幅回路のゲインをアンプモードとリセットモードで切換え、リセットモード時の保持電圧を用いてオフセット電圧を圧縮する。

【解決手段】差動増幅回路と、上記差動増幅回路の一方の入力端子に接続された第1のスイッチと、上記差動増幅回路の上記一方の入力端子と他方の入力端子間に接続された第2のスイッチと、ダイオード接続された第1のトランジスタと第2のトランジスタで形成されたカレントミラー回路の該第2のトランジスタに並列に接続された第3のトランジスタと、該第3のトランジスタの入力端子と基準電位に接続された電圧保持手段と、上記第3のトランジスタの入力と上記電圧保持手段の共通接続点と、上記差動増幅回路の出力間に接続された第3のスイッチと、を設けてスイッチを切り換えオフセット電圧を圧縮する。

(もっと読む)

ピークホールド回路

【課題】高速動作に適し、且つピーク検出の精度を向上できるピークホールド回路を提供する。

【解決手段】第1ピークホールド回路20aは、入力信号Vinが供給される入力トランジスタQ1と、入力信号Vinのピーク値をホールドするコンデンサC1と、コンデンサC1の保持電圧が供給されるオペアンプ26と、補正用トランジスタQ2とを備える。また、入力トランジスタQ1に流れる電流を検出する電流検出回路30と、電流検出回路30において検出された電流のピーク値をホールドし、電流Ipとして補正用トランジスタQ2に供給するピーク電流ホールド回路35とを備える。

(もっと読む)

差動電圧比較器及び差動回路

【課題】NBTI劣化又はPBTI劣化による入力トランジスタの閾値のバラツキの増大化を抑制することにより、入力オフセット電圧の増大化を抑制し、例えば、A/D変換器に使用する場合には、INLやDNL等のA/D変換精度の劣化を抑制することができるようにした差動電圧比較器を提供する。

【解決手段】入力制御部28は、判定結果出力期間の間は、入力電圧VIP及び入力電圧VIMの差動回路3の非反転入力端子3A及び反転入力端子3Bへの供給を遮断し、差動回路3の非反転入力端子3A及び反転入力端子3Bに電源電圧VDDを供給し、差動回路3の入力トランジスタをなすPMOSトランジスタのゲート−バルク間電圧を0Vにする。

(もっと読む)

振幅制限増幅回路

【課題】同符号連続耐性と応答時間の短縮と残留オフセット電圧の抑圧とを同時に実現する。

【解決手段】バースト先頭においてはフィードフォワード型オフセット補償回路により瞬時にオフセットを補償し、その後フィードバック型オフセット補償回路によりフィードフォワード型オフセット補償回路で生じる長期的なオフセット変動を補償する。フィードフォワード型オフセット補償回路によるバースト先頭でのオフセット補償時には、フィードバック型オフセット補償回路のアナログスイッチ41をオフ、アナログスイッチ42をオンしておき、時定数の小さいローパスフィルタ22を必要な電圧に急速充電させる。この後オフセット補償回路のキャパシタへの瞬時的な充電が完了するタイミングで、アナログスイッチ41をオンしてローパスフィルタ22の出力電圧を差動増幅器13に入力させるとともに、時定数の大きなローパスフィルタ21を帰還ループに加える。

(もっと読む)

ヒステリシスコンパレータ回路

【課題】回路規模をより縮小することが可能なヒステリシスコンパレータ回路を提供する。

【解決手段】ヒステリシスコンパレータ回路100は、定電流源と、定電流による電圧降下に応じた出力電圧を出力する可変抵抗回路と、入力端子に反転入力端子が接続され、定電流源と可変抵抗回路との間の第1の接点に非反転入力端子が接続され、反転入力端子に入力された入力信号と非反転入力端子に入力された第1の接点の基準電圧とを比較し、この比較結果に応じた電圧を出力するコンパレータと、スイッチ回路と、を備える。スイッチ回路は、コンパレータの非反転出力が“Low”レベルの場合は、可変抵抗回路の抵抗値を第1の抵抗値に切り換え、コンパレータの非反転出力が“High”レベルの場合は、可変抵抗回路の抵抗値を第1の抵抗値よりも小さい第2の抵抗値に切り換える。

(もっと読む)

コンパレータ装置

【課題】より高い精度をもって出力信号を出力することのできるコンパレータ装置を提供する。

【解決手段】更新回路部40は、最初の比較実行期間の終了時まで判定信号Vpの電圧レベルとして基準信号Vrefの電圧レベルを設定する。また、更新回路部40は、出力信号Voutの電圧レベルの立ち上がりの変化時における積分信号Vpの電圧レベルが、基準信号Vrefの電圧レベルを上回る場合、補正済みの判定信号Vrの電圧レベルとして、当該比較実行期間中の判定信号Vrの電圧レベルがその上回った分だけ低く補正された電圧レベルを採用する一方、基準信号Vrefの電圧レベルを下回る場合、補正済みの判定信号Vrの電圧レベルとして、当該比較実行期間中の判定信号Vrの電圧レベルがその下回った分だけ高く補正された電圧レベルを採用する。

(もっと読む)

負荷電流を温度に依存して調節するための回路構成

【課題】負荷電流を温度に依存して調節するための回路構成を提供すること。

【解決手段】差動増幅器は、負荷電流ILを温度の関数として調節するために第1および第2のトランジスタ(Q1、Q2)を有し、回路構成(2)は、2つのトランジスタ(Q1、Q2)が同じコレクタ−エミッタ電圧UCE1、UCE2にて、および1とは異なるコレクタ静止電流IC1、IC2の一定比率にて動作するように設計され、それにより回路構成(2)は、半導体の物理的特性によって決まる温度電圧によって制御され、負荷電流ILを規定された形で温度の関数として調節する。さらに、このような回路構成(2)を備える自動車用ファン、および関連する方法に関する。

(もっと読む)

車両用空調装置

【課題】ユーザの利便性を損なうことのない、ヒステリシスコンパレータ回路を用いた車両用空調装置を提供する。

【解決手段】差動対の一方の電圧入力端子に入力される入力電圧と、差動対の他方の基準電圧入力端子に入力される基準電圧とを比較し、その比較結果を出力端子から二値出力するとともに、入力電圧の変動に対し一定幅の不感帯を有したヒステリシスコンパレータ回路と、ヒステリシスコンパレータ回路の動作状態を検出する動作状態検出手段と、出力端子の出力状態を記憶する出力状態記憶手段と、ヒステリシスコンパレータ回路の駆動電圧が入力状態から遮断状態に遷移したときに、記憶された出力端子の出力状態に基づいて、当該ヒステリシスコンパレータ回路の、駆動電圧遮断時における出力端子の出力反転を阻止するためのダミー電圧を生成し、予め定められた期間、該ダミー電圧を電圧入力端子に重畳入力するダミー電圧生成入力手段と、を備えることを特徴とする車両用空調装置として提供可能である。

(もっと読む)

受信回路および2値信号生成回路

【課題】簡易な回路構成で消費電力の増大を抑制しつつ、受信信号からデジタル信号を再生する際のノイズの発生を抑制できる受信回路を提供する。

【解決手段】ベースバンド信号S1のレベルが参照信号S2のレベルより高くなると、コンパレータ50において出力されるデジタル信号Doutが「0」から「1」へ変化し、ヒステリシスアンプ40のゲインが低下し、コンパレータ50に入力される参照信号S2のレベルが低くなる。また、ベースバンド信号S1のレベルが参照信号S2のレベルより低くなると、デジタル信号Doutが「0」へ変化し、ヒステリシスアンプ40のゲインが上昇し、コンパレータ50に入力される参照信号S2のレベルが高くなる。何れの場合も、デジタル信号Doutの値を維持した状態でベースバンド信号S1と参照信号S2との電圧差が広がるため、コンパレータ50の誤動作が起こりにくくなる。

(もっと読む)

ドライバ設計方法

【課題】ドライバ設計方法が開示される。

【解決手段】ドライバの設計方法は、マッチングステージでの電流変化を利用して複数のトランジスタのミスマッチした特性差によって生じるオフセットを導出するステップと、特性差を減らすように、オフセットの導出結果を利用してトランジスタの大きさを決定し、測定されたマッチング情報及び決定されたトランジスタの大きさを利用してシミュレーションによって求めたドライバのシミュレーション収率が目標収率に近似するまで大きさを再決定するステップと、最終的に決定された大きさを反映してドライバを製作し、製作されたドライバのテスト収率を求めるステップ及びテスト収率が目標収率にならない場合、測定されたマッチング情報を調整してシミュレーションによって求めたドライバの調整収率がテスト収率に近似するまでマッチング情報を調整するステップと、を備える。

(もっと読む)

半導体回路

【課題】CMOS回路と差動回路の両方の利点を生かした回路方式として擬似差動回路があるが、プロセスばらつき等を考慮すると、正・負出力のクロスポイントが一定ではなく、出力波形のデューティのばらつきも大きくなるという欠点がある。

【解決手段】本発明にかかる半導体回路は、第1の電源と出力端子との間に接続され入力信号が印加される第1導電型の第1トランジスタと、第2の電源と前記出力端子との間に接続される第2導電型の第2トランジスタと、前記第1の電源と前記出力端子との間に接続される第2導電型の第3トランジスタと、前記第2の電源と前記出力端子との間に接続される第1導電型の第4トランジスタとを有する。

(もっと読む)

1 - 20 / 41

[ Back to top ]