Fターム[5J039EE21]の内容

Fターム[5J039EE21]の下位に属するFターム

間欠形のもの (20)

Fターム[5J039EE21]に分類される特許

1 - 20 / 46

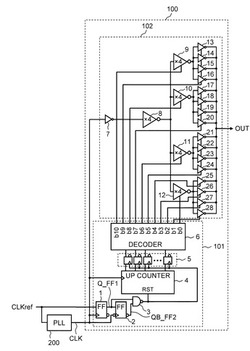

クロックバッファ回路及びクロック分配回路

【課題】クロック源の消費電力を増大させることなく、動作クロック周波数に応じて駆動能力を変化させることにより消費電力低減可能なクロックバッファ回路を提供すること。

【解決手段】クロック信号を伝達するバッファ部102と、クロック信号の参照クロック信号に対する逓倍数をカウントし、バッファ部102に対して逓倍数に基づいたイネーブル信号を出力する駆動能力切替部101と、を備え、バッファ部102は、当該バッファ部102の入力に接続された入力インバータ7と、イネーブル信号によりオンオフが可能であって、それぞれの出力が当該バッファ部の出力に共通に接続された複数の出力インバータ13〜28と、を備え、入力インバータ7が1個のCMOSインバータからなるクロックバッファ回路。

(もっと読む)

多相クロック生成回路

【課題】

位相ノイズが少ない多相クロック生成回路を提供する。

【解決手段】

多相クロック生成回路は,基準クロックを生成する基準クロック生成器と,リング状に接続された複数の遅延回路を有し,前記複数の遅延回路がそれぞれ位相がずれた出力クロックを出力する多相クロック発振器と,前記複数の遅延回路のいずれかの出力端子に前記基準クロックを供給する基準クロック注入回路とを有する。多相クロック発振器のクロックの位相ノイズを低減し周波数変動が抑制できる。

(もっと読む)

パルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置

【課題】 駆動中の論理ゲートを減らして消費電力を少なくし、クロックが通る論理ゲート数を減らしてクロック遅延を短くしたパルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置を提供する。

【解決手段】 パルスエッジ選択回路が、複数のクロックから1つのクロックを選択して通過させる入力段と、前記1つのクロックをエッジ検出回路に出力する出力段とを有し、クロックの立ち下がりエッジを検出して、第1のクロックの立ち下がりエッジで立ち上がり、第2のクロックの立ち下がりエッジで立ち下がるパルスを生成するエッジ検出回路の場合に、前記出力段は、複数の入力端を有する複数のNORゲート及び複数の入力端を有する複数のNANDゲートを交互に組み合わせて接続されており、前記第1及び第2のクロックを出力する出力ゲートにはNORゲートが使用される。立ち上がりエッジでパルスを生成する場合、出力ゲートにはNANDゲートが使用される。

(もっと読む)

半導体集積回路の設計方法及びプログラム

【課題】タイミング制約を満たすためにセルの物理的な位置やRTL(Register Transfer Level)を変更する必要がなく、回路の最適化を短時間に行うことができ、半導体集積回路の設計期間を短縮することができる半導体集積回路の設計方法、設計プログラムを提供する。

【解決手段】半導体集積回路のネットリストに対して静的タイミング解析を行うことにより、所定のタイミング制約を満たさないタイミングエラーパスを検出し、前記タイミングエラーパスを含む第1の論理ブロックと、フリップフロップを介して前記第1の論理ブロックに接続され、所定のタイミング制約を満たす第2の論理ブロックとを抽出し、前記第1の論理ブロックと前記第2の論理ブロックとの間のフリップフロップが正相/逆相フリップフロップである場合は、当該正相/逆相フリップフロップを逆相/正相フリップフロップに変更する。

(もっと読む)

同期化結晶発振器ベースのクロックを採用するシステム

【課題】改良された同期クロックシステムを提供する。

【解決手段】同期クロック信号を必要とする複数のシステムノードを有する電子システム用の同期クロックシステム。クロックシステムは、第1の同期バスと第1の同期バスから絶縁された第2の同期バスと、交互にバスに接続された少なくとも1対、そして好ましくは複数対のSXOモジュールを含む。システムノードの各々は、第1のバスに沿った任意の場所において適宜選択されたあらゆる接続点のうちの異なる1つで接続される。SXOモジュールが接続されるバスに沿った点は、およそ等間隔で隔てられる。システムノードは信号調整回路を用いてバスに接続され、信号調整回路は、補正回路、増幅器、周波数逓倍器、論理変換器、およびファンバッファを含んでいてもよい。

(もっと読む)

デシリアライザ

【課題】PLL回路を用いずにクロックを同期させることを課題とする。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

(もっと読む)

非重複クロック生成のための技術

【解決手段】望ましい周波数範囲にわたって、正確な非重複時間及びクロックフェーズ遅延時間を生成する技術が提供される。一構成において、装置はそれに結合されるクロック生成回路への制御電圧を順に生成する遅延ロックループ(DLL)回路を含む非重複クロック生成回路を備えている。制御電圧はクロック生成回路によって生成される非重複遅延クロック信号の正確なタイミング関係を維持するように動作する。一態様において、DLL回路は知られたデューティサイクルによる入力クロックを受信し、入力クロックサイクルの特定の部分へのユニット遅延をフィックスする出力制御電圧を得る。更なる態様において、クロック生成回路は製造プロセス変化とは関係ない非重複時間(tnlp)でクロック信号の第1のセットから遅延されたクロック信号の第2のセット及びクロック信号の第1のセットを生成するDLL回路に結合される複数の電圧制御遅延セルを備えている。 (もっと読む)

信号生成回路及びその信号生成方法

【課題】信号生成回路において、容易に、十分な出力信号レベルを確保したまま、スプリアスとなる高調波を除去し、正弦波を生成することである。

【解決手段】本発明の信号生成回路の一態様は、第1の入力信号に基づき第1の信号を出力する第1の分周器1bと、第2の入力信号に基づき第2の信号を出力する第2の分周器1bと、第1の入力信号と第2の入力信号との間に第1の位相差φを与える第1の移相器2a、2bと、第1の信号と第2の信号とを合成し、出力信号を生成する合成回路3a〜3dと、を有し、第1の移相器2a、2bは、第1の信号において除去対象となる第1の高調波成分が、第1の信号と第2の信号との間で逆位相となる第1の位相差φを第1の入力信号に付加して第2の入力信号を生成する。

(もっと読む)

同期周波数合成器

【課題】同期周波数合成器によるクロック生成装置を提供する。

【解決手段】クロック生成装置において、2つの入力クロックに関連付けられた基準位相の範囲内の位相値を有する出力を生成する位相補間器121を有する。ロジック・ユニット130は、位相補間器121の複数の位相設定を決定するために結合され、分周器122は位相補間器121に結合され、変更可能な分周設定に基づき出力クロックを生成する。

(もっと読む)

半導体集積回路

【課題】クロック信号の位相、デューティー比等の変動に対し耐性の強い、小型の半導体集積回路を提供する。

【解決手段】複数配設される回路部と、クロック信号の立ち上がりエッジから前記クロック信号を逓倍した周期の第1信号を生成する第1カウンタと、前記クロック信号の立ち下がりエッジから前記クロック信号を逓倍した周期の第2信号を生成する第2カウンタと、前記第1信号が転送される第1ラインと、前記第2信号が転送される第2ラインと、前記第1ライン及び前記第2ラインと接続され前記第1信号と前記第2信号との位相差から第3信号を生成し前記回路部に前記第3信号を出力する位相比較器と、を備え、前記位相比較器は、前記第1ライン及び前記第2ライン上に配設され且つ前記第1ライン及び前記第2ラインの末端と前記回路部との間に複数配設される。

(もっと読む)

データ受信装置

【課題】シリアルデータの各データにデータ幅の不均等や位相差があっても、サンプリングミスを防止することのできるデータ受信装置を提供する。

【解決手段】データ受信装置1は、多相クロック生成部11が、入力されたクロック信号CKから相互の位相差がT/7である7個のクロックC1〜C7を生成し、位相調整部21、22、23が、位相制御信号A、B、Cによる設定に応じてクロックC1〜C7の個々のクロックの位相を調整して、サンプリングクロックCA1〜CA7、CB1〜CB7、CC1〜CC7として出力し、シリアルパラレル変換部31、32、33が、サンプリングクロックCA1〜CA7、CB1〜CB7、CC1〜CC7により、入力されたシリアルデータA、B、Cをそれぞれサンプリングし、7ビットのパラレルデータA、B、Cに変換する。

(もっと読む)

クロック生成回路、システムLSI

【課題】システムLSIに好適なクロックを生成するクロック生成回路を提供する。

【解決手段】複数の機能モジュールを有するシステムLSIの各機能モジュールに供給するクロックを生成するクロック生成回路200である。クロック生成回路200は、周期的に読み出されることにより複数の異なるクロック信号を与えるクロックパターンを記録したクロックパターンメモリ210と、クロックパターンメモリ210のアドレスを順に指定して周期的なクロックパターンの読み出しを制御するポインタ制御部220と、を備える。

(もっと読む)

データ出力回路

【課題】データ出力回路を提供する。

【解決手段】クロック信号を受信して所定のパルス幅を持つクロックパルスを生成するデータ出力制御部と、前記クロックパルスに同期して第1データを出力する第1データ出力部と、前記クロックパルスに同期して第2データを出力する第2データ出力部と、を含むデータ出力回路を提供する。

(もっと読む)

ミキサ

【課題】ダイレクトコンバージョン方式や低IF方式では局部発振器信号の高調波成分によるノイズを低減させる。

【解決手段】位相差がそれぞれ120°異なる3相信号を局部発振信号として受信信号と乗算し、それぞれの復調波の同相信号をキャンセルすることで、局部発振信号の高調波成分のうち、第3高調波によるノイズ成分をキャンセルすることができるミキサを提供する。

(もっと読む)

クロック信号生成装置及び方法

【課題】比較的小さな回路規模で、入力された多相クロック信号から所望の位相のクロック信号を生成する。

【解決手段】入力された多相クロック信号から所望の位相のクロック信号を生成する装置において、中間クロック生成器(11)は、多相クロック信号のいずれか一つを基準クロック信号として、基準クロック信号の複数周期を1周期とする多相中間クロック信号を生成する。第1の位相セレクタ(12)は、多相中間クロック信号のいずれか一つを選択する。第2の位相セレクタ(13)は、多相クロック信号のいずれか一つを選択する。ラッチ回路(14)は、第1の位相セレクタ(12)によって選択された中間クロック信号を、第2の位相セレクタ(13)によって選択されたクロック信号でラッチする。

(もっと読む)

位相差平滑化装置

【課題】多相クロック生成及び伝送の過程において発生した多相クロックの位相誤差を低減する。

【解決手段】入力多相クロックのうち所望の位相関係にある複数のクロックを入力して各クロックの位相に所望の重み付けをする重み付け手段と、重み付けされたクロックを加算する加算手段と、を有する位相フィルタ回路を前記多相クロックの位相数と同数備え、位相フィルタ回路から出力されたクロックを出力多相クロックとして出力する。

(もっと読む)

データセンタートラッキング回路及びこれを含む半導体集積回路

【課題】本発明は、外部環境の影響にも安定的に動作し、より向上した電力及び面積効率を具現するデータセンタートラッキング回路及びこれを含む半導体集積回路を提供する。

【解決手段】本発明は、直列連結した複数のクロックバッファーからなり、クロックをバッファーリングして出力信号を出力するクロックツリー;クロックに基づき、出力信号の位相の変化を感知して感知信号を出力する感知部;及び、感知信号に応じて、クロックツリーに供給される電流を調節し、出力信号の位相を調節するディレイ補償部を含む。

(もっと読む)

電子回路およびその構成方法

【課題】消費電力の少ない電子回路およびその構成方法を提供する。

【解決手段】クロック信号CLKにより入力状態F〜Iを記憶し、記憶結果J〜Mを外部に出力する記憶回路11〜14を有する記憶回路群15と、記憶回路11〜14の入力端Dと出力端Qに接続され、入力状態F〜Iが記憶結果J〜Mと異なったときに、記憶回路11〜14にクロック信号CLKの供給を許可するイネーブル信号EN1〜EN4を出力する比較手段16〜18と、比較手段16〜18の少なくとも1つがイネーブル信号EN1〜EN4を出力しているときは、クロック信号CLKを記憶回路群15に供給し、比較手段16〜18がイネーブル信号EN1〜EN4を出力していないときは、クロック信号CLKの供給を停止するクロックゲート回路20と、を具備する。

(もっと読む)

プログラム可能な遅延を有するシーケンスが独立のオーバーラップしないディジタル信号発生器

【課題】オーバーラップしないクロック発生回路を提供する。

【解決手段】複数の遅延された基準クロック信号を生成するプログラム可能な遅延基準クロック信号回路と、プログラム可能な遅延基準クロック信号回路と動作可能に接続され、オーバーラップしないクロック信号を発生する複数の遅延クロック信号発生器とを含む。各遅延クロック信号発生器は、クロック信号の立ち上がりの遅延を制御し第1の信号を出力するラッチまたはフリップフロップと、遅延されたクロック信号の立ち下がりエッジの遅延を制御し第2の信号を出力するもう一つのラッチまたはフリップフロップと、第1および第2の信号からクロック信号を発生する論理回路とを含む。ラッチまたはフリップフロップは、複数の遅延された基準クロック信号の1つに応答してクロック信号の立ち上がりエッジの遅延を独立して制御する。

(もっと読む)

クロック生成回路及び電子機器

【課題】入力クロックから出力クロックまでの遅延時間のロックと出力クロックの精度の良い位相調整とを両立できるクロック生成回路、電子機器の提供。

【解決手段】クロック生成回路は、クロックCK1を受け、クロックCK2を出力するスキュー調整回路10と、クロックCK2を受け、クロック遅延時間がロックされた多相クロックRCK1〜RCKMを生成して出力するDLL回路40と、多相クロックのいずれかに対応するクロックを、出力クロックCKQとして出力するクロック出力回路70を含む。スキュー調整回路10は、クロックCK1を遅延させたクロックをクロックCK2として出力する遅延回路30と、多相クロックのいずれかに対応するクロックCK3を受け、クロックCK1とCK3の位相が一致するように、クロックCK1に対するクロックCK2の遅延時間を調整する遅延調整回路20を含む。

(もっと読む)

1 - 20 / 46

[ Back to top ]