Fターム[5J039JJ10]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 主たる比較部 (286)

Fターム[5J039JJ10]の下位に属するFターム

二安定素子によるもの (109)

論理ゲートによるもの (77)

カウンタによるもの (68)

一方の入力を電圧−時間軸に直すもの (23)

Fターム[5J039JJ10]に分類される特許

1 - 9 / 9

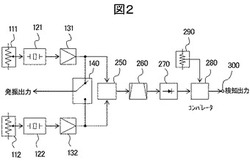

中波放送機の発振部

【課題】2台の水晶発振器を備え、一方の水晶発振器が出力する周波数信号を利用して発振する中波放送機の発振部において、2台の水晶発振器各々の発振器の出力周波数のズレを監視し、ズレが発見された場合に、アラーム信号を発生し、迅速な対応を即すことで、中波放送機の信頼性をより高める。

【解決手段】現用と予備の2台の水晶発振器の出力周波数を、常に比較若しくは監視し、周波数ズレが発生した場合に対応できるように発振制御を行う中波放送機の発振部とした。

(もっと読む)

デューティ比補正回路及びデューティ比補正方法

【課題】非同期信号のデューティ比を補正可能なデューティ比補正回路を提供すること。

【解決手段】本発明に係るデューティ比補正回路は、第1クロック信号が入力されるクロック用入力バッファと、補正信号に基づいて、前記クロック用入力バッファから出力される第2クロック信号のデューティ比を調整して第3クロック信号を生成するクロック用デューティ調整回路と、第1データ信号が入力されるデータ用入力バッファと、前記補正信号に基づいて、前記データ用入力バッファから出力される第2データ信号のデューティ比を調整して第3データ信号を生成するデータ用デューティ調整回路と、前記第3クロック信号に基づいて、前記補正信号を生成するデューティ比較回路と、を備えるものである。

(もっと読む)

リング発振器及びこれを用いるマルチ位相クロック補正回路

【課題】クロスカップル構造を有する複数のバッファを備えて発振し、CMLレベルのクロック信号を生成することのできるリング発振器を提供し、また、基準位相クロック信号を補正して希望の周波数、及び互いに予め定められた位相差を有するマルチ位相クロック信号を生成することのできるマルチ位相クロック補正回路を提供する。

【解決手段】 本発明のリング発振器は、各々クロスカップル構造を有し、予め定められた電圧レベルのバイアス電圧が印加されて複数のクロック信号を生成するための複数のバッファ手段を備え、前記複数のクロック信号が、前記バイアス電圧に対応するスイング幅を有する。

(もっと読む)

位相調整回路および試験装置

【課題】被測定信号の位相を、基準信号の位相に精度よく合わせることができる位相調整回路を提供する。

【解決手段】被測定信号の位相を調整する位相調整回路であって、トリガ信号を生成するトリガ発生部と、基準信号を受け取り、共通の前記トリガ信号のタイミングで、被測定信号および基準信号を測定し、被測定信号および基準信号のそれぞれの信号レベルの差分に応じた測定結果を出力するレベル比較部と、レベル比較部が出力する信号レベルの差分が略零となるように、被測定信号の位相を調整する信号位相調整部とを備える位相調整回路を提供する。

(もっと読む)

半導体集積回路装置および出力バッファ遅延変動検出方法

【課題】I/Oバッファの実際の配置場所及び実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出し、オーバーマージンな設計を回避できるようにした半導体集積回路装置を提供する。

【解決手段】差動アンプ152で、VSS変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP1として求める。差動アンプ153で、VDE変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP2として求める。差動アンプ154で、VDE・VSS変動の影響を受けていない状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP3として求める。

(もっと読む)

周波数比較器、周波数合成器及び関連方法

【課題】電圧に基づいて内部周波数を設定し、これを外部周波数と比較するアナログ周波数比較器と、アナログ周波数比較器の同じ原理でクロック信号を合成するアナログ周波数合成器、及び関連の方法を提供する。

【解決手段】周波数比較器は、第一信号と入力電圧に基づいて基準信号を生成する周波数検出回路と、該入力電圧に基づいて第二信号を生成する周波数発生器と、周波数検出回路と周波数発生器に結合され、基準信号と第二信号の一方に基づいて充電電流をイネーブルして電圧レベルを上げ、更に基準信号と第二信号のもう一方に基づいて放電電流をイネーブルして電圧レベルを下げる電荷ポンプ回路と、電荷ポンプ回路に結合され、該電圧レベルに基づいて第一信号と第二信号間の周波数関係を示す決定論理とを含む。

(もっと読む)

位相比較器

【課題】フルレートとハーフレートの両方に対応した位相比較器を得る。

【解決手段】データ信号の立ち下がりタイミングでクロック信号の振幅値を検出する第一の検出手段1と、データ信号の立ち上がりタイミングでクロック信号の振幅値を検出する第二の検出手段2と、第一の検出手段1がクロック信号の立ち上がり状態又は立ち下がり状態の振幅値を検出しているのかを識別して第一の識別結果を出力し、第二の検出手段2がクロック信号の立ち上がり状態又は立ち下がり状態の振幅値を検出しているのかを識別して第二の識別結果を出力するエッジ比較手段3と、第一の識別結果に応じて第一の検出手段1の出力の極性を反転する第一の極性反転手段4と、第二の識別結果に応じて第二の検出手段2の出力の極性を反転する第二の極性反転手段5と、データ信号の極性に応じて第一又は第二の極性反転手段4、5の出力値を選択して出力する信号選択手段6とを設けた。

(もっと読む)

ディジタル位相同期装置

【課題】入力された正弦波と周波数が等しく、かつ位相が同期した正弦波を、簡易で正確に、出力する装置を提供する。

【解決手段】位相差検出回路1は、外部から入力された第一の正弦波と正弦波生成回路5より出力する第二の正弦波との位相差を、ディジタル信号処理により算出する。その算出値に基づいて第二の正弦波の位相と周波数を調整するので、正弦波生成回路5は入力された第一の正弦波に周波数が等しく、かつ位相が同期した第二の正弦波を簡易に正確に出力することができる。

(もっと読む)

位相比較回路及びクロックリカバリ回路

データ信号とクロック信号の位相差を示す位相差信号を出力する位相比較回路であり、異なる複数の識別レベルを用いてデータ信号の位相を検出し、位相を示す複数の信号を出力する検出部と、検出部から出力される複数の識別レベルに対応する複数の出力信号の各々とクロック信号との位相差を示す複数の位相差信号を出力する位相比較部と、位相比較部から出力される複数の位相差信号の全部又は一部を用いて、複数の位相差信号のうちの1つの信号を出力するか又は出力しないかを制御する制御部とを有するように構成する。  (もっと読む)

(もっと読む)

1 - 9 / 9

[ Back to top ]