Fターム[5J039JJ15]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 主たる比較部 (286) | カウンタによるもの (68)

Fターム[5J039JJ15]に分類される特許

1 - 20 / 68

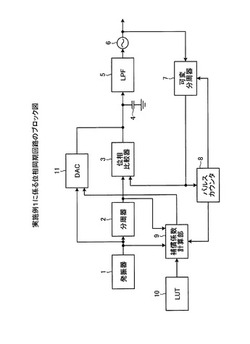

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

遅延ロックドループを内蔵する半導体集積回路およびその動作方法

【課題】擬似ロックを防止するための論理回路の回路規模を低減する。

【解決手段】遅延ロックドループ(DLL)は、複数の可変遅延回路DL0〜8の電圧制御遅延回路1と位相周波数比較器2とチャージポンプ3を具備する。初段の出力PH[0]と最終段の出力PH[8]は、比較器2に供給される。比較器2のアップ信号とダウン信号は、チャージポンプ3に供給される。擬似ロック防止回路4は、第M段の出力PH[1]と第M+1段の出力PH[2]に応答して、可変遅延リセット信号RST_VDL_T、Bを生成する。初段の回路DL0から第M+1段の回路DL2に、クロック入力信号CLKとクロック反転入力信号がリセット信号RST_B、Tとして供給される。第M+2段の回路DL3から最終段の回路DL8に、可変遅延リセット信号RST_VDL_T、Bがリセット信号RST_B、Tとして供給される。

(もっと読む)

同期信号処理装置

【課題】回路の小面積化、低消費電力化を図ることが可能であり、しかも温度依存性の影響を受けない安定した位相比較が可能な同期信号処理装置を提供する。

【解決手段】水平同期信号を同期クロックで同期させ、当該同期クロックのタイミングでデジタルデータとして出力する時間デジタル変換器(TDC)と、同期クロックをカウントして参照クロックを生成する参照クロック生成部と、TDCによるデジタルデータと参照クロックの位相比較を行うことにより位相差情報を得るデジタル位相比較器と、デジタル位相比較器の位相差情報に応じて上記参照クロックとTDCによる水平同期信号のデジタルデータの位相が一致するように周波数が制御される同期クロックを生成する同期クロック生成装置と、を有する。

(もっと読む)

位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

(もっと読む)

パルス信号補正装置およびそれを用いた充填装置

【課題】流量計と充填を制御する制御装置の間でノイズなどによって流量を表すパルスが増加あるいは消失すると、制御装置が正確な流量を把握できないので、正確に充填することができない。本発明はこのような課題を解決することを目的にする。

【解決手段】パルス信号補正装置を経由して流量計の出力を制御装置に入力する。パルス信号補正装置は流量計の出力と制御装置が受信したパルス数の差分を計算し、この差分に基づいて、次の出力周期で出力パルス数を補正するようにする。制御装置が正確な流量を得ることができるので、正確に充填できる。

(もっと読む)

デジタルPLL回路及びクロック生成方法

【課題】位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供する。

【解決手段】デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器10と、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を範囲に限定されない位相値に補正する補正部11と、補正部の出力する位相値に応じてスレーブクロックを生成するスレーブクロック生成部15とを含む。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

時間デジタル変換装置

【課題】時間デジタル変換装置のダイナミックレンジを広くする。

【解決手段】第1の信号に応答して、所定の周期で繰返される第1のパルスの生成を開始する第1のパルス列生成部と、前記第1の信号に応答して、前記第1のパルスのカウントを開始するカウンタ回路と、入力端子が互いに接続され更にクロック端子が互いに接続される複数の遅延フリップフロップを有するストキャスティック型時間デジタル変換装置とを含み、第2の信号が入力する時の前記カウンタ回路のカウント数に基づく第1の時間を、前記第1の信号と前記第2の信号の時間差として検出する。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

クロック周波数制御回路及びクロック周波数制御方法

【課題】 信号の分周比を比較的少なくし、また位相雑音の増加も抑圧した上で微少な周波数変化した信号を生成するPLL回路を実現する。

【解決手段】 本発明は、所定の電圧を加減することにより出力周波数を制御する相関回路入力される電圧に応じて出力周波数が変化する電圧制御発振器と、電圧制御発振器の出力を分周する第1の分周回路と、外部から入力される基準周波数を分周する第2の分周回路と、第1の分周回路と前記第2の分周回路との出力の位相に応じたパルスを出力する位相比較器と、位相比較器の出力から低周波成分を抽出し、電圧制御発生器に入力するローパスフィルタとを有する。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

位相同期回路及び無線機

【課題】位相同期回路のセトリング時間を短縮する。

【解決手段】位相同期回路は、制御信号に応じた発振周波数を含む発振信号を生成する電圧制御発振器と、前記発振信号を分周して分周信号を生成する分周器と、前記分周信号と基準信号との位相を比較し、比較信号を生成する位相比較器と、前記比較信号に応じた電流を出力するチャージポンプと、前記電流をフィルタリングし、前記制御信号を生成するフィルタと、前記分周信号の周波数の定数倍の値と前記基準信号の周波数の定数倍の値との差分が極小となった場合に検出信号を生成する周波数差検出回路と、前記検出信号が生成されると、前記分周信号と前記基準信号との位相を同期させる位相調整回路とを備える。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

デジタル位相同期ループ回路

【課題】TDC(Time−to−DigitalConverter)の回路規模を拡張することなく、デスキュー用途に用いることが可能であるADPLLの構成の提供。

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

(もっと読む)

位相同期ループ回路

【課題】必要な特性を満たしつつ、回路構成を簡素化し、省面積化を可能とするデジタルPLLの提供。

【解決手段】リファレンスクロック信号FRと分周クロック信号FDの位相差を検出するTDC101、FDとFRの進み遅れを出力するFF103、位相誤差演算器102、位相誤差(PERR)を平滑化するデジタルフィルタ104、出力クロック信号FOを出力するDCO105、FOを分周したFDを出力するN分周器106、N分周器106内のカウンタ値をFRに応答してサンプルするレジスタ107を備え、TDC101は、位相差検出測定範囲がFOの1周期以内とされ、FRとFDの位相差をFOの1周期に換算した小数で出力し、位相誤差演算器102は、FDとFRの位相差が、FOの周期の整数倍以上のときは、レジスタ107出力と符号情報signから、FOの1周期内のときは、TDCの出力と符号情報signからPERRを演算出力する。

(もっと読む)

PLL回路、PLL回路の動作方法およびシステム

【課題】 回路規模を増加することなく、PLL回路の精度を向上する。

【解決手段】 時間計測回路は、基準クロックの遷移エッジが現れてから、出力クロックの遷移エッジが2回現れるまでの時間間隔をカウント値として計測する。位相差正規化回路は、計測された時間間隔を出力クロックのクロック数で表される微少位相差に正規化する。また、位相差正規化回路は、PLL回路のロック後に、”1”または”2”を示す微少位相差が連続して現れるときに、”1”と”2”がランダムに現れるまで正規化係数を徐々にずらす。演算回路は、出力クロックの積算値から微少位相差の値を引いた値を、周波数制御語の積算値から差し引いて、基準クロックと出力クロックの位相差を示す位相差信号を生成する。発振回路は、基準クロックと出力クロックの位相を合わせるために、位相差信号に基づいて出力クロック信号の周波数を変更する。

(もっと読む)

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

クロック異常検出回路

【課題】クロック異常を検出する精度を向上させる技術を提供する。

【解決手段】被検査クロックを遅延させる第1の遅延回路の出力と第2の遅延回路の出力よりLow期間を決める。定められたLow期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。第1の遅延回路の出力と第2の遅延回路の出力よりHigh期間を決める。定められたHigh期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。Low期間の異常とHigh期間の異常を統合する。

(もっと読む)

1 - 20 / 68

[ Back to top ]