Fターム[5J039JJ16]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 主たる比較部 (286) | 一方の入力を電圧−時間軸に直すもの (23)

Fターム[5J039JJ16]に分類される特許

1 - 20 / 23

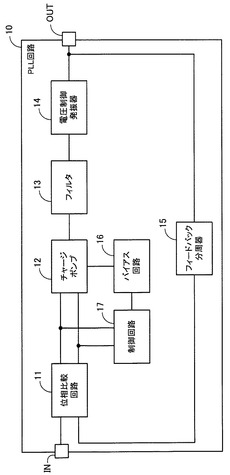

PLL回路

【課題】低消費電力のPLL回路を提供する。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

パルス出力型フィールド機器およびそのチェック方法

【課題】パルス信号を出力するフィールド機器のパルス信号が正確に出力されているかをチェックするためには、内部積算値とパルス信号が入力されるカウンタを同期して動作させなければならないので、操作が複雑であり、かつリアルタイムでチェックできなかった。本発明はこのような課題を解決することを目的とする。

【解決手段】物理量に対応する値を基準時間における値に変換し、パルス信号をこの基準時間の間カウントする操作を繰り返して、このカウント値と前記基準時間における値を比較するようにする。簡単な操作でリアルタイムにパルス信号をチェックできる。

(もっと読む)

PLL回路

【課題】 電源起動からロックまでの時間を短くすると共に、電源断時に電荷を速く放電できるPLL回路を提供する。

【解決手段】 位相の進み/遅れを検出器11で検出し、位相の進み/遅れに相当する信号を積分器12で積分し、起動パルス生成部13が、電源起動を検出し、ロックまでの時間に基づいたパルス幅のパルスをLPF5と積分器12に出力し、LPF5と積分器12が、起動パルス生成部13からのパルスによって内部のコンデンサを充電すると共に電源断で内部のコンデンサに蓄積された電荷を放電するPLL回路である。

(もっと読む)

PLL回路

【課題】平均値計算器に演算能力が比較的低い計算器を用いることが可能な技術を提供することを目的とする。

【解決手段】PLL回路は、基準クロック信号frと比較クロック信号fpとの位相比較を基準クロック信号frの周期毎に実行し、高電圧レベルの第1パルス及び低電圧レベルの第2パルスを含む信号を、前記第1及び第2パルスの当該周期単位でのパルス幅の差が当該位相比較での位相差に対応するように生成する位相比較器2と、位相比較器2が生成した信号の電圧を基準クロック信号frの周期毎に平均化する平均値計算器3とを備える。そして、平均値計算器3からの出力を基準クロック信号frの1周期分よりも長く遅延させるm周期遅延器5を備える。

(もっと読む)

位相比較器及びその位相比較器を用いたクロック・リカバリ回路

【課題】

クロックによりサンプリングされた受信データ間のゼロクロス点の位相を高精度で検出することが可能な位相検出器を提供することである。

【解決手段】

第1受信データの第1データ値及び第2受信データの第2データ値に対応した論理を備える判別信号を発生するタイミング判別器と、第1受信データのサンプリング時刻及び第1データ値と、第2受信データのサンプリング時刻及び第2データ値とから補間計算により求めらる、第1ゼロクロス時刻とクロックとの位相関係に関する第1位相情報を抽出する第1ゼロクロス抽出器と、第1データ値及び第1受信データのサンプリング時刻に基づいて、単位時間当たりのデータ値の増分を用いて求められた、第2ゼロクロス時刻とクロックとの位相関係に関する第2位相情報を抽出する第2ゼロクロス抽出器と、判別信号の論理に対応して、第1位相情報又は第2位相情報の内の一方を選択するセレクタと、を備える位相比較器。

(もっと読む)

時間デジタル変換器

【課題】時間遅延量の最適値制御が行える時間デジタル変換器を提供すること。

【解決手段】入力されるクロック信号を多段に遅延する複数の遅延段を有し、該複数の遅延段の少なくとも1つが可変遅延段である遅延回路と、前記遅延回路の遅延段と同数個設けられ、参照信号の入力に応答して並列に対応する遅延段の出力を取り込む複数のフリップフロップと、前記複数のフリップフロップの各出力の立ち上がりと立ち下がりの一方または両方を検出するエッジ検出回路と、前記エッジ検出回路が検出したエッジ数をカウントするカウンタ回路と、前記カウンタ回路がカウントしたエッジ数に応じて前記可変遅延段の遅延量を制御する制御回路とを備える。

(もっと読む)

遅延回路

【課題】矩形波を入力される遅延回路において、入力信号にノイズパルスが存在すると、出力信号のジッターが生じる。

【解決手段】シュミットコンパレータ102からの出力信号VdoでスイッチSW3を制御し、コンデンサCstへの充電電流を供給する電流源I1と、放電電流を供給する電流源I2とのいずれかを選択する。入力信号VdiでスイッチSW1,SW2を制御することで、選択された電流源からの電流供給がオン/オフされる。シュミットコンパレータ102はコンデンサCstの電圧Vstに応じてVdoを切り替える。Vdiの立ち上がり時には、VdiのHレベル期間にてコンデンサCstへ充電電流を供給し、Vdiの立ち下がり時には、VdiのLレベル期間にてコンデンサCstへ放電電流を供給する。

(もっと読む)

信号発生装置

【課題】

積分回路や発振回路に、時間差なく各信号が入力され、さらには、積分回路や発振回路の補正や校正の自由度を高くする。

【解決手段】

複数のアナログ信号を入力し当該アナログ信号をそれぞれ積分した積分信号をそれぞれ出力する積分回路111,112と、各積分信号をそれぞれ入力し、積分信号の大きさを所定のしきい値と比較して比較信号をそれぞれ出力する比較回路121,122と、積分回路のうち少なくとも2つの積分回路の制御端子に接続され、それぞれセットされた時間だけ、他の少なくとも1つの積分回路の積分動作の開始タイミングと異なるタイミングで積分動作を開始させる遅延回路131,132と、比較信号を入力し、これらの入力信号の入力タイミングを比較し、これらの入力タイミングに応じた比較結果信号を出力する信号処理回路14とを備える。

(もっと読む)

時間差に関するデータを評価する装置及び方法、並びにディレイラインを較正する装置及び方法

2つの事象の時間差に関するデータを評価する装置は、複数の段(101、102、103、104)を有するディレイライン100を含む。各段は第1部分の第1遅延と第2部分の第2遅延との遅延差を有する。この遅延差を各段の位相アービタ(105)が測定して、2つの事象のうちの第1部分の第1事象が第2部分の第2事象より先か後かを示す指示信号を出力する。合計値(201)を得るために、複数の段の指示信号を合計する合計デバイス(200)を備える。合計値は時間差の評価を示す。 (もっと読む)

位相同期ループ回路の制御方法及び位相同期ループ回路

【課題】ロックアップ時間を短縮すること。

【解決手段】PLL回路20の位相比較器23は、基準信号frと比較信号fpの位相を比較し、両信号fr,fpの位相差に応じた信号を出力する。ループフィルタ25は強誘電体容量C1を含み、位相比較器23の出力信号に応じたチャージポンプ24から出力される位相差電流IPにより直流電圧を生成するとともに、その直流電圧を平滑化して制御電圧VCを生成する。VCO26は、制御電圧VCに応じた周波数の出力信号foを生成する。カウンタ31は、入力信号fiをカウントし、カウント値と第1の設定値,第2の設定値とを比較し、第1の期間、強誘電体容量C1を高電位電源VDDの電源線に接続し、第2の期間、強誘電体容量C1と低電位電源VSSの電源線を接続する。

(もっと読む)

半導体集積回路装置

【課題】遅延を有する論理回路から検出した信号を直接利用して、その論理回路の電源電圧の制御を行うような機構が求められている。

【解決手段】本発明は、本発明は、論理回路と、前記論理回路の遅延の変化に応じた周波数の検出信号を出力する遅延特性検出回路と、前記検出信号に応じて抵抗値が変化する抵抗素子と、前記抵抗素子の抵抗値の変化に応じて参照電圧を出力する参照電圧生成回路と、前記参照電圧を前記論理回路及び遅延特性検出回路に出力する電圧供給回路とを有する半導体集積回路装置である。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号が入力される端子とVCXO109の入力端子との接続を制御し、異常信号によって接続をオンにするスイッチとを有するタイミングリカバリー回路である。

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

アナログ信号比較器

【課題】アナログ信号の値を、比較的簡易な回路でかつ短時間で、所定の値と比較する。

【解決手段】所定時間経過後にしきい値を超える基準信号を生成する波形生成回路51Aと、アナログ信号を入力し当該アナログ信号を積分してアナログ積分信号を出力する積分回路52と、前記波形生成回路51Aからの基準信号と、前記積分回路52からのアナログ積分信号とを入力し、前記波形生成回路51Aからの基準信号が所定値に達するまでの時間と積分回路52からのアナログ積分信号が所定値に達するまでの時間とを比較する比較回路と、を備えたことを特徴とするアナログ信号比較器。

(もっと読む)

電圧制御発振器を内蔵したPLL(PhaseLockedLoop)回路の位相差検出回路

【課題】低電圧動作時においても、VCO信号と基準信号との位相差を検知し、その位相差に対応したデジタル信号を生成する位相比較器を提供する。

【解決手段】基準信号と対象信号との位相差をデジタル信号として出力する位相比較器において、前記位相差に対応したパルス幅の信号により第1容量素子を充電することによって前記位相差を電荷として検出する第1検出手段と、前記基準信号の周期に対応したパルス幅の信号により第2容量素子を充電することによって基準となる時間差を基準電荷として検出する第2検出手段と、前記第1検出手段により検出された電荷と前記第2検出手段により検出された電荷とを比較する電荷比較手段と、前記電荷比較手段による比較結果により、前記第2容量素子に充電された電荷に対する前記第1容量素子に充電された電荷の比をデジタル信号として出力する出力手段と、を備える。

(もっと読む)

周波数/位相比較器

【課題】フルレートとハーフレートの両方に対応して、周波数比較モードおよび位相比較モードで正常動作を行うことのできる周波数/位相比較器を得る

【解決手段】フルレートおよびハーフレートのどちらに対してもクロック信号の振幅値をアナログホールド出力するアナログホールド位相比較部10と、フルレートの場合に1/4周期遅れのクロック信号の振幅をデジタルホールド出力し、ハーフレートの場合に1/8周期遅れのクロック信号の振幅をデジタルホールド出力するデジタルホールド位相比較部20、30と、アナログホールド値とデジタルホールド値に基づいて、入力データ信号とクロック信号の周波数比較を行う周波数比較手段50と、デジタルホールド値の極性に応じて、アナログホールド位相比較部10からの出力値と周波数比較手段50からの出力値を選択出力する最終出力信号選択手段60とを備える。

(もっと読む)

主にデジタルな時間基準発生器を使用する信号完全性測定のシステム及び方法

1以上の被テスト信号のサンプリングを制御するための、独自の時間基準発生技法を利用する信号完全性測定のシステム及び方法である。本開示に従い作成した時間基準発生器は、位相フィルタ及び変調回路を備えており、これらは、シグマデルタ変調器の出力の関数として、高速に変化する位相信号を発生させるものである。この位相フィルタは、該高速に変化する位相信号から所望でない高い周波数の位相成分をフィルタする。フィルタされた該信号は、1以上のサンプラをクロックするために使用され、それによって上記の被テスト信号のサンプリングの事例を生成する。次に、これらサンプリングの事例を、被テスト信号の種類に適した何らかの1以上の様々な技法を使用して分析する。 (もっと読む)

位相調整回路装置及びタイミング調整回路システム

【課題】 所定の入力信号または出力信号について製造バラツキや電源電圧や温度変化の影響を少なくし、適切なタイミングでの動作を実現する位相調整回路装置を提供する。

【解決手段】 2つの入力クロック信号の位相差に応じた電圧の位相差検出信号を出力する位相比較回路2と位相差検出信号Sfの電圧値に応じた周波数で発振する基準クロック信号C0を出力する電圧制御発振回路3を有する位相同期回路8、位相の異なる複数のクロック信号C6の1つを選択して位相調整用の参照クロック信号C3として出力する位相選択回路4、及び、第1入力クロック信号C1の信号レベルの変化タイミングを参照クロック信号C3の立ち上がりまたは立ち下がりタイミングに合わせる位相調整を行うフリップフロップ回路5を備え、位相調整後の第1入力クロック信号C4と基準クロック信号C0が外部回路を経由して得られる遅延クロック信号C2を位相比較回路2に入力する。

(もっと読む)

遅延素子の遅延寄与決定を有する時間−デジタル変換

【課題】本発明は、時間−デジタル変換に対応する方法に関する。

【解決手段】遅延素子(126.1、...、126.N)の少なくとも1つのチェーンを備える時間−デジタル変換器(110)であって、前記遅延素子(126.1、...、126.N)のチェーンのステータスが変換する時間間隔に関連するデジタル信号を表し、前記時間−デジタル変換器(110)が、遅延素子(126.1、...、126.N)の中で転送されるパルスを基準にして統計的に等しく分散された可変位置を有するトリガ信号(154)を供給する手段(156)であり、前記較正トリガ信号(154)に応じて遅延素子(126.1、...、126.N)の前記チェーンのステータスを捕捉する手段(130)であって、前記ステータスは前記遅延素子(126.1、...、126.N)の遅延時間によって決まり、前記較正トリガ信号(154)に応じて、パルス位置の発生に基づく前記遅延素子(126.1、...、126.N)の全遅延に対する少なくとも幾つかの前記遅延素子(126.1、...、126.N)の実寄与を決定する手段と、前記時間間隔を前記デジタル信号(168)に変換する際に、少なくとも幾つかの前記遅延素子(126.1、...、126.N)の前記実寄与を考慮する手段(164)とを備えることを特徴とする時間−デジタル変換器(110)。

(もっと読む)

1 - 20 / 23

[ Back to top ]