Fターム[5J039JJ12]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 主たる比較部 (286) | 二安定素子によるもの (109) | RS−FF (11)

Fターム[5J039JJ12]に分類される特許

1 - 11 / 11

位相調整回路及び位相調整方法

【課題】LSIチップ面積の増大を抑制しつつ、製造ばらつきや使用条件の影響を受けない安定的な位相調整を実現する

【解決手段】入力クロックと出力クロックの位相差を調整する位相調整回路を以下のように構成する。その位相調整回路は、出力クロックに遅延を付加するクロック遅延回路と、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスを入力として受け、パルス除去幅設定値によって遅延素子の段数を変化させて、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスの幅を検出する位相差検出回路とを有することが好ましい。そして、位相差検出回路で検出した入力クロックと出力クロックの位相差が入力クロックに対して目標の位相差になるようにクロック遅延回路にて出力クロックに遅延を付加する。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

半導体集積回路

【課題】PLL(Phase Locked Loop)回路を搭載した半導体集積回路において、当該PLL回路の発振安定待ちの時間を有効利用する。

【解決手段】実動作準備期間中に、PLL回路50の帰還ループを遮断した状態で位相比較器51の参照クロック入力部Fpと帰還クロック入力部Frとの双方に基準クロック100を供給して、位相比較器51における位相差の検出不感帯が小さくなるように当該位相比較器51内のリセット信号の遅延を調整する。

(もっと読む)

デジタル型ヘリウム−ネオン安定化レーザ

【目的】 安定化のために、デジタル量を用いる安定化ヘリウム−ネオンレーザの高度の安定度をうるため、デジタルのパルスの形状を正確に揃える手段の提供を行なうと共に、前記安定化のためのデジタル量のパルスの周波数を正確に一定にする手段の提供を行なうことを目的とする。

【構成】

レーザから安定化のために使用出来るデジタル量のパルス周波数を、基準周波数を完全に、しかも安定に一致させるため、ダイオードの順方向の電圧を利用して、正負のパルスの基線を零ボルトにし、さらに、このデジタル量をアナログ量に変換する際、F/V変換回路と正負のパルスの電荷をゆっくり積分する回路を並列にして誤差信号の値を完全に零にしている。

(もっと読む)

半導体装置の二重基準入力受信器及びその入力データ信号の受信方法

【課題】半導体装置の二重基準入力受信器及びその入力データ信号の受信方法を提供する。

【解決手段】第1及び第2入力バッファと位相検出器とを備える入力受信器であって、第1入力バッファは、クロック信号によって同期して、イネーブルまたはディセーブルされ、ポジティブ入力端子に入力される入力データ信号とネガティブ入力端子に入力される第1基準電圧との電圧差を感知して増幅し、第2入力バッファは、クロック信号によって同期して、イネーブルまたはディセーブルされ、ポジティブ入力端子に入力される第2基準電圧とネガティブ入力端子に入力される入力データ信号との電圧差を感知して増幅する。第1基準電圧のレベルは、入力データ信号のレベルの中間レベルより高く、第2基準電圧のレベルは、入力データ信号のレベルの中間レベルより低い。位相検出器は、第1入力バッファの出力信号と第2入力バッファの出力信号との位相差を検出し、検出された位相差に対応する出力信号を発生させる。

(もっと読む)

比較器

【課題】小面積で計算速度が速い比較器を提供する。

【解決手段】比較器は、各々の入力端にクロック信号が共通して入力される第1及び第2遅延回路と各々の第1入力端に第1遅延回路の出力信号及び第2遅延端の出力信号が各々入力される第1及び第2論理ゲートを含む第1ラッチ回路、及び第1論理ゲートの出力端から出力される信号及び前記第2論理ゲートの出力端から出力される信号をラッチする第2ラッチ回路を備える。第1遅延回路の遅延時間は外部から入力される第1デジタル信号により制御される可変の遅延時間であり、前記第2遅延回路の遅延時間は外部から入力される第2デジタル信号により制御される可変の遅延時間である。

(もっと読む)

遅延同期ループ及びこれを具備した半導体メモリー装置

【課題】 互いに異なる位相を有した複数個のクロック信号を発生することができる遅延同期ループを提供する。

【解決手段】 クロック信号とフィードバッククロック信号との位相差を検出し、前記位相差によって変化する複数ビットの遅延制御信号を発生する位相検出器12と、前記複数ビットの遅延制御信号に応答して前記クロック信号を遅延させて複数個の出力クロック信号及び前記フィードバッククロック信号を発生する所定個数の縦続接続された第1の遅延セルを具備する第1の遅延器18と、前記複数個の遅延制御信号に応答して反転クロック信号を遅延させて複数個の反転出力クロック信号を発生する所定個数の縦続接続された第2の遅延セルを具備する第2の遅延器22と、前記複数個の出力クロック信号及び前記複数個の反転出力クロック信号の中で関連があるクロック信号を位相混合して補正された複数個の出力クロック信号を発生する位相混合器24とを含む。

(もっと読む)

可変遅延回路及び半導体集積回路装置

【課題】 高い精度で遅延時間を制御できる可変遅延回路を用いた半導体集積回路装置を提供することを目的とする。

【解決手段】入力クロック信号を遅延させる第1のDLL回路3と、第1のDLL回路よりも高い精度で遅延を制御できる第2のDLL回路10とを有し、第1及び第2のDLL回路の位相比較(31、14)を独立に動作させ、かつ第2のDLL回路の遅延量制御を第1のDLL回路の動作に従属させることで、入力クロック信号に対し所定の位相関係を有する出力クロック信号を出力するように第1及び第2のDLL回路で遅延を与える半導体集積回路装置。

(もっと読む)

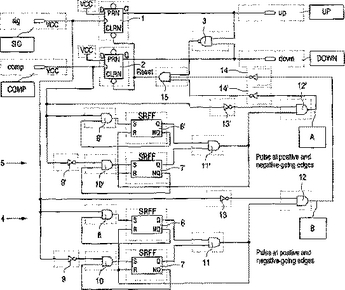

位相比較器

とりわけ、PLLモジュールに対する位相比較器は、入力信号の位相角をそれら入力信号のエッジを評価することで比較し、調節信号を生成する。この調節信号を入力信号についての崩壊或いは干渉に対して強くするために、これら入力信号(SIG、COMP)の更なる異なるエッジを評価し、これらから調節信号(UP、DOWN)に対する追加のリセット信号を生成するための追加の回路(4、5)が提供される。  (もっと読む)

(もっと読む)

1 - 11 / 11

[ Back to top ]