Fターム[5J042CA27]の内容

Fターム[5J042CA27]に分類される特許

1 - 20 / 187

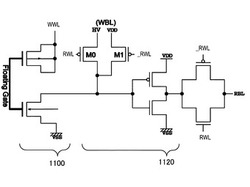

半導体装置

【課題】外部からの回路構成情報の呼び出し処理を不要にして、電源投入後すぐに動作できる半導体装置を提供する。

【解決手段】半導体装置は、ワード線とデータ線とが交差する位置にそれぞれ配置された複数の不揮発メモリセル1100を有する。不揮発メモリセル1100の出力にはインバータ回路が接続され、さらに不揮発メモリセルの出力とWBL(Write Bit Line)との間に第1トランジスタM1と、第1トランジスタよりも抵抗が低い第2トランジスタM2とを備える。インバータ回路の出力とRBL(Read Bit Line)との間にはトランスファーゲートを備える。

(もっと読む)

ニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器

【課題】回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器を提供すること。

【解決手段】本発明の一実施形態によると、第1のCMOS回路と、共通するローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに並列に接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源遮断後の起動時間が短く、高集積化及び低消費電力化を図ることが可能であるプログラマブルロジックデバイスを提供する。

【解決手段】入出力ブロックと、論理エレメントを有する複数の論理ブロックと、該複数の論理ブロックを接続する配線とを有するプログラマブルロジックデバイスにおいて、論理エレメントは、コンフィギュレーションデータが保持されたコンフィギュレーションメモリ及び選択回路を有するルックアップテーブルを有する。また、コンフィギュレーションメモリは、酸化物半導体膜をチャネル領域に有するトランジスタと、該トランジスタ及び選択回路の間に設けられた演算回路とを有するメモリ素子を複数有し、入力信号に応じて選択回路によりコンフィギュレーションデータを選択的に切り替えて出力する。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

半導体装置

【課題】電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なプログラマブルなアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルを複数並列に接続されたプログラマブル回路とし、ユニットセル毎に導通または非導通の切り替えを行う。また、当該ユニットセルのスイッチとして、オフ電流を十分に小さくすることができる第1のトランジスタと、ゲート電極が第1のトランジスタのソース電極又はドレイン電極と電気的に接続された第2のトランジスタと、を含む構成とし、当該第2のトランジスタのゲート電位によってユニットセルの導通または非導通を制御する。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電位の供給が遮断されたときでもコンフィギュレーションデータの保持が可能で、電源投入後のプログラマブルスイッチの起動時間が短い、低消費電力化が可能なプログラマブルロジックデバイスを提供すること。

【解決手段】各論理ブロック間の配線接続を制御するプログラマブルスイッチのメモリ部のトランジスタに、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドバンドギャップ半導体である酸化物半導体材料を用いて当該トランジスタを構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、電源電位の供給が遮断されたときでもコンフィギュレーションデータを保持することが可能となる。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電位の供給が遮断されたときでもコンフィギュレーションデータの保持が可能で、電源投入後の論理ブロックの起動時間が短い、低消費電力化が可能なプログラマブルロジックデバイスを提供すること。

【解決手段】プログラマブルスイッチのメモリ部のトランジスタに、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドバンドギャップ半導体である酸化物半導体材料を用いて当該トランジスタを構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、電源電位の供給が遮断されたときでもコンフィギュレーションデータを保持することが可能となる。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

スピン・トランスファ・トルク磁気抵抗デバイスを用いるソフトウェア・プログラマブル・論理

【課題】スピン・トランスファ・トルク磁気抵抗ランダムアクセスメモリ技術を用いるソフトウェア・プログラマブル・論理のためのシステム,回路および方法を提供する。

【解決手段】磁気トンネル接合(MTJ)素子と、MTJ素子に結合されるプログラマブル・ソースと、書込み及び読出し部を備え、前期読出し部は、書込み動作の間中、高インピーダンス状態に設定されるように構成されるMUXドライバを具備し、前記MTJ素子の第一グループを入力プレーンに配列し、第二グループを出力プレーンに配列し、入力プレーンおよび出力プレーンを、各々のMTJデバイスの自由層の相対的な極性に基づいた論理関数を形成するために組み合わせられるプログラマブル・論理アレイを提供する。

(もっと読む)

プログラマブル論理の特定用途向け集積回路等価物および関連の方法

【課題】FPGAのASIC等価物をより効率的、経済的に提供すること。

【解決手段】FPGAのASIC等価物の提供は、複数のいわゆるハイブリッド論理素子(HLE)を含むASICアーキテクチャを使用することによって、促進され、より効率的、経済的に実行される。各HLEは、FPGA論理素子(LE)の完全機能の一部を提供可能である。ユーザの論理設計を実装する各FPGA LEの機能は、ユーザの論理を再合成することなく単一または複数のHLEへとマッピング可能である。必要な数のHLEだけが、各LEの関数を実行するために使用される。LE間および(1)単一のHLEまたは(2)HLE群間の1対1の等価性によって、FPGA設計とASIC設計との間のいずれの方向においてもマッピングが(再合成することなく)促進される。

(もっと読む)

非同期式回路

【課題】2相式の非同期式回路の処理速度を向上させると共に、回路規模の増大を抑制する。

【解決手段】非同期式回路200は、段階的に接続された複数の回路ブロックを備え、夫々の回路ブロックが、演算回路と、該演算回路に対して2相式制御を行う制御回路を有する。モード制御回路230は、1段目の回路ブロックに対して、該回路ブロックが休止相を開始したときに初期化を開始し、最下段の回路ブロックが休止相を開始したときに稼働相を開始し、2段目の回路ブロックに対して、1段目の回路ブロックが初期化を開始したときに稼働相を開始し、1段目の回路ブロックが稼働相を開始したときに初期化を開始するように制御を行う。

(もっと読む)

プログラマブルロジック集積回路デバイスの相互接続ならびに入力/出力リソース

【課題】プログラマブルロジックデバイスに適用してプログラマブルロジックアレー集積回路デバイスの動作速度を増加するための相互接続リソースの提供。

【解決手段】プログラマブルロジック集積回路(10)は、交差する複数の領域の行および列からなる配列をもって、デバイス上に配置された複数のプログラマブルロジック領域(20)を有する。領域から領域へおよび/または領域間におけるプログラム可能な相互接続を形成するための相互接続リソース(例えば、相互接続コンダクタ等)が設けられ、これらのうちの少なくともいくつかは、構造的には類似であるが著しく異なる信号伝送速度特性を有する2つの形式で構成される。例えば、これらの双対形式相互接続リソースのうちの主要なまたは大きな部分(200a,210a,230a)はノーマル速度と呼ばれるものであり、少ないほうの部分(200b,210b,230b)は大幅に高速な信号速度を有する。

(もっと読む)

論理回路、該論理回路を含む集積回路及び該集積回路の動作方法

【課題】論理回路、該論理回路を含む集積回路及び該集積回路の動作方法を提供する。

【解決手段】入力信号の電圧及び電流のうち少なくともいずれか一つによって変更される抵抗レベルを有し、抵抗レベルを記憶する少なくとも1つの可変抵抗素子を含み、少なくとも1つの可変抵抗素子に記憶された抵抗レベルに対応するマルチレベル・データをラッチする論理回路である。

(もっと読む)

半導体装置

【課題】耐タンパ性を有する、可変論理機能を実現するための記憶回路を有する半導体装置を提供する。

【解決手段】制御回路24は、記憶回路23の次の読出しアドレスを先に記憶回路23から読出した制御フィールドの情報または外部イベント入力に基づいて自律的に制御することが可能である。正規デコーダ28は、制御回路24から出力されるアドレスをデコードし、デコード結果に基づいて、データフィールドの少なくとも1つの正規メモリセルと、制御フィールドの少なくとも1つのメモリセルを選択する。冗長制御回路51は、イネーブル信号が活性化された場合に限り、制御回路24から出力されるアドレスと、所定の正規メモリセルのアドレスとが一致したときに、正規デコーダ28による選択を禁止し、データフィールドの少なくとも1つの冗長メモリセルと制御フィールドの少なくとも1つの冗長メモリセルを選択する。

(もっと読む)

プログラマブル論理の特定用途向け集積回路等価物および関連の方法

【課題】FPGAのASIC等価物をより効率的、経済的に提供する。

【解決手段】FPGAのASIC等価物の提供は、複数のいわゆるハイブリッド論理素子

(HLE)を含むASICアーキテクチャを使用することによって、促進され、より効率

的、経済的に実行される。各HLEは、FPGA論理素子(LE)の完全機能の一部を提

供可能である。ユーザの論理設計を実装する各FPGA LEの機能は、ユーザの論理を

再合成することなく単一または複数のHLEへとマッピング可能である。必要な数のHL

Eだけが、各LEの関数を実行するために使用される。LE間および(1)単一のHLE

または(2)HLE群間の1対1の等価性によって、FPGA設計とASIC設計との間

のいずれの方向においてもマッピングが(再合成することなく)促進される。

(もっと読む)

論理否定型電子回路

【課題】 ブートストラップ機能を有する電子回路に関し、出力電圧の降下を防止して、論理否定型電子回路の誤作動を阻止し、また、長い作動時間を確保する。

【解決手段】 負荷トランジスタ、駆動トランジスタ部、充電用トランジスタ並びにブートストラップ容量を具備し、入力電圧の位相を出力部から反転せしめて出力する論理否定型電子回路について、前記充電用トランジスタのソース−ドレイン間の電圧が電源の電圧Vddと同値の電圧であるときに、これらソース−ドレイン間を流れる電流が1×10−9A以下となる範囲の電圧をこの充電用トランジスタのゲートに印加する定電圧印加手段を接続する。

(もっと読む)

ルックアップテーブル回路およびフィールドプログラマブルゲートアレイ

【課題】動作速度の速いルックアップテーブル回路およびフィールドプログラマブルゲートアレイを提供する。

【解決手段】ルックアップテーブル回路1は、入力信号に基づいて複数の抵抗変化型素子の中から一つの抵抗変化型素子を選択する抵抗変化回路2と、抵抗変化回路2の最大抵抗値と最小抵抗値との間の抵抗値を有する参照回路4と、抵抗変化回路2の他端にソースが接続された第1のnチャネルMOSFET6と、参照回路の他端にソースが接続された第2のnチャネルMOSFET8と、第1のnチャネルMOSFET6のドレインを通して抵抗変化回路2に電流を供給する第1の電流供給回路10と、第2のnチャネルMOSFET8のドレインを通して参照回路4に電流を供給する第2の電流供給回路12と、第1のnチャネルMOSFET6のドレイン電位と第2のnチャネルMOSFET8のドレイン電位を比較する比較器14と、を備える。

(もっと読む)

同期ラッチング機能を持つ多値論理手段と多値ハザード除去手段

【課題】同期ラッチング機能を持つ多値論理手段を提供する。

【解決手段】トランジスタ1、2、17と抵抗20、21等が構成する判別手段、この判別結果信号に基づき動作する、トランジスタ41、37、ダイオード39及び抵抗15が構成するオン・オフ駆動手段及び、このオン・オフ駆動手段がオン・オフ駆動する、トランジスタ3、4が構成する双方向性プル・スイッチング手段が新・多値論理フージ(Hooji)代数を実現した多値論理回路を構成する。前記判別手段と前記オン・オフ駆動手段の間でやり取りする信号は2値信号と同様な為、その間に2値同期型フリップ・フロップ手段として同期信号発生手段60、トランジスタ61及び抵抗26、28が構成する同期信号供給手段が供給する同期信号に基づき動作するD型フリップ・フロップ27を挿入・接続する。

(もっと読む)

1 - 20 / 187

[ Back to top ]