Fターム[5J055DX56]の内容

Fターム[5J055DX56]の下位に属するFターム

DEPP (5)

Fターム[5J055DX56]に分類される特許

581 - 596 / 596

半導体装置

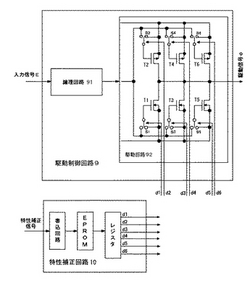

【課題】 半導体スイッチング素子のコレクタ電流の立ち上がりおよび立下り時における電流変化の傾きを変化できないため、ノイズ発生およびスイッチング損失を最適に設定できない。

【解決手段】 半導体スイッチング素子と、入力信号に基づきこの半導体スイッチング素子の駆動制御を行う駆動制御手段(9)とからなる半導体装置において、前記駆動制御手段(9)に、駆動能力の異なる複数個の駆動デバイス(T1〜T6)を備え、その駆動デバイスの中からいずれか1つ、もしくは複数個を選択して用いることにより、半導体スイッチング素子の動作特性を補正する特性補正手段(10)を備える。

(もっと読む)

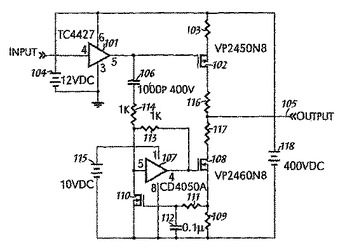

電力MOSトランジスタのゲート駆動回路

ゲートコントローラより高い電源電圧を使用する電力MOSトランジスタのゲート駆動回路が開示される。上記ゲート駆動回路は,ゲートコントローラの出力信号を,ゲートコントローラの電源電圧に対してより高い電源電圧を使用する電力MOSトランジスタに伝達する際,ゲートコントローラの出力信号をデューティサイクルおよび周波数に拘わらず,安定に,かつ,效率的に伝達できる。従って,上記ゲート駆動回路は,ゲートコントローラ出力信号のデューティサイクルの変化が大きい場合,また,スイッチング周波数が一定でない場合にも適している。  (もっと読む)

(もっと読む)

リセット回路

【課題】 パワーダウン時のパワーダウンリセット信号のタイミング制御を容易にし、繰り返し電源をオン/オフした時の起動不良を防ぐことを課題とする。

【解決手段】 リセット回路は、電源検出回路とパワーダウン検出回路と出力回路とを有する。電源検出回路は、パワーオン及びパワーダウン時に電源電圧(VDD)に応じた第1の電圧が第1のしきい値より大きいと第1の信号を出力し、低いと第2の信号を出力する。パワーダウン検出回路は、パワーダウン時に第2の信号が出力された後、電源電圧(VDD)に応じた第2の電圧が第2のしきい値より小さくなると第3の信号を出力する。出力回路は、パワーオン時に第1の信号が出力されるとローレベルからハイレベルに変化するパワーオンリセット信号(POR)を出力し、パワーダウン時に第3の信号が出力されるとハイレベルからローレベルに変化するパワーダウンリセット信号(POR)を出力する。

(もっと読む)

低電力高性能記憶回路及び関連方法

第1NMOSトランジスタ、第1PMOSトランジスタ、第2NMOSトランジスタ、第2PMOSトランジスタ、第2PMOSの第1ソース/ドレインに接続された第1バイアス電圧ノード、第1PMOSトランジスタのゲートに接続された第3バイアス電圧ノード、第1PMOSトランジスタのゲートに接続された第4バイアス電圧ノード、第1NMOSトランジスタの第2ソース/ドレインを第1PMOSトランジスタの第1ソース/ドレインに接続するプルアップノード、第2PMOSトランジスタの第2ソース/ドレインを第2NMOSトランジスタの第1ソース/ドレインに接続するプルダウンノード、入力ノード、第1PMOSトランジスタの第2ソース/ドレインを第2NMOSトランジスタの第2ソース/ドレインに接続する記憶ノード、出力ノード、入力データ値を入力ノードから第1NMOSトランジスタのゲートと第2PMOSトランジスタのゲートに制御可能に伝達するべく接続された入力スイッチ、及び保存されているデータ値を記憶ノードから出力ノードに制御可能に伝達するべく接続された出力スイッチを有する集積回路である。  (もっと読む)

(もっと読む)

MOSFET駆動回路、プログラマブル電源及び半導体試験装置

半導体試験装置に使用されるプログラマブル電源において、電流レンジや出力リレーにおける大電流の高速切り換えを可能とする。

半導体試験装置1のプログラマブル電源10に設けられたスイッチ部20のMOSFET駆動回路22において、光絶縁素子22−1の受光部22−12からの電流によりコンデンサ部22−12に電荷が蓄積される。アナログスイッチ部22−3の切り換えによりSWAがON(SWBがOFF)となると、コンデンサ部22−12に蓄積されていた電荷によりMOSFET部21の各MOSFETのゲートがチャージされON状態となる。一方、アナログスイッチ部22−3のSWBがON(SWAがOFF)となると、MOSFETのゲートがディスチャージされる。

(もっと読む)

(もっと読む)

高く、かつ広い作動電圧レンジのためのバイアス回路を備えるゲートドライバー出力ステージ

【課題】ICデバイスの通常の最大電圧定格よりも高い電圧において、より広い電圧レンジで作動できるゲートドライバーを提供する。

【解決手段】 簡単で、低コストのゲートドライバー、およびバイアス回路は、NMOSトランジスタおよびPMOSトランジスタのような構成部品の通常の部品のブレークダウン電圧を超える、より広い作動電圧レンジを可能にしている。回路を実現するために、バルクおよびPタイプの基板として、エピタキシャル層を備えるCMOSプロセスを使用する。

(もっと読む)

リーク電流低減方法

データ保持モードのために回路をパワー・ダウンする方法は、電源電圧ノードを能動状態の電源電圧レベルから非能動状態の電源レベルに変更する工程と、Pチャネル・デバイスのソースを電源電圧ノードに接続する工程と、Pチャネル・デバイスのバック・ゲートに保持用電源電圧レベルを供給する工程と、Pチャネル・デバイスのドレイン電圧を保持用電源電圧レベルとは異なる基準電圧レベルに変更する工程と、Pチャネル・デバイスのゲート電圧を基準電圧レベルに変更する工程とを含む。  (もっと読む)

(もっと読む)

インバータ回路とこれを用いた圧電発振器

【課題】CMOSインバータの貫通電流は、このインバータを用いた装置の電力消費量を増大させ、特に携帯機器においては電池の寿命を短くする。

【解決手段】従来のCMOSインバータと同じ回路のP-MOSTQ1のソースS回路に、別のP-MOSTQ3を直列に追加接続し、そのゲートと回路の入力端間を遅延回路Z1で接続し、また、前記CMOSインバータのN-MOSTQ2のソース回路に、別のN-MOSTQ4を直列に追加接続してそのゲートと回路の入力端間を遅延回路Z2で接続した回路構成にする。

(もっと読む)

ダイナミックバックゲートバイアスを伴うブートストラップダイオードエミュレータ

【解決手段】ハーフブリッジスイッチング回路で使用するためのブートストラップダイオードエミュレータ回路が提供される。スイッチング回路は、負荷ノードにおいてトーテムポール構造の形で互いに繋がれているトランジスタと、これらのトランジスタを駆動するための駆動回路と、高圧側駆動回路に電力を供給するためのブートストラップコンデンサとを含む。ブートストラップダイオードエミュレータ回路は、ゲート、バックゲート、ソース、およびドレインを有し、そのドレインを高圧側供給ノードに結合され、そのソースを低圧側供給ノードに結合されているLDMOSトランジスタと、LDMOSトランジスタのゲートに電気的に結合されているゲート制御回路と、LDMOSトランジスタのバックゲートに電気的に結合されているダイナミックバックゲートバイアス回路とを備える。ダイナミックバックゲートバイアス回路は、LDMOSがオンにされたときに、LDMOSトランジスタのドレインの電圧に近いけれども同電圧よりも僅かに低い電圧をLDMOSトランジスタのバックゲートに印加することによって、LDMOSトランジスタのバックゲートを動的にバイアスするように動作可能である。 (もっと読む)

フェイルセイフな方法で誘導負荷を遮断するための装置および方法

【課題】誘導負荷54の遮断時の誘導電圧の大きさを監視することにより、誘導負荷54をフェイルセイフな方法で遮断する。

【解決手段】入力側の遮断信号20,22または24を受信すれば少なくとも1つのスイッチング素子26により負荷54を遮断する。遮断時に負荷54において誘導電圧Uiが発生するが、この誘導電圧Uiは閾値スイッチ38,40,41,44により制限されている。閾値スイッチ38,40,42,44は、監視回路68,70により監視されており、閾値スイッチ38,40,42,44の1つが故障すれば監視回路68,70において誤差信号が発生する。

(もっと読む)

静電結合を用いた高電圧パルスドライバ

高電圧システムに共通する、高電源リプルにおいて有用である静電結合を用いた高電圧ドライバである。それは、デューティサイクルの最大範囲を許容するが、変圧器の磁気の制限はなく、または、光学式の結合方法における複雑さの増加もない。それはまた、出力駆動ラインにアークする高電圧によって作成される過渡電圧においても、強固である。本発明はまた、特に例示的ディスプレイの応用における使用のために、低コストでの静電結合の使用を再構築するが、静電結合に特有の制限はない。  (もっと読む)

(もっと読む)

信号増幅用回路、及びアクティブマトリクス装置における同回路の使用

増幅回路はキャパシタ構造(42)と切替装置とを備える。キャパシタ構造は、電圧依存性静電容量を有する第一のキャパシタ(C2)と第二のキャパシタ(C1)(これもまた電圧依存性としてよい)とを有する。同回路は2つのモードで、すなわち少なくとも第一のキャパシタの一端子に入力電圧が提供される第一のモードと、切替装置によって第一及び第二のキャパシタ同士の間で電荷の再配分が起こることにより、第一のキャパシタにかかる電圧が変化し第一のキャパシタの静電容量が減少し、出力電圧が第一のキャパシタにかかる電圧に依存する第二のモードとで、動作可能である。本発明は電圧制御静電容量をキャパシタ間の電荷共有と併せて使用するものであり、これにより、結果的に電圧増幅特性が提供される。よってこの機構は、アナログ電圧の増幅に、または固定レベル(すなわちデジタル電圧)の昇圧に利用できる。よって本発明の回路は、レベルシフトまたは増幅のために、例えばアクティブマトリクスアレイ装置のピクセルでの用途に使用できる。  (もっと読む)

(もっと読む)

トラック/ホールド回路

スイッチ(10)とキャパシタ(12)を備えるトラック/ホールド回路である。第1のブートストラップスイッチ(14a)は、その入力として、クロック信号clkin及び入力信号Vinを有する。第1のブートストラップスイッチ(14a)から出力されるクロック信号clkbootは、スイッチ(10)のゲートに印加される。第1のブートストラップスイッチ(14a)は、電流源(20)という形のレベルシフト手段及びバッファ手段(30)を介して、当該回路の入力Vinと出力Vsとの間に接続されている。第2のブートストラップスイッチ(14b)が設けられており、第2のブートストラップスイッチ(14b)は、その入力として、クロック信号clkin及び入力信号Vinを有する。第2のブートストラップスイッチ(14b)から出力される逆位相クロック信号clknbootは、スイッチ(10)のいずれかの側に接続されている2つのダミースイッチ(16)のゲートに印加される。  (もっと読む)

(もっと読む)

半導体スイッチの高周波制御

共振ゲートドライバ回路は、例えば、MOSFETの効率的なスイッチングを提供する。しかし、共振ゲートドライバ回路は、高いスイッチング周波数が必要とされる用途を可能にさせないことがしばしばある。本発明によれば、共振ゲートドライバ回路のインダクタのプリチャージングが実行される。これは、MOSFETの極めてエネルギー効率が良い高速な動作を可能にさせる。  (もっと読む)

(もっと読む)

スイッチング回路における不感時間制御

DC−DC変換器は、入力端子(37)と接地端子(38)との間に直列に接続された2つの電界効果トランジスタ(35,36)を有する。両方のトランジスタ(35,36)がオフとなるときの不感時間の調整は、トランジスタ(35,36)の一方又は双方のドレイン(39,44)及びソース(43,40)に直接かけられてケルビンフィードバック接続部(71,72,67,68)を設けることによって行い、信号ラインの抵抗及びインダクタンスを回避するようにしている。  (もっと読む)

(もっと読む)

電源回路

【課題】CMOS集積回路を用いた同期整流方式の電源回路などにおいて、電力消費の低減と、部品増や効率低下を伴うことなく負荷変動に対する高速応答が可能な電源回路を提供すること。

【解決手段】PWM信号をゲートに、VIN(=VDD)をソースに接続するPMOS(QP1)のドレインに接続され、VSSをソースに有す、NMOS(QN1)のドレインに接続される中間ノード電圧VMAが、NMOS(QN1)オン時に、アンダーシュートから戻って基準電位VSSレベルを越えたときこれを検出してNMOS(QN1)のゲート電圧をローレベル(オフ)にする。また、NMOS(QN1)オン時に、中間ノード電圧VMAが、アンダーシュートから基準電位VSSレベルに戻ったタイミング(ゼロ点位置)を検出することで、このゼロ点位置検出信号を負荷電流の大小を示す信号としてPWM回路33に帰還してPWM信号のパルス幅を制御し、負荷変化に対応させる。

(もっと読む)

581 - 596 / 596

[ Back to top ]